# Diameter Optimization of Nano-scale SiNWT Based SRAM Cell

Yasir Hashim Faculty of Engineering Technology, University Malaysia Pahang (UMP), Lebuhraya Tun Razak, 26300, Pahang, Malaysia yasirhashim@ump.edu.my Hadi bin Manap Faculty of Engineering Technology, University Malaysia Pahang (UMP), Lebuhraya Tun Razak, 26300, Pahang, Malaysia

Abstract—This paper represents diameter and logic voltage level optimizations of 6-Silicon Nanowire Transistors (SiNWT) SRAM. This study is to demonstrate diameter of nanowires effects at a different logic voltage level  $(V_{dd})$  on the static characteristics of Nano-scale SiNWT Based SRAM Cell. Noise margins (NM) and inflection voltage  $(V_{inf})$  of transfer characteristics are used as limiting factors in this optimization. Results indicate that optimization depends on both diameters of nanowires and logic voltage level  $(V_{dd})$ . And increasing of logic voltage level from 1V to 3V tends to decrease in optimized nanowires diameters but with increasing in current and power dissipation. SRAM using nanowires transistors must use logic level (2V or 2.5V) to produce SRAM with lower diameters and suitable inflection currents and then with lower power dissipation as possible.

Index Terms—Nanowire, Digital Inverter, SiNWT, CMOS, SRAM.

## I. INTRODUCTION

Static random access memory (SRAM) cell with six transistors (6T) is the primary memory used in many applications in digital circuits. As is well known, designing an integrated circuit chips that having the greatest possible number of individual 6T SRAM cells with two inverters circuits was considered a main goal of semiconductor technologies in our days, with a view to provide the integrated circuit chip with a largest memory as possible within the available area thereon. To achieve this objective, layouts for the transistors making up the cells integrated circuit have been developed by designers to reduce the area required for each. As the conventional silicon metal-oxide-semiconductor-fieldeffect transistor (MOSFET) approaches it downscaling limits, many novel transistors' structures are being extensively explored. Among them, the silicon nanowire transistor (SiNWT) has attracted broad attention from both the semiconductor industry and academic fields [1-4].

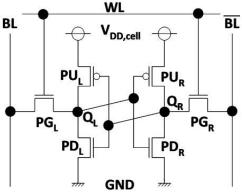

Fig. 1 shows the most commonly used SRAM bit-cell architecture that is the six MOSFET transistors (6-T) SRAM cell. It consists of two cross-coupled inverters (PMOS pull-up transistors PUL and PUR and NMOS pull-down transistors PDL and PDR) and two access transistors (NMOS pass-gate transistors PGL and PGR). When the horizontally-running word-line (WL) is enabled, the access transistors are turned on, and connect the storage nodes to the vertically-running bit-lines (BL and BL). In other words, they allow access to the

cell for read and write operations, acting as bidirectional transmission gates.

Fig. 1 circuit diagram of a Static Random Access Memory (SRAM).

#### II. METHODOLOGY

Construction of SRAM cells and its inverters using nanowires, include a number of PMOS and NMOS devices disposed on nanowires that are arranged on a wafer. Since the dimensions of nanowires effect on the operation of SRAM, it is desirable to arrange the devices such that these effects of the dimensions of nanowire are optimized.

In the present paper, a computer-based model that discussed in [5] used to produce static characteristics of SRAM cells. The MATLAB software is designed to calculate the working points of the matched curves of the output characteristic of the two nanowire transistors connected as a CMOS inverter circuit in SRAM. The MATLAB software is designed to calculate output  $(V_{out}-V_{in})$  and current  $(I_{out}-V_{in})$  characteristics of the NW-CMOS inverter depending on the  $I_d$ - $V_d$  characteristics of SiNWTs [5]. This model used MuGFET tool [6, 7] to produce NW N- and P-channel transistor output characteristics to fully simulate the NW-CMOS. These characteristics are then implemented in the MATLAB model to find the final static characteristics of the two transistors connected as a CMOS inverter circuit the main part of SRAM.

The nanowires ratio of two SiNWTs was selected to make the SRAM work in the best possible conditions. The dimension ratio (Kp/Kn) of the two transistors (where K=Diameter (D)/Length (L)) in a normal CMOS inverter is ( $\approx$ 3/1) when the width of the PMOS is increased or the length of the NMOS is decreased. The parameters in Table 1 are used

to study the effect of dimensions on the characteristics of the SRAM.

Table 1 Parameters of nanowire transistors

| Parameter Name                   | N-nanowire                                   | P-nanowire                                       |

|----------------------------------|----------------------------------------------|--------------------------------------------------|

| Channel length L                 | 30 nm                                        | 30 nm                                            |

| Source length                    | 10 nm                                        | 10 nm                                            |

| Drain length                     | 10 nm                                        | 10 nm                                            |

| Channel diameter D               | 20 nm                                        | 10, 17, 24, 30, and 37 nm                        |

| Oxide thickness SiO <sub>2</sub> | 2 nm                                         | 2 nm                                             |

| Channel concentration            | 1*10 <sup>10</sup> /cm <sup>3</sup>          | 1*10 <sup>10</sup> /cm <sup>3</sup>              |

| Source and drain concentration   | 1*10 <sup>20</sup> /cm <sup>3</sup> (n-type) | 1*10 <sup>20</sup> /cm <sup>3</sup> (p-<br>type) |

The optimization will depends strongly on increasing current ( $I_{ds}$ ) of PMOS transistor. Increasing in  $I_{ds}$  of a nanowire in the P-channel transistor tends to compensate for the lower mobility of carriers (holes) in P-channel NWs. This process tends to improve noise margins of the inverter circuit. The dimensional optimization principle depends on noise margins and the inflection voltage ( $V_{inf}$ ). These parameters are used as limitation factors. The best inverter has equal noise margin low (NM<sub>L</sub>) and noise margin high (NM<sub>H</sub>) values. Both NM<sub>L</sub> and NM<sub>H</sub> must have high values, and the  $V_{inf}$  must be close to ( $V_{dd}/2$ ) value.

### III. RESULTS AND DISCUSSIONS

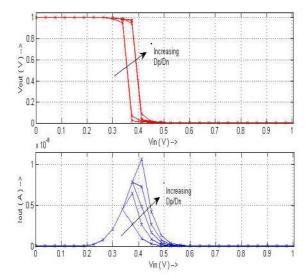

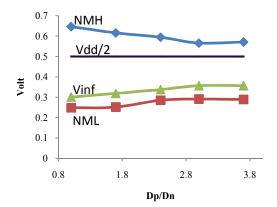

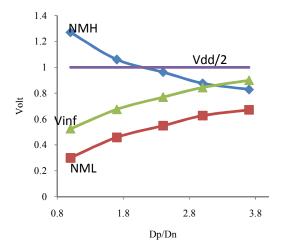

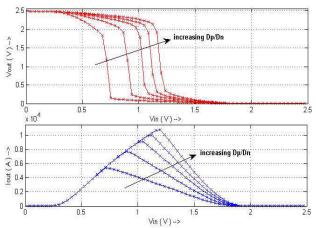

Fig 2 illustrates the shift of inflection point to the right with increasing nanowires ratio (Dp/Dn) by increasing diameter of nanowire in PMOS transistor, where ((Dp/Dn) =1, 1.7, 2.4, 3, and 3.7) at logic level voltage  $V_{dd}\!=\!1$ . According to Fig 2, increasing of  $D_p/D_n$  tends to increase in NML and decrease in NMH without reaching optimized value (0.5V). NMH and NML are the high- and low-state noise margins, respectively. In current characteristics, it is clear that the current was increased at the inflection point with increasing nanowires diameters ratio. According to Fig 3, and at  $V_{dd}\!=\!1V$  there is no optimization point where NMH and NML curves cross in it and be nearer to  $V_{dd}/2$  line with inflection voltage curve, and this figure illustrates that NML and NMH could be equal but at very high Dp/Dn ratio.

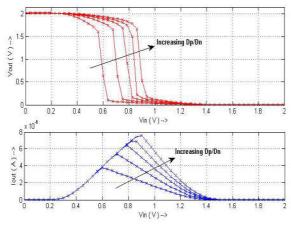

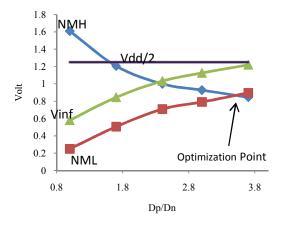

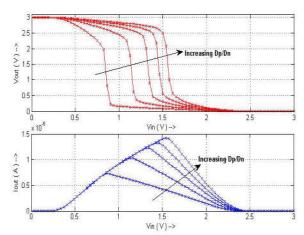

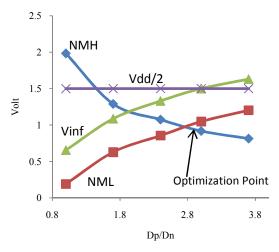

In Fig 4 the transfer characteristics of same inverters in SRAM with same dimensions in Table1 and also with same nanowires diameters ratios ((Dp/Dn) =1, 1.7, 2.4, 3, and 3.7) but with logic level voltage  $V_{dd}$ =2, this figure illustrates the shift of inflection point to the right with increasing nanowires diameters ratio (Dp/Dn) at this logic level (2V), according to Fig 4, increasing of (Dp/Dn) tends to increase in NM<sub>L</sub> and decrease in NM<sub>H</sub> and reaching optimized value (1V). In current characteristics it is clear that the current was increased at the inflection point with increasing nanowires ratio. Fig 5 shows that the crossing between NM<sub>H</sub> and NM<sub>L</sub> curves happens at Dp/Dn=4.2 which represent the optimized value for nanowires ratio. At this optimization point NM<sub>H</sub>=NM<sub>L</sub>=0.77V,  $V_{inf}$ =1V at this optimization point, which is equal to  $V_{dd}$ /2 (1 V).

Fig 2 Transfer and current characteristics with different (Dp/Dn) and  $$V_{\rm dd}\!\!=\!\!1V.$

Fig 3 NM<sub>H</sub>, NM<sub>L</sub> and  $V_{inf}$  curves with (Dp/Dn) at  $V_{dd} = 1$  V.

Fig 4 Transfer and current characteristics with different (Dp/Dn) and  $V_{dd}=2V$ .

Fig 5 NM<sub>H</sub>, NM<sub>L</sub> and  $V_{inf}$  curves with (Dp/Dn) at Vdd = 2 V.

The transfer and current characteristics of the inverters in SRAM with same dimensions in Table1 and also with same nanowires diameters ratios (( $D_p/D_n$ ) =1, 1.7, 2.4, 3, and 3.7) at  $V_{dd}\!\!=\!\!2.5$  was shown in Fig 6, this figure illustrates the shift of inflection point to the right with increasing nanowires diameters ratio ( $D_p/D_n$ ) at logic level 2.5V. According to Fig 6, increasing of ( $D_p/D_n$ ) tends to increase in NM $_L$  and decrease in NM $_H$  with start to appointing an optimized point. In current characteristics, it is clear that the current was increased at the inflection point with increasing nanowires ratio. Fig 7 shows that the crossing between NM $_H$  and NM $_L$  curves happens at Dp/Dn =3.5 which represent the optimized value for nanowires ratio. At this optimization point NM $_H$ =NM $_L$ =0.8V,  $V_{\rm inf}$ =1.15V at this optimization point, which is very close to  $V_{\rm dd}/2$  (1.25 V).

Fig 6 Transfer and current characteristics with different (Dp/Dn) and  $V_{dd}=2.5V$

Fig 7 NM<sub>H</sub>, NM<sub>L</sub> and  $V_{inf}$  curves with (Dp/Dn) at Vdd = 2.5 V.

The transfer and current characteristics of the inverters in SRAM with same dimensions in Table1 and also with same nanowires diameters ratios ((Dp/Dn) =1, 1.7, 2.4, 3, and 3.7) but with logic level voltage  $V_{dd}=3$  was shown in Fig 8, this figure illustrates the shift of inflection point to the right with increasing nanowires diameters ratio (Dp/Dn) at logic level 3V. According to Fig 8, increasing of (Dp/Dn) tends to increase in NM<sub>L</sub> and decrease in NM<sub>H</sub> with reaching (and crossing over) optimized value (1.5V). In current characteristics, it is clear that the current was increased at the inflection point with increasing nanowires ratio. Fig 9 shows that the crossing between NM<sub>H</sub> and NM<sub>L</sub> curves happens at Dp/Dn =2.6 which represent the optimized value for nanowires ratio. At this optimization point NM<sub>H</sub>=NM<sub>I</sub>=1V, V<sub>inf</sub>=1.45V at this optimization point, which is very close to  $V_{dd}/2$  (1.5 V).

Fig 8 Transfer and current characteristics with different (Dp/Dn) and  $$V_{\rm dd}\!\!=\!\!3V.$

Fig 9 NM<sub>H</sub>, NM<sub>L</sub> and  $V_{inf}$  curves with (Dp/Dn) at  $V_{dd} = 3 \text{ V}$ .

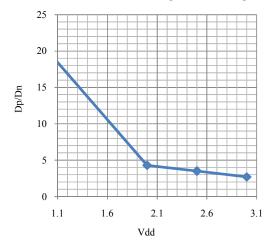

According to figure 10, optimization point will happen at lower value of nanowires diameters ratio (Dp/Dn) by increasing digital level voltage from 1V to 3V, but this also will tend to increase inflection current and power consumption in SRAM. under this fact, the fabrication of SRAM using nanowires transistors must use logic level (2V or 2.5V) to produce SRAM with lower diameters ratio and lower inflection currents and then with lower power consumption.

Fig. 10. Optimized  $D_p/D_n$  with  $V_{dd}$ .

### IV. CONCLUSION

Effect of nanowires diameter ratio of silicon nanowire transistors in SRAM cell with different  $V_{dd}$  was studded in this paper. The limiting factors of this optimization were noise margins and inflection voltage of transfer characteristics. Results indicate that optimization depends strongly on nanowires diameters ratio and  $(V_{dd})$ . And increasing of voltage from 1V to 3V tends to decrease in optimization ratio from very high nanowire ratio to 2.5, but with increasing in the current. the fabrication of SRAM using nanowires transistors must use logic level (2V or 2.5V) to produce SRAM with lower dimensions and lower inflection currents and then with lower power consumption.

#### ACKNOWLEDGMENT

This work was supported by the University Malaysia Pahang (UMP) grant [RDU150323]

#### REFERENCES

- [1] R. Huang, J. Zou, R. Wang, C. Fan, Y. Ai, J. Zhuge, Y. Wang: Experimental Demonstration of Current Mirrors Based on Silicon Nanowire Transistors for Inversion and Subthreshold Operations, IEEE Trans. on Electron Devices, Vol. 58 (2011), p. 3639.

- [2] A. Martinez, M. Aldegunde, N. Seoane, A. R. Brown, J. R. Barker, A. Asenov: Quantum-Transport Study on the Impact of Channel Length and Cross Sections on Variability Induced by Random Discrete Dopants in Narrow Gate-All-Around Silicon Nanowire Transistors, IEEE Trans. on Electron Devices, Vol. 58 (2011), p. 2209.

- [3] L. Ansari, B. Feldman, G. Fagas, J. Colinge, J. Greer: *Atomic scale simulation of a junctionless silicon nanowire transistor*, 12th Int. Conf. on Ultimate Integration on Silicon (ULIS), pp. 1-3, March (2011).

- [4] Y. Hashim, and O. Sedik: Temperature effect on IV characteristics of Si nanowire transistor, IEEE Colloquium on Humanities, Science and Engineering Research (CHUSER 2011), pp. 331-334, Dec (2011).

- [5] Y. Hashim and O. Sidek: Study and Simulation of Static Characteristics of Nanowire Inverter with Different Circuit Configurations, Int. Rev. Model. Simul. (IREMOS), Vol. 5 (2012), p. 93.

- [6] Information on https://nanohub.org/tools.

- [7] B. P. Haley, S. Lee, M. Luisier, H. Ryu, F. Saied, S. Clark, H. Bae, and G. Klimeck: Advancing nanoelectronic device modeling through peta-scale computing and deployment on nanoHUB, J. Phys. Conf. Ser., Vol. 180 (2009), p. 012075.