# DEVELOPMENT OF AUTOMATIC POWER FACTOR CORRECTION DEVICE

MOHD AZUARI BIN MUSTAPHA

UNIVERSITI MALAYSIA PAHANG

# UNIVERSITI MALAYSIA PAHANG

| BORANG PENGESAHAN STATUS TESIS <sup>*</sup><br>JUDUL: <u>DEVELOPMENT OF AUTOMATIC POWER FACTOR</u> |                                                       |                                                                                                                                                   |  |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                    |                                                       | DRRECTION DEVICE<br>PENGAJIAN:2009/ 2010                                                                                                          |  |

| Saya                                                                                               | MOHD AZU                                              | J <b>ARI BIN MUSTPHA ( 860927-29-5001)</b><br>(HURUF BESAR)                                                                                       |  |

|                                                                                                    |                                                       | rjana Muda/ <del>Sarjana</del> / <del>Doktor Falsafah</del> )* ini disimpan di<br>at kegunaan seperti berikut:                                    |  |

| 2. Po<br>3. Po<br>p                                                                                | erpustakaan dibenarkan me                             | rsiti Malaysia Pahang (UMP).<br>mbuat salinan untuk tujuan pengajian sahaja.<br>mbuat salinan tesis ini sebagai bahan pertukaran antara institusi |  |

|                                                                                                    | SULIT                                                 | (Mengandungi maklumat yang berdarjah keselamatan<br>atau kepentingan Malaysia seperti yang termaktub<br>di dalam AKTA RAHSIA RASMI 1972)          |  |

|                                                                                                    | TERHAD                                                | (Mengandungi maklumat TERHAD yang telah ditentukan<br>oleh organisasi/badan di mana penyelidikan dijalankan)                                      |  |

|                                                                                                    | √ TIDAK TERH                                          | IAD                                                                                                                                               |  |

|                                                                                                    |                                                       | Disahkan oleh:                                                                                                                                    |  |

| ,                                                                                                  | TANDATANGAN PENULIS)                                  | (TANDATANGAN PENYELIA)                                                                                                                            |  |

| <u>263, F</u><br>15100                                                                             | <u>KG SERIAN BETA,</u><br><u>KOTA BHARU,</u><br>ANTAN | MOHD REDZUAN BIN AHMAD<br>( Nama Penyelia )                                                                                                       |  |

| Tarikh                                                                                             | a: <u>23 NOVEMBER 2009</u>                            | Tarikh:                                                                                                                                           |  |

| CATATAN:                                                                                           | * Potong yang tio                                     | lak berkenaan.<br>JLIT atau TERHAD, sila lampirkan surat daripada pihak                                                                           |  |

penyelidikan, atau Laporan Projek Sarjana Muda (PSM).

"I hereby acknowledge that the scope and quality of this thesis is qualified for the award of the Bachelor Degree of Electrical Engineering (Electronics)"

| Signature | :                               |

|-----------|---------------------------------|

|           |                                 |

| Name      | : <u>MOHD REDZUAN BIN AHMAD</u> |

|           |                                 |

| Date      | : 23 NOVEMBER 2009              |

## DEVELOPMENT OF AUTOMATIC POWER FACTOR CORRECTION DEVICE

## MOHD AZUARI BIN MUSTAPHA

This thesis is submitted as partial fulfillment of the requirements for the award of the Bachelor of Electrical Engineering (Power System)

Faculty of Electrical & Electronics Engineering Universiti Malaysia Pahang

NOVEMBER, 2009

"All the trademark and copyrights use herein are property of their respective owner. References of information from other sources are quoted accordingly; otherwise the information presented in this report is solely work of the author."

| Signature | :                                 |

|-----------|-----------------------------------|

| Author    | : <u>MOHD AZUARI BIN MUSTAPHA</u> |

Date

: <u>23 NOVEMBER 2009</u>

Specially dedicated to my beloved family and those people who have guided and inspired me throughout my journey of education

### ACKNOWLEDGEMENT

First and foremost, I am very grateful to the almighty ALLAH S.W.T for letting me to finish my Final Year Project.

Here, I wish to express my sincere appreciation to my supervisor, En. Mohd Redzuan bin Ahmad for encouragement, guidance, suggestions, critics and friendship throughout finishing this project.

In particular, I wish to thank lecturers, staff and technicians, for their cooperation, indirect or directly contribution in finishing my project. My sincere appreciation also extends to all my friends who has involved and helped me in this project.

Most importantly, I wish my gratitude to my parents for their support, encouragement, understanding, sacrifice and love.

## ABSTRACT

Nowadays the life cost more getting higher and higher. People more consider every dollar that they spend in their daily life. The price of gasoline more getting higher every year, this also make the life cost for each family increase. The price of electricity also increases because of the increase gasoline price. The people should spend their money with efficiently to make sure that the money that they spend is totally useful. There have two methods to save the electricity usage; the first one is using the electricity energy with smart, for example when the air-conditioner is not used it should turn off. The second is using the power factor correction technique, but this method just for inductive load such as air-conditioner, washing machine and refrigerator. The inductive load running causes the leading power factor, means the current that used is more and not totally used. To overcome this problem the reactive component is added, the capacitor is added to improve the power factor and also reduce the current that transfer to the inductive load. The microcontroller (PIC) is use as a control element that switching the capacitor to the power line. The sensor is place at the power line to giving the signal to the microcontroller, microcontroller analyze the signal that feed from the sensor. Microcontroller execute the instruction depend to the signal that giving.

## ABSTRAK

Pada setiap tahun taraf hidup semakin meningkat dan setiap orang mengira setiap ringgit yang mereka belanjakan. Pada setiap tahun juga harga bahan api terutamanya petrol meningkat berikutan perminataan yang tinggi oleh setiap Negara. Ini menyebabkan tarif elektrik meningkat berikutan meningkatnya harga bahan api di pasaran. Setiap orang perlu menggunakan duit mereka dengan bijaknya bagi menanpung perbelanjaan sara hidup yang makin meningkat. Bagi mengurangkan beban yg ade mereka seharusnya menggunakan elektrik dengan sebaiknya. Ada dua kaedah untuk menjumatkan penggunaan elektrik, salas satunya ialah menggunakan elektrik dengan jimat cermat sebagai contoh apabila tmeninggalkan bilik penyaman udara dan perkakas elektrik yang lain seharusnya dimatikan. Keadah ini berkesan bagi menjimatkan elektrik tetapi penggunaan elektrik masih tidak efisyen. Kaedah kedua adalah menggunakan teknik pembetulan faktor kuasa, tetapi kaedah ini hanya berkesan bagi alat yang mengunakkan applikasi moto. Apabila alat berplikasi moto bekerja faktor kuasa dalam talian kuasa menjadi rendah iaitu mengekori. Bagi membetulkan balik komponent reaktif diperlukan, kapasitor adalah komponent reaktif digunakan bagi membetulkan balik faktor kuasa. Pemprosesan Kawalan Mikro (PIC) digunakan bagi mengawal kemasukan kapasitor dalam talian. Kemasukan kapasitor bergantung kepada masukan data daripada peranti pengesan. Ini mengelakan daripada faktor kuasa mendahui daripada terjadi.

## **TABLE OF CONTENTS**

## CHAPTER

## TITLE

## PAGE

| DECLARATION           | ii  |

|-----------------------|-----|

| DEDICATION            | iii |

| ACKNOWLEDGEMENTS      | iv  |

| ABSTRACT              | V   |

| ABSTRAK               | vi  |

| TABLE OF CONTENTS     | vii |

| LIST OF TABLES        | Х   |

| LIST OF FIGURES       | xi  |

| LIST OF ABBREVIATIONS | xii |

| LIST OF APPENDICES    | xiv |

## 1 INTRODUCTION

| 1.1 | Project Background | 1 |

|-----|--------------------|---|

| 1.2 | Objectives         | 2 |

| 1.3 | Scope of Project   | 2 |

| 1.4 | Literature Review  | 2 |

| 1.5 | Thesis Outline     | 4 |

## 2 AUTOMATIC POWER FACTO R CORRECTION

| 2.1 | Introduction             | 6 |

|-----|--------------------------|---|

| 2.2 | Phase and Phasor Diagram | 7 |

# TITLE

PAGE

| 2 | 2.3 Automatic Power Factor Correction    | 8  |

|---|------------------------------------------|----|

|   | 2.4 Operation of APFC                    | 9  |

|   | 2.5 APFC Design                          | 10 |

|   | 2.5.1 Relay                              | 10 |

|   | 2.5.2 Current Transducer                 | 11 |

|   | 2.5.3 Voltage Transducer                 | 12 |

|   | 2.5.4 Capacitor                          | 13 |

|   | 2.6 Summary                              | 13 |

| 3 | CONTROL ELEMENT CIRCUIT                  |    |

|   | 3.1 Introduction                         | 15 |

|   | 3.2 Microcontroller (PIC) Features       | 16 |

|   | 3.2.1 PIC 18F4550                        | 16 |

|   | 3.2.2 Input and Output Used              | 17 |

|   | 3.2.3 Crystal Oscillator                 | 18 |

|   | 3.3 Software and Hardware Implementation | 19 |

|   | 3.3.1 Microcode Studio                   | 19 |

|   | 3.3.2 PICkit USB Programmer              | 22 |

|   | 3.3.2.1 Plugging the Microcontroller PIC | 22 |

|   | 3.3.2.2 Program the Microcontroller PIC  | 24 |

|   | 3.4 Summary                              | 25 |

| 4 | DEVELOPMENT OF AUTOMATIC POWER           |    |

|   | FACTORCORRECTION DEVICE                  |    |

|   | 4.1 Introduction                         | 26 |

| 4.1 | Introduction       | 20 |

|-----|--------------------|----|

| 4.2 | Project Flow       | 26 |

| 4.3 | Proposed Design    | 27 |

| 4.4 | Hardware Design    | 28 |

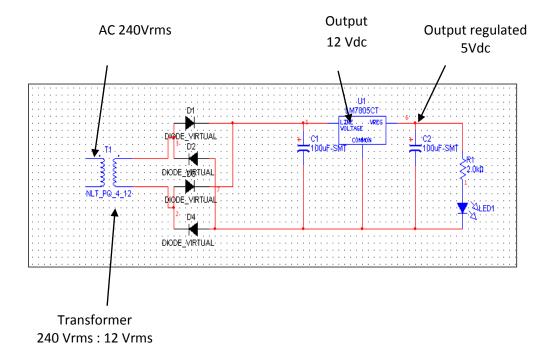

|     | 4.4.1 Power Supply | 29 |

# TITLE

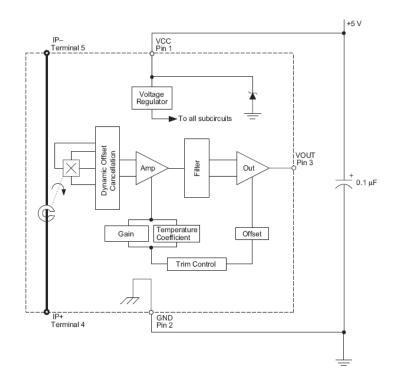

| 4 | 4.4.2 Current Sensor                   | 30     |

|---|----------------------------------------|--------|

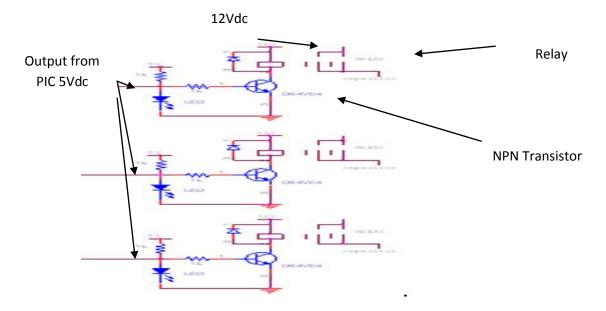

|   | 4.4.3 Driver Relay Circuit             | 31     |

|   | 4.4.4 Control Circuit                  | 32     |

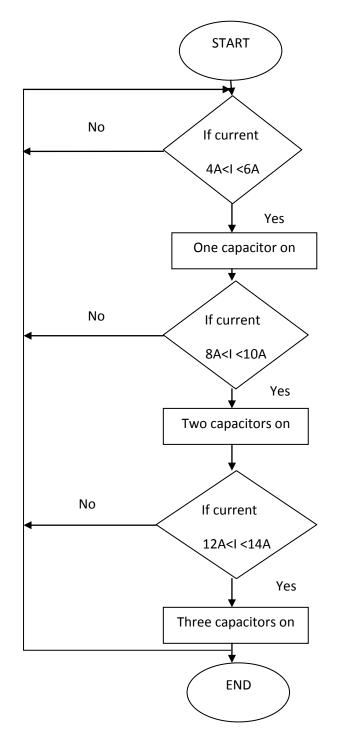

|   | 4.5 Flow Chart                         | 33     |

|   | 4.6 Hardware Operation Process         | 36     |

|   | 4.7 Summary                            | 36     |

| 5 | <b>RESULT AND DISCUSSSION</b>          |        |

|   | 5.1 Result of Power Supply             | 38     |

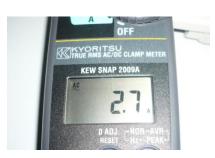

|   | 5.2 Result Current Sensor              | 40     |

|   | 5.3 Result for Power Factor Correction | 40     |

|   | 5.4 Analysis of the Load Tested        | 42     |

|   | 5.5 Discussion                         | 45     |

|   | 5.6 Summary                            | 45     |

| 6 | <b>CONCLUSIONS &amp; SUGGESTIONS</b>   |        |

|   | 6.1 Conclusions                        | 46     |

|   | 6.2 Suggestions                        | 47     |

|   | 6.3 Costing and Commercialization      | 47     |

|   | 6.3.1 Costing                          | 48     |

|   | 6.3.2 Commercialization                | 49     |

|   | REFERENCES                             | 51     |

|   | Appendices A-G                         | 52-116 |

Х

xi

## LIST OF TABLES

| TABLE NO. | TITLE                  | PAGE |

|-----------|------------------------|------|

|           |                        |      |

| 5.1       | Output Current Sensor  | 40   |

| 5.2       | Result for Tested Load | 44   |

| 6.1       | Cost of Component      | 48   |

## LIST OF FIGURES

| FIGURE | TITLE                                      | PAGE |

|--------|--------------------------------------------|------|

| NO.    |                                            |      |

| 2.1    | Power Factor Triangle                      | 7    |

| 2.2    | Phase Diagram for Leading Pf               | 8    |

| 2.3    | Waveform Voltage and Current               | 9    |

| 2.4    | Block Diagram Power Factor Controller      | 10   |

| 2.5    | Relay                                      | 11   |

| 2.6    | Current Transducer                         | 12   |

| 2.7    | Voltage Transducer                         | 12   |

| 2.8    | Capacitor                                  | 13   |

| 3.1    | PIC 18F4550 Pins Diagram                   | 17   |

| 3.2    | Connection Input and Output                | 18   |

| 3.3    | Symbol Crystal and Equivalent Circuit      | 19   |

| 3.4    | Configuration PIC 18F4550                  | 20   |

| 3.5    | Setting the Analog Digital Converter (ADC) | 21   |

| 3.6    | Compile and Checking Error                 | 21   |

| 3.7    | PICkit USB Programmer                      | 22   |

| 3.8    | Plugging 18 Pins PIC                       | 23   |

| 3.9    | Plugging 40 Pins PIC                       | 23   |

| 3.10   | PICkit Programmer                          | 24   |

| 3.11   | Import Hex File                            | 25   |

| 4.1    | Purposed Design APFC                       | 27   |

| 4.2    | Schematic Power Supply                     | 29   |

| 4.3    | Block Diagram Current Sensor               | 30   |

|   | ٠ | ٠ |

|---|---|---|

| v | 1 | 1 |

| • | 1 | г |

|   |   |   |

| FIGURE | TITLE                                      | PAGE |

|--------|--------------------------------------------|------|

| NO.    |                                            |      |

| 4.4    | Schematic Driver Relay Circuit             | 32   |

| 4.5    | PIC with Input and Output Connection       | 33   |

| 4.6    | Flow Chart of the System                   | 35   |

| 5.1    | Result Input LM7805                        | 39   |

| 5.2    | Result Output LM7805                       | 39   |

| 5.3    | Current Draw Before APFC Function (600W)   | 41   |

| 5.4    | Current Draw After APFC Function (600W)    | 41   |

| 5.5    | Current Draw before APFC operate (1.32KW)  | 41   |

| 5.6    | Current Draw after APFC operated (1.32KW). | 42   |

## LIST OF ABBREVIATIONS

| AC                        | - | Alternate Current                 |  |

|---------------------------|---|-----------------------------------|--|

| ADC                       | _ | Analog to Digital Converter       |  |

| DC                        | - | Direct Current                    |  |

| APFC                      | _ | Automatic Power Factor Correction |  |

| Vac                       | _ | Voltage alternate Current         |  |

| LED                       | _ | Light Emitting Diode              |  |

| LCD                       | - | Liquid Crystal Display            |  |

| PIC                       | - | Programmable Intelligent Computer |  |

| Vdc                       | _ | Voltage Direct Current            |  |

| TNB                       | _ | Tenaga Nasional Berhad            |  |

| VAR                       | _ | Unit of Appearent Power           |  |

| $\mathbf{V}_{\mathrm{o}}$ | - | Output Voltage                    |  |

## LIST OF APPENDICES

## APPENDIX

## TITLE

## PAGE

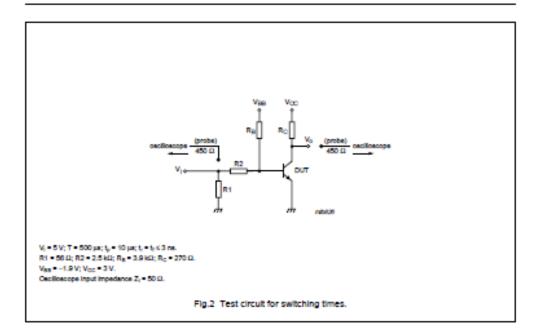

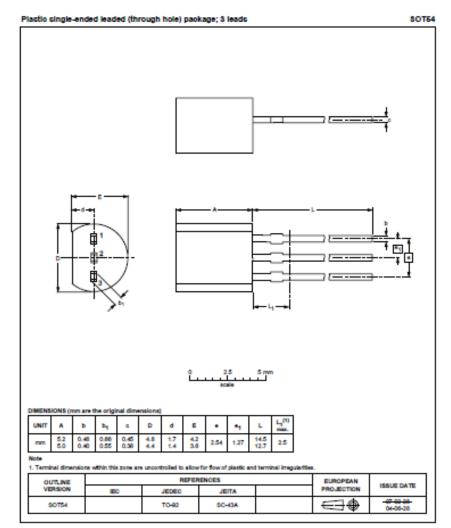

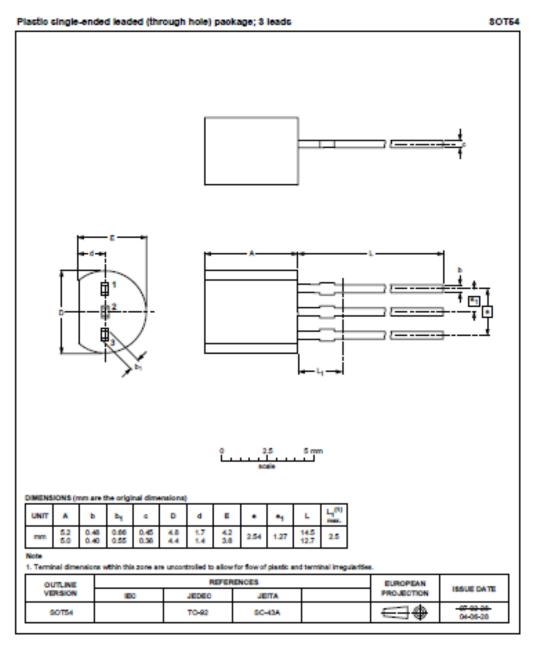

| A | Transistor 2N3904 Data Sheet                      | 52  |

|---|---------------------------------------------------|-----|

| В | PIC18F4550 Microcontroller, Addressing Modes, and | 59  |

|   | Instruction Set                                   |     |

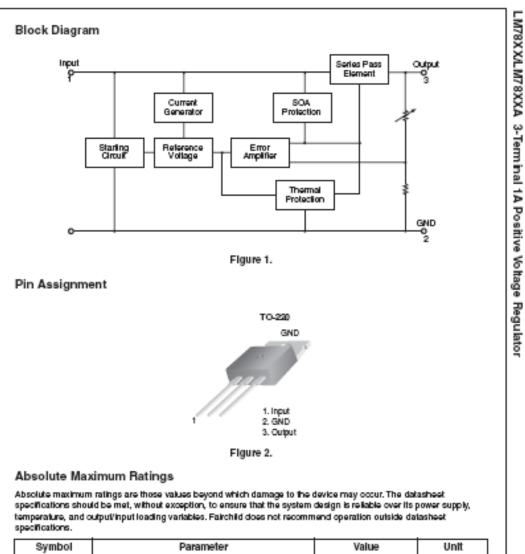

| С | LM7805 Voltage Regulator Data Sheet               | 91  |

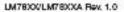

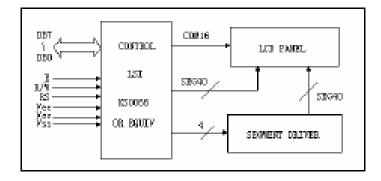

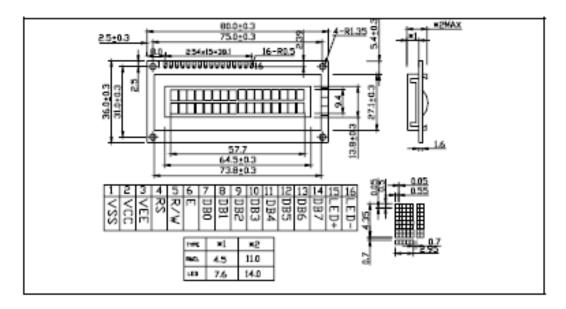

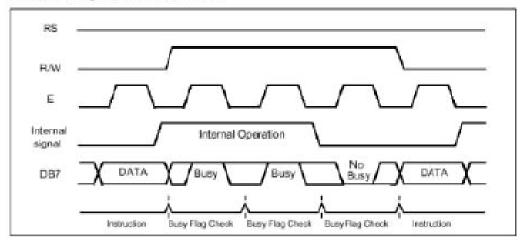

| D | JHD162A Series Datasheet                          | 100 |

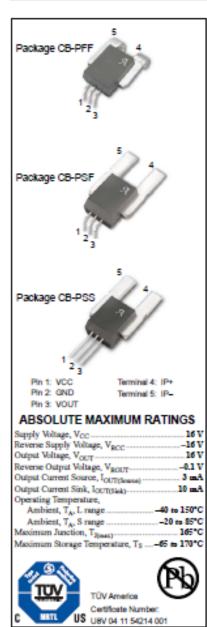

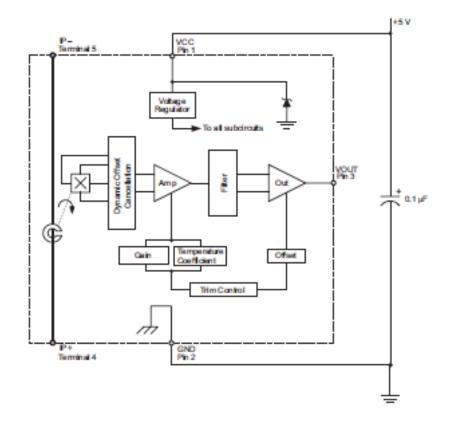

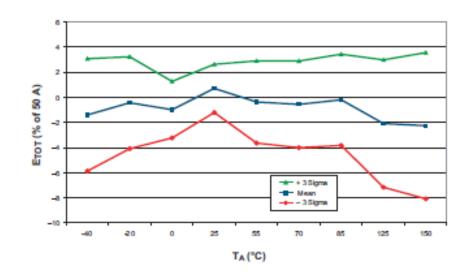

| Е | Current Sensor Data Sheet                         | 105 |

| F | APFC Program                                      | 111 |

| G | Biodata of the Author                             | 115 |

## **CHAPTER 1**

### INTRODUCTION

### 1.1. Project Background

In the recent year the life cost is getting more expensive and the people need to consider all the money that they spend. The electric tariff from TNB getting higher in every year because the electric tariff, depend to the price of gasoline. The electricity bills is the one of the life cost that need to support because without electric people can't do their daily life. To minimize the electric bill in the manual method is try to use the electric with the smart. The other method to minimize the electric bill is used the automatic power factor correction (power saver).

This project is focus on the design and building a unit of automatic power factor correction, this device more suitable and effective in the house that used a lot of inductive component such as air-conditioner, washing machine and etc. This device is function as the power factor corrector to improve the power factor to unity. The value of capacitor that insert in the system is depend to the value of power factor that control by microcontroller.

The problems of this we have to determine the value of the power factor and the value of the capacitor that we need to insert in the system. The value of the capacitor is the most important because it will change the power factor to unity and significantly the current to the load is reduce. This is the main problem we have to focus because it will determine the percentage of the save the electricity.

## 1.2. Objectives:

The objectives of this project are:

- I. Develop automatic power factor correction (power saver)

- II. This device able to reduce the power consumption in the house and minimize the electricity cost.

- III. To help the people reduce the life cost by reduce the electricity cost.

### **1.3.** Scope of Project

The scope of this project can be summarizing as follows:

- I. This projects focus on the single-phase system 240Vac, for house application.

- II. The maximum current rating is 40A, suitable for house that usually current rating is same.

III. Device use 4 parallel capacitors to improve power factor.IV.

#### **1.4.** Literature Review

The power factor of an AC electric power system is defined as the ratio of the real power to the apparent power, and is a number between 0 and 1. Real power is the capacity of the circuit for performing work in a particular time. Apparent power is the product of the current and voltage of the circuit. Due to energy stored in the load and returned to the source, or due to a non-linear load that distorts the wave shape of the current drawn from the source, the apparent power can be greater than the real power. Low-power-factor loads increase losses in a power distribution system and result in increased energy costs [1].

The significance of power factor lies in the fact that utility companies supply customers with volt-amperes, but bill them for watts. Power factors below 1.0 require a utility to generate more than the minimum volt-amperes necessary to supply the real power (watts). This increases generation and transmission costs. For example, if the load power factor were as low as 0.7, the apparent power would be 1.4 times the real power used by the load. Line current in the circuit would also be 1.4 times the current required at 1.0 power factor, so the losses in the circuit would be doubled (since they are proportional to the square of the current). Alternatively all components of the system such as generators, conductors, transformers, and switchgear would be increased in size (and cost) to carry the extra current [2].

Interfacing the microprocessor with the AC power lines need to consider the voltage, current and also power dissipated by the microcontroller (PIC). The PIC chip only support 1W power dissipation [1]. The phase voltage and current is detected using the current and voltage transducer. Using the external existing unique function (zero crossing detector) in PIC16F77 the phase shift between voltage and current is determine [1]. High external resistor must be connect place before connect to input circuit, to ensure that PIC not damage. PIC 16C5X series is design to short the input when the large voltage is applied to protect the chip from static electric short [3].

The Hall Effect sensor is the one device that used to interface between the power line and the microcontroller (PIC) [4]. This sensor is connecting series with the inductive load. It has an internal current transducer that senses the electromagnetic field. It also produce the output voltage that suitable for the PIC (0V-5V), this output voltage is in AC because use in the AC application, it also suitable use in DC application. This device precise is depending to the temperature, it sense the fully scale current at the  $25^{\circ}$ C [4].

### **1.5. Report Outline**

This report is divided into six chapters. Chapter 1 is explaining about the background of the project, objectives, scope of project and literature review. Chapter 2 explaining about the power factor, phase and phasor diagram, automatic power factor correction, current sense conventional APFC and summary for this chapter. The new automatic power factor correction device (power saver) should have ability to reduce the power factor to unity when the inductive component exists in the system. This device should have a correct trigger the step of the capacitor to accomplish the value VAR in the system and the current transfer to load is less. Chapter 3 explain about the control element circuit, the PIC 18F4550 is used as a brain of the system, this microcontroller PIC is used to monitor all the changing current in the system that feed by the current sensor. The porta is used to feed the input because only porta have the special features that can receive analog input. The oscillator is the important thing that generates the frequency when the voltage is given. The frequency generate is feed to the microcontroller and as a clock for microcontroller to function. Microcode studio is used to write and compile. It convert pbp file to the hex file. The PICkit is used to burn the program to the microcontroller, the hex file is transfer to the PICkit program and it transfer into microcontroller. Chapter 4 explains about methodology of the project. The power factors is study fist and also find the technique to improve the power factor. The purpose design for this project is using the current sensor as the input and the driver relay circuit as an output. The current sensor is feed the signal to the microcontroller, the microcontroller analyze and give the output to the driver relay circuit according the condition that stated in the programming. Chapter five explain about the result and discussion, the result of the power factor is determined using the motor load. There have two type of motor used, first is 600W motor, the current 0.3A are reduce after the APFC operate. The initial power factor is 0.83pf and after insert the capacitor insert the power factor become 0.92pf. Second is 1.32KW motor, current 0.5A are reduce after APFC operate. The initial power factor is 0.77pf and after insert capacitor the current is 0.83pf. Chapter 6 explains about the conclusion and suggestion. This device is able to reduce the current usage by the inductive load.

## **CHAPTER 2**

#### **AUTOMATC POWER FACTOR CORRECTION (APFC)**

### 2.1. Introduction

Power factor is the ratio of true power or watts to apparent power or volt amps. They are identical only when current and voltage are in phase then the power factor is 1.0. The power in an ac circuit is very seldom equal to the direct product of the volts and amperes. In order to find the power of a single phase ac circuit the product of volts and amperes must be multiplied by the power factor. Ammeters and voltmeters indicate the effective value of amps and volts. True power or watts can be measured with a wattmeter. If the true power is 1870 watts and the volt amp reading is 2200. Than the power factor is 0.85 or 85 percent. Real power divided by apparent power. The power factor is expressed in decimal or percentage. Thus power factors of 0.8 are the same as 80 percent. Low power factor is usually associated with motors and transformers. An incandescent bulb would have a power factor of close to 1.0. A one hp motor has power factor about 0.80. With low power factor loads, the current flowing through electrical system components is higher than necessary to do the required work. These results in excess heating, which can damage or shorten the life of equipment, a low power factor can also cause low-voltage conditions, resulting in dimming of lights and sluggish motor operation.

Low power factor is usually not that much of a problem in residential

homes. It does however become a problem in industry where multiple large motors are used. So there is a requirement to correct the power factor in industries. Generally the power factor correction capacitors are used to try to correct this problem.

For a DC circuit the power is P=VI and this relationship also holds for the instantaneous power in an AC circuit. However, the average power in an AC circuit expressed in terms of the rms voltage and current is

$$P_{avg} = VI \cos \varphi$$

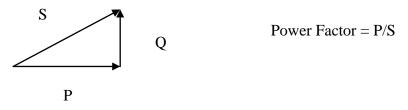

Where,  $\phi$  is the phase angle between the voltage and current. The additional term is called the power factor. Power factor triangle is shown in Figure 2.1.

Figure 2.1: Power Factor triangle

From the phasor diagram for AC impedance, it can be seen that the power factor is P/S. For a purely resistive AC circuit, P=S and the power factor = 1.

### 2.2. Phase and Phasor Diagram

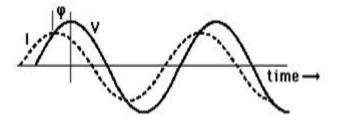

When capacitors or inductors are involved in an AC circuit, the current and voltage do not peak at the same time. The fraction of a period difference between the peaks expressed in degrees is said to be the phase difference. The phase difference is  $\leq 90$  degrees. It is customary to use the angle by which the voltage leads the current. This leads to a positive phase for inductive circuits since current

lags the voltage in an inductive circuit. The phase is negative for a capacitive circuit since the current leads the voltage. Figure 2.2 shows the waveform for voltage and current when the power factor is leading. The current lead the voltage because the inductive component running.

Figure 2.2: Phase Diagram for leading PF

#### 2.3 Automatic Power Factor Correction

An automatic power factor correction (APFC) is a device that used to improve the power factor to unity using the microcontroller. Usually the automatic power factor correction is used in the industry such as the factory that used the biggest horse power (hp) motor. Such as the chiller system, chiller system is the one of the type air-conditioner. This chiller used the motor to operate; motor is used as pump to pump the water for each floor in the building. The motors that used have 200hp each to pump the water in each floor. This motor is operate when the temperature high inside the building and off when the temperature reach at the desire level. The automatic power factor correction is needed here because to maintain the value of the power factor unity. The value of power factor unity is important because it will affect the current and voltage drop in the system. Second is TNB will give the penalty if the power factor below that 0.8, power factor below that 0.8 need to supply more energy to this system and make them loss out. This device is function to monitor the system that makes sure that the value of the power factor approach to unity.

#### 2.4 Operation of APFC

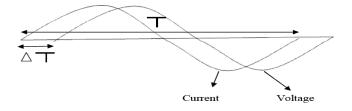

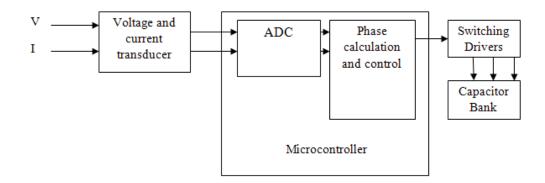

The automatic power factor correction is the device the used the microcontroller to analyze the power factor in the system. The microcontroller is the brain of the system because where the power factor is analyze and determine the value. Microprocessor receives the signal from the voltage and current transducer. Microprocessor is build in the analog digital converter, This ADC is used to convert analog signal to the digital signal, the digital signal from the current and voltage transducer is analyze. To determine the power factor zero-crossing detector is used. The programming of microprocessor is the most important because, if the inductive components running the voltage are lagging current. The signal from the current transducer will on the timer and the signal from voltage off the timer, from the delay between the current and voltage the power factor is determine. Figure 2.3 show the time delay between current and voltage.

Figure 2.3: Waveform voltage and current

The value of capacitor is depends to the value of the VAR that used in the system (motors). The microprocessor will give the signal the contactor to turn on capacitor to the system depend to the value of VAR that used. The steps of the capacitor usually for the system is depend to the how many the inductive component (VAR) in the system. That means before the automatic power factor is design the value of the VAR in system need to know first and the how many steps of the capacitor will determine. The figure 3.2 shows the block diagram for the system.

Figure 2.4: Block diagram Power factor Controller

### 2.5 APFC Design

There are two circuits for design automatic power factor correction. First is control circuit that consists of microcontroller, two transducers and driver relays. Second is power circuit that consists of capacitor bank and relay.

## 2.5.1 Relay

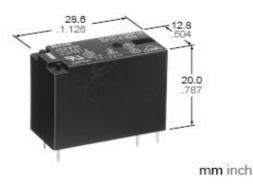

A relay is an electrical switch that opens and closes under the control of another electrical circuit. In the original form, the switch is operated by an electromagnet to open or close one or many sets of contacts. Because a relay is able to control an output circuit of higher power than the input circuit, it can be considered, in a broad sense, to be a form of an electrical amplifier. Current flowing through the coil of the relay creates a magnetic field which attracts a lever and changes the switch contacts. The coil current can be on or off so relays have two switch positions and they are double throw (changeover) switches. Usually this is a spring, but gravity is also used commonly in industrial motor starters. Most relays are manufactured to operate quickly. In a low voltage application, it is used to reduce noise. In a high voltage or high current application, it is used to reduce arcing. The symbol circuit of relay and the relay are shown in Figure

Figure 2.5: Relay

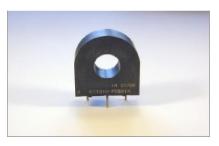

#### 2.5.2 Current Transducer

There are several types of current detector such as current transducer, transtronics current detector and current transformer which are use for detected current by sensing the AC current. This device is function when the wire carrying the current through the coil. The magnetic field form from the wire will detect, the coil consist in the current transducer will induce the current, acting like transformer. Figure 3.4 below the current transducer. The application of current transducer normally use in sensing overload current, ground fault detection, metering and analog to digital circuit.

Figure 2.6: Current Transduccer

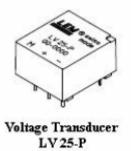

### 2.5.3 Voltage Transducer

Voltage transducer is function like a transformer. The voltage in the system will step down; the voltage step down is depending to the coil. For this project the voltage is step down from 240Vac to 5Vac, before the signal sense to the microcontroller the current is limited using the large value of the resistor. The high current produce when the transformer is step down, current is limited because the microcontroller can accept only 1W power consumption. The higher current will damage the microcontroller. Figure 3.5 show the LV 25-P voltage transducer.

Figure 2.7: Voltage Transducer

#### 2.5.4 Capacitor

Capacitor is the main important because it will improve the power factor and reduce the current that transfer to the load. The capacitor that used is has the voltage rating 400V. This value of the voltage rating is suitable for single phase. Figure 3.6 show the ELCO capacitor.

| ELCO    | 1 0 AF 1 5% 25/85.<br>4007 CLB 50/60H<br>4507 CLC PO SH |

|---------|---------------------------------------------------------|

| PSB TUV | IEC 60252-1 33<br>D701072-12<br>MADE IN MALAYS          |

Figure 2.8: Capacitor

### 2.6 Summary

The power factor is exists when the capacitor and inductor component operate in the ac circuit. Usually the load is inductive load such as motor application, when the motor running the power factor in the system is low; to improve the power factor the capacitor component which called capacitor bank is inserting in the system. The value of the capacitor is depending to the value of the VAR that used. The current sense for APFC is not suitable because not efficiency to improve the power factor and also reduce the current used by inductive components. The automatic power factor correction device consist two circuits, control and power circuit. The control circuit consist of transducers, microcontroller and drivers relay. The signal is feed to the microcontroller using the transducers. Microcontroller analyzes the power factor in the system and sends the signal to the drivers relay. driver relay will on the steps of capacitor depend to the power factor. This process continuous until the power reaches to power factor unity.

## **CHAPTER 3**

## **CONTROL ELEMENT CIRCUIT**

### 3.1 Introduction

PIC is widely used to as a control element circuit for the device or electrical equipment. PIC is a family of Harvard architecture microcontrollers made by Microchip Technology, derived from the PIC164originally developed by General Instrument's Microelectronics Division. The name PIC initially referred to "**Peripheral Interface Controller**". PICs are popular with developers and hobbyists alike due to their low cost, wide availability, large user base, extensive collection of application notes, availability of low cost or free development tools, and serial programming (and re-programming with flash memory) capability. The Harvard architecture is different with the von Neumann architecture because it can read an instruction and perform the data memory access at the same time. This is because this Harvard architecture can read and writing in the same time and this significantly to the times taken to execute the instruction. This Harvard architecture also take less time and more efficiency to execute the instruction and it user friendly because the programmer easy to write the program.

#### **3.2** Microcontroller (PIC) Features

The feature of microcontroller (PIC) is can only operate when two Vcc (5Vdc), two Gnd (0Vdc) and one oscillator. The PIC will blow if the voltage exceed 5Vdc is given and the polarity is reverse are connected. The microcontroller (PIC) is easy to use because is no additional memory and no need to connect the buffer or latch circuit to interface with the input or output device.

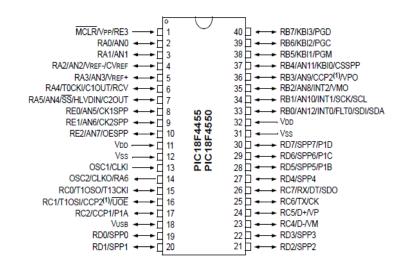

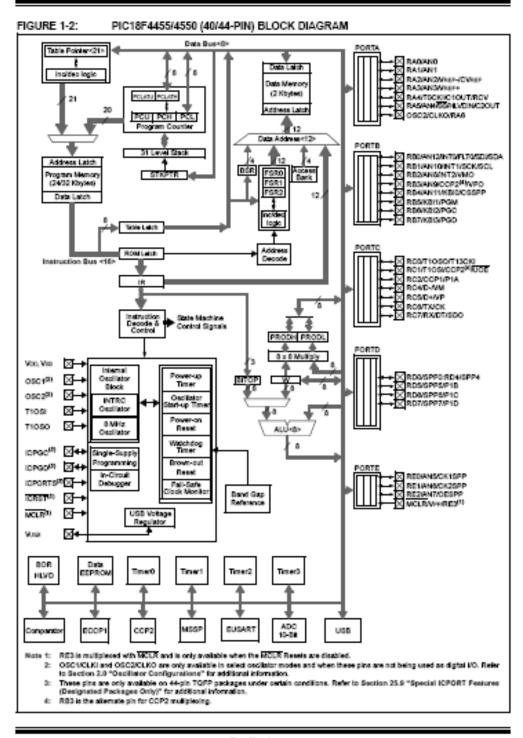

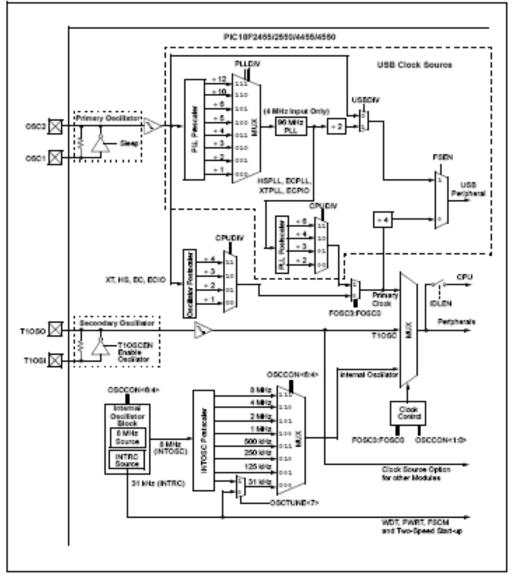

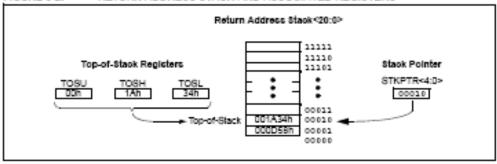

#### 3.2.1 PIC 18F4550

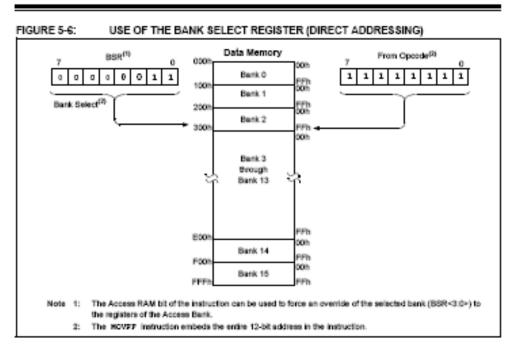

The type of the microcontroller (PIC) that chooses for this project is PIC 18F4550, this PIC has 40 pins and has four ports. The PIC function when the 5Vdc is apply and the oscillator is connect, the diode is add at the Vcc pin to avoid the damage when the user incorrect connect between Vcc and Gnd. The port for this PIC is porta, portb, portc and portd, porta is the special port because it has the analog digital converter. The function analog digital converter is to convert the analog signal form to the digital signal form because build in microprocessor only understand the digital signal to function. Another port is use as the digital port, it only understand the logic 1 (5Vdc) or logic 0(0Vdc). This port can be set whether input the output using the program declaration. The oscillator is used to generate the frequency (pulse form) to the microcontroller, the more high value of oscillator more fast the program or instruction execute by the PIC. The pins 11 and 32 are connecting with the Vcc (5Vdc0), pins 12 and 31 are connecting with the Gnd (0Vdc) and the pins 13 and 14 are connecting to the oscillator. The figures 3.1 below show the PIC 18F4550 pins.

Figure 3.1: PIC 18F4550 Pins Diagram

#### 3.2.2 Input and Output Port Used

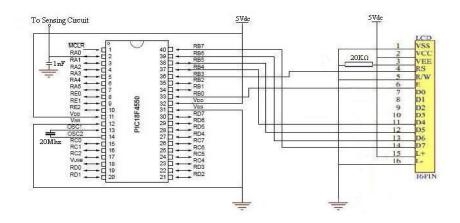

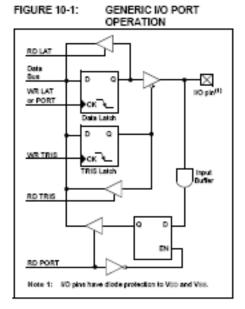

The input and output use for this project are porta, portb and portd. The porta is set as a input port, this port receive the signal from the sensor circuit. Porta ia a special port for the all type of PIC because it use for the analog input, this port is use for this project to given signal to the build in microprocessor, it convert the voltage level that receive from the sensor circuit to the digital form and send to the microprocessor. The maximum bit for ADC this PIC is 10 bits, this will define when the program is write. The pin no 2 is use as a analog signal output. The portb is use as an output to give the signal to the driver relay circuit to operate, it give the logic 1 (5Vdc) to the transistor to operate the relay. The portc is also use as an output for the LCD display. The interface with the LCD, PIC need use the special instruction in the program to operate the LCD. The figure 3.2 below show the connection input and output device with the PIC.

Figure 3.2: Connection Input and Output

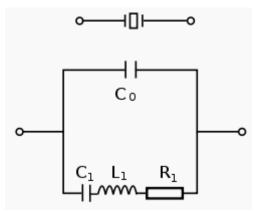

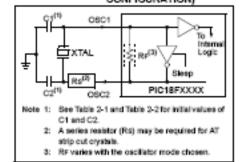

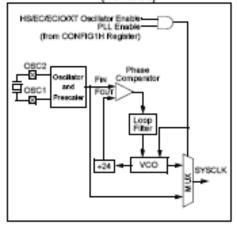

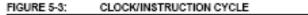

#### 3.2.3 Crystal Oscillator

Crystal Oscillator is electronic circuits that use the mechanical resonant of a vibrating crystal of piezoelectric material to create an electrical signal with a very precise frequency. This frequency is commonly used to keep track of time (as in quartz wristwatches), to provide a stable clock signal for digital integrated circuits, and to stabilize frequencies for radio transmitters and receivers. The quartz need to cut properly to make sure that the amount of the frequency is reaches. When the voltage is applying to the quartz it will beat and generate the frequency, the quartz crystal is behaved like a circuit composes of an inductor, capacitor and resistor with precise of the frequency. The quartz crystal is equivalent with the RLC circuit. The value of the crystal come to many size (Mhz), it depend to the cutting of the quartz stone. The figures 3.3 show the symbol and equivalent circuit for the crystal oscillator.

Figure 3.3: Symbol Crystal and Equivalent Circuit

# 3.3 Software and Hardware Implementation

Software that use for this project function to make the programmer easier to write the program, the language used is C language. The C language is easy because the programmer easy t understand the function of the instruction. The instruction is the word that has the sir turn task for the microcontroller (PIC) to execute the task that has been burn into microcontroller.

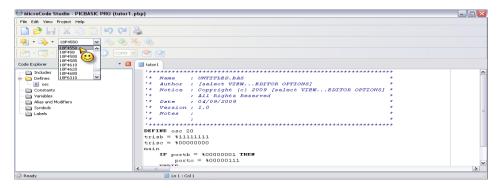

# 3.3.1 Microcode Studio

MicroCode Studio is a powerful, visual Integrated Development Environment (IDE) with In Circuit Debugging (ICD) capability designed specifically for microEngineering Labs PICBasic PRO compiler. The code explorer allows you to automatically jump to include files, defines, constants, variables, aliases and modifiers, symbols and labels that are contained within your source code. It's easy to set up your compiler, assembler and programmer options or you can let MicroCode Studio do it for you with its built in autosearch feature. Compilation and assembler errors can easily be identified and corrected using the error results window. MicroCode Studio even comes with a serial communications window

The In Circuit Debugger (ICD) enables you to execute a PICBasic Program on a host PIC microcontroller and view variable values, Special Function Registers (SFR), memory and EEPROM as the program is executing. You can toggle multiple breakpoints and step through your PICBasic code line by line. The graphical interface is built on microEngineering Labs debug architecture, which is both efficient and robust. In this project, there are several steps that have to setup first before write the program and compile it.

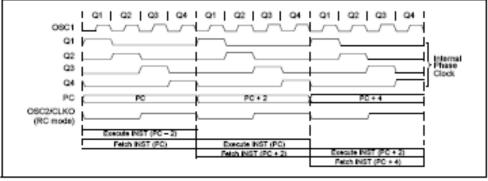

Step 1, below, is step to configure programming. In this project, we use PIC18F4550. So, we must select configuration of PIC18F4550 in figure 3.4 below.

Figure 3.4: Configuration PIC18F4550

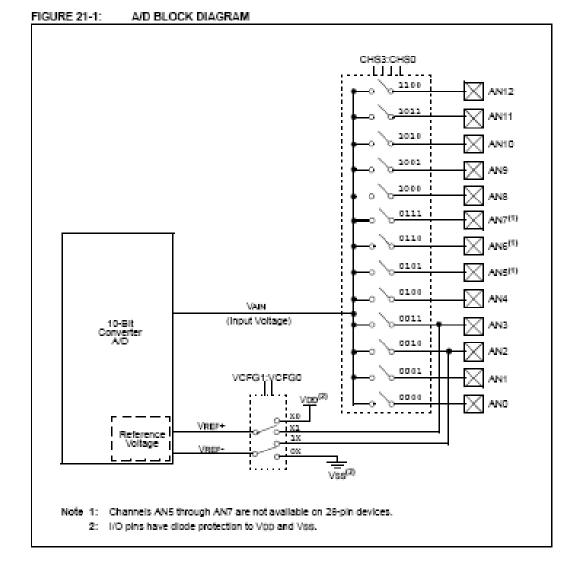

Step 2, we must define oscillator 20MHz. It is because, in the project we use oscillator 20MHz. Define ADC (analog to digital) 8 bits. ADC clock sample = 3 and ADC sampleus = 50. Figure 3.5 below show how to setting.

| MicroCode Studio - PICBASIC PRO (Untitle)     File Edit View Project Help                                                                                                   | d.bas)                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 🏶 • 💫 • 18F4550 💽 🧠 🍫                                                                                                                                                       | 🗞 🔍                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 🐏 - 💫 - 🕟 💿 🕕 💿 сомз 🛛                                                                                                                                                      | 2 😬 🔮                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Code Explorer 🔹 🔀                                                                                                                                                           | Untitled                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Includes     Defines     OSC     OSC     OAC_SITS     OAC_CLOCK     OAC_SAMPLEUS     Constants     Variables     Variables     Variables     Symbols     Symbols     Labels | <pre>'* Author : [select VIEWEDITOR OPTIONS] '* Notice : Copyright (c) 2009 [select VIEW' '* : All Rights Reserved '* Date : 07/09/2009 '* Version : 1.0 '* Notes : '* DeFine osc 20 ; set the value oscillator that DeFine osc 20 ; set the value oscillator that DeFine Adc_BITS 8; set NUMBER of BITD DeFINE ADc_CLOCK 3; set CLOCK SOURCE DeFINE ADc_SAMPLEUS 50; set SAMPLING TIME ADVAL VAR BYTE; create Adval to STRORE INPUT DAT.</pre> |

|                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| O Ready                                                                                                                                                                     | Ln 11 : Col 53                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Figure 3.5: Setting the Analog Digital Converter

Step 3, after all of setting has been configured, it may be able to be written according to the flowchart of microcontroller based power factor correction Cart program. Then after finishing write the program, it has to be compiling using the compiler button or press F9. This action has to be perform because it can check whether there is error or misuse command while write the program. The Figure 3.6 shown how to compile and checking error.

| File Edit View Project I                                                                                                       | à 🛅 🖢 🛯 🍓 🖣 | ***** |                   |   |

|--------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-------------------|---|

| Code Explorer   Code Explorer  Code Explorer  Constants  Constants  Constants  Constants  Constants  Constants  Labels  Labels | asd         |       | Coma      P     P |   |

| < >                                                                                                                            | <           |       |                   | > |

Figure 3.6: Compile and Checking Error

### 3.3.2 PICkit USB Programmer

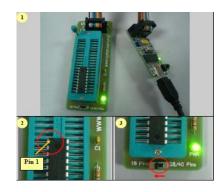

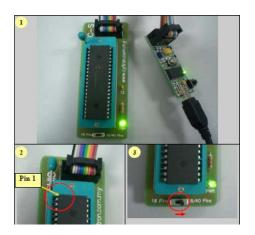

PICkit USB programmer is used to write (burn) PIC. The device is design to interface between the computer and the microcontroller (PIC). The USB port is used to transfer the data from the computer to the PIC. This device has the PIC holder that used to make sure the PIC's pins connect with the holder. Figure 3.7 show the picture of the PICkit programmer. There have five component to operate this device, first UIC00A is used as a driver to interface between PIC and computer, second mini USB cable, third rainbow cable to connect between UIC00A with the no five, fourth software installation and user's manual CD and fifth UIC-S socket board use to hold the PIC.

Figure 3.7: PICkit USB Programming

#### **3.3.2.1** Plugging the Microcontroller (PIC)

The microcontroller must be plugging in the UIC-S socket with proper because cause the damage to the microcontroller (PIC) if the wrong instruction use. There have two types to program the PIC, first if the pins of the PIC if less than 18 pins the switch of the bottom must be select 18 pins and the microcontroller (PIC) must be put at the UIC-S socket as show in the figure 3.8. The first step, place the PIC at the UIC-S socket, second make sure that the dot mark at PIC is the right as show in the figure (2) above and the last is make sure that the switch is select at the 18 pins direction like show in figure.

Figure 3.8: Plugging 18 pins PIC

The second type is the PIC pin is 28 to 40 pins, the switch must be select at the 28/40 pins. The figure 3.9 below show the PIC has the 40 pins put at the UIC-S socket. The first step, place the PIC at the UIC-S socket, second make sure the dot mark at OIC is the right side as show in figure and third is make sure the switch is select at the 28/40 pins direction.

Figure 3.9: Plugging 40 pins PIC

#### 3.3.2.2 Program the PIC Microcontroller

To program the PIC using the PICkit USB programmer, the Hex file must be produce first. The Hex file is getting from the microcode, where the C language is write and the language is compile using the compiler that has in the microcode. After C language is compile and the error has been check the Hex file will exist, this Hex file is at the where the Sps file is save. The software PICkit is install in the computer using the instruction that stated in the CD. Finish the installation the icon PICkit appear in the desktop, double click the icon and the software is running, it automatically detect the PIC that place at the UIC-S socket as show in figure 3.10 below.

| ile Devic                                                                                           | e Family                                                             | Programme                                                    | er Tools                                                     | Help                                                         |                                                              |                                                      |                                                                      |                                                                      |            |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|------------|

| PIC18F Cor                                                                                          | figuration                                                           |                                                              |                                                              |                                                              |                                                              |                                                      |                                                                      |                                                                      |            |

| Device:                                                                                             | PIC18F4                                                              | 4550                                                         |                                                              | Config                                                       | uration: 0                                                   | 500 1F1F                                             | F 8300                                                               | 0085                                                                 |            |

| Hser IDs:                                                                                           | FE FE FI                                                             | E EE EE EE E                                                 | FFF                                                          |                                                              | C                                                            | 00F E00                                              | F 400F                                                               |                                                                      |            |

| Checksum:                                                                                           | 8358                                                                 |                                                              |                                                              |                                                              |                                                              |                                                      | BandGap:                                                             |                                                                      |            |

| Checksum:                                                                                           | 0000                                                                 |                                                              |                                                              |                                                              |                                                              |                                                      | o andu ap:                                                           |                                                                      |            |

| PICkit 2 c                                                                                          | onnected                                                             | d. ID = U                                                    | ICOOA re                                                     | v1.0                                                         |                                                              |                                                      |                                                                      | ROCH                                                                 |            |

| PIC Devic                                                                                           | e Found                                                              |                                                              |                                                              |                                                              |                                                              |                                                      | NAUC                                                                 | HULF                                                                 |            |

|                                                                                                     |                                                                      |                                                              |                                                              |                                                              |                                                              |                                                      | D Target                                                             |                                                                      |            |

| Read                                                                                                | Write                                                                | Verify                                                       | Eras                                                         |                                                              | ank Check                                                    | 5   5                                                | Check                                                                | 5,0                                                                  | \$         |

|                                                                                                     |                                                                      | Veniy                                                        | Elds                                                         |                                                              | ank crieck                                                   |                                                      | J /MULH                                                              |                                                                      |            |

| Program M                                                                                           | _                                                                    |                                                              |                                                              |                                                              |                                                              |                                                      |                                                                      |                                                                      |            |

| Enabled                                                                                             | Hex Or                                                               | ily 🚩                                                        | Source:                                                      | None (En                                                     | npty/Erased                                                  | 0                                                    |                                                                      |                                                                      |            |

| 0000                                                                                                | FFFF                                                                 | FFFF                                                         | FFFF                                                         | FFFF                                                         | FFFF                                                         | FFFF                                                 | FFFF                                                                 | FFFF                                                                 | ^          |

| 0010                                                                                                |                                                                      | FFFF                                                         | FFFF                                                         | FFFF                                                         | FFFF                                                         | TTTT                                                 | FFFF                                                                 |                                                                      | _          |

|                                                                                                     | FFFF                                                                 |                                                              |                                                              |                                                              |                                                              |                                                      |                                                                      | FFFF                                                                 |            |

| 0020                                                                                                | FFFF                                                                 | FFFF                                                         | FFFF                                                         | FFFF                                                         | FFFF                                                         | FFFF                                                 | FFFF                                                                 | FFFF                                                                 |            |

| 0020                                                                                                | FFFF<br>FFFF                                                         | FFFF                                                         | FFFF                                                         | FFFF<br>FFFF                                                 | FFFF                                                         | FFFF<br>FFFF                                         | FFFF<br>FFFF                                                         | FFFF<br>FFFF                                                         |            |

| 0020<br>0030<br>0040                                                                                | FFFF<br>FFFF<br>FFFF                                                 | FFFF<br>FFFF<br>FFFF                                         | FFFF<br>FFFF<br>FFFF                                         | FFFF<br>FFFF<br>FFFF                                         | FFFF<br>FFFF<br>FFFF                                         | FFFF<br>FFFF<br>FFFF                                 | FFFF<br>FFFF<br>FFFF                                                 | FFFF<br>FFFF<br>FFFF                                                 |            |

| 0020<br>0030<br>0040<br>0050                                                                        | FFFF<br>FFFF<br>FFFF<br>FFFF                                         | FFFF<br>FFFF<br>FFFF<br>FFFF                                 | FFFF                                                         | FFFF<br>FFFF<br>FFFF<br>FFFF                                 | FFFF<br>FFFF<br>FFFF<br>FFFF                                 | FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF                                         | FFFF<br>FFFF<br>FFFF<br>FFFF                                         |            |

| 0020<br>0030<br>0040<br>0050<br>0060                                                                | FFFF<br>FFFF<br>FFFF<br>FFFF                                         | FFFF<br>FFFF<br>FFFF<br>FFFF                                 | FFFF<br>FFFF<br>FFFF<br>FFFF                                 | FFFF<br>FFFF<br>FFFF<br>FFFF                                 | FFFF<br>FFFF<br>FFFF<br>FFFF                                 | FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF                                         | FFFF<br>FFFF<br>FFFF<br>FFFF                                         |            |

| 0020<br>0030<br>0040<br>0050<br>0060<br>0070                                                        | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                                 |            |

| 0020<br>0030<br>0040<br>0050<br>0060<br>0070<br>0080                                                | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                         |            |

| 0020<br>0030<br>0040<br>0050<br>0060<br>0070<br>0080<br>0090                                        | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 |            |

| 0020<br>0030<br>0040<br>0050<br>0060<br>0070<br>0080<br>0090<br>0040                                | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 |            |

| 0020<br>0030<br>0040<br>0050<br>0060<br>0070<br>0080<br>0090                                        | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | >          |

| 0020<br>0030<br>0040<br>0050<br>0060<br>0070<br>0080<br>0090<br>0040<br>0080                        | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         |            |

| 0020<br>0030<br>0040<br>0050<br>0060<br>0070<br>0080<br>0090<br>0040                                | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF         | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF                 | Hex        |

| 0020<br>0030<br>0040<br>0050<br>0060<br>0070<br>0080<br>0090<br>00A0<br>00B0<br>EEPROM<br>C Enabled | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF<br>FFFF | Hex<br>ice |

Figure 3.10: PIckit Programmer

Before the Hex file imported, the PIC nee to blank check first to make sure that there no program that exist in PIC. If have the program in the PIC the program need to erase first, to erase the program the erase button is press. The erase is complete when the no blinking red LED in the UIC00A. Then the verify button is press to verify the PIC is located at the right pins. Lastly click file at the top of the PICkit program and choose import Hex. After Hex file is import the button write is press to write the program to the PIC. The red LED is blink at the UIC00A and when red led stop blink the green LED id turn on, it show that the program is completely transfer to the PIC. This called burn process. The figures 3.11 above show the import Hex file to PICkit programmer.

| 🔁 PICkit 2 P | rogramn  | ner - UICO | 0A rev1. | 0         |           |           |           | _    |    |

|--------------|----------|------------|----------|-----------|-----------|-----------|-----------|------|----|

| File Device  | Family   | Programmer | Tools    | Help      |           |           |           |      |    |

| Import H     | lex O    | trl+I      |          |           |           |           |           |      |    |

| t H          | lex Ct   | rl+E       |          | Configu   | ation: 1  | 0500 1F1F | 8300      | 0085 |    |

|              |          |            |          | coninga   |           | COOF EOOF |           | 0005 |    |

| Exit         | Ct       | rl+Q F     | FF       |           |           |           |           |      |    |

| Checksum:    | 8358     |            |          | OSCCA     | L:        | E         | andGap:   |      |    |

|              |          |            |          |           |           |           |           |      |    |

| Verification | n Succe: | ssful.     |          |           |           |           | Mic       | BOCK | ΗD |

|              |          |            |          |           |           |           |           |      |    |

|              |          |            |          |           |           | VDI       | ) Target- |      |    |

|              |          |            |          |           |           | 5 5       | Check     | 5,0  | \$ |

| Read         | Write    | Verify     | Erase    | Bla       | nk Check  |           | /MCLR     |      |    |

| Program M    | emory    |            |          |           |           |           |           |      |    |

| 🗹 Enabled    | Hex On   | ly 🔽       | Source:  | None (Emp | oty/Erase | d)        |           |      |    |

| 0000         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 0010         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 0020         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 0020         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 0040         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 0050         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 0060         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 0070         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 0080         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 0090         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| OOAO         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF |    |

| 00B0         | FFFF     | FFFF       | FFFF     | FFFF      | FFFF      | FFFF      | FFFF      | FFFF | ~  |

|              |          |            |          |           |           |           |           |      |    |

Figure 3.11: Import Hex File

# 3.4 Summary

This chapter explains about the function of the PIC as the control element, there have four port at the PIC which is porta, portb, portc and last portd. Porta is the special port because it analog input, this port function to interface with the analog signal that produce from the input circuit. Microcode studio is the software that used to write the C language, the user is easier to write using this language compare to the assembly language. This software also converts the Sps file to the Hex file. The programmer PICkit is used to program the PIC, it functions to interface between the PIC and the user computer. The Hex file that produce from the microcode studio is imports to this programmer and transfer to the PIC with press the write button.

# **CHAPTER 4**

# DEVELOPMENT OF AUTOMATIC POWER FACTOR CORRECTION DEVICE

# 4.1 Introduction

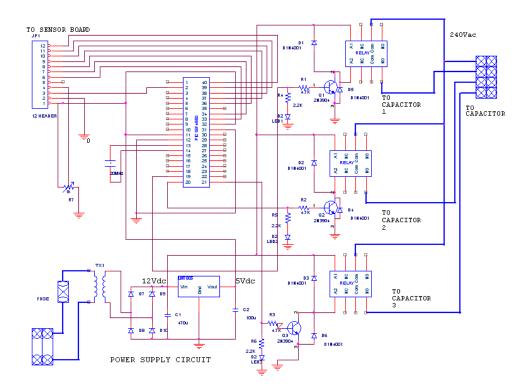

This chapter explains about the hardware design include the power supply circuit, PIC controller circuit, current sensor circuit and driver relays circuit. This chapter also explains about the software design that used to program the microcontroller (PIC) that using the C language, PIC18F4550 and the complete operation of the project system.

# 4.2 **Project Flow**

The project begins with study the equipment in the house that uses the inductive component to operate. The inductive component in the house such as washing machine, air-conditioner and refrigerator, all this component make the power circuit in the system has a power factor. The lagging power factor is happened when this equipment running and also draw more current. To prevent this happen the power factor correction technique is studies, according to the power factor correction the lagging power factor can be improve to unity by adding the capacitor series with equipment. The value of the capacitor is determined depending to the load that running in one time. This can be avoiding from the power factor become leading. The leading power factor is also become a problem, the capacitor become a load and also draw a current. The sensor is used to sense the current in the system, the type of the sensor is Hall-effect current sensor. The rating of this current sensor is up to 50A, which is suitable for house application. This current sensor converts the current signal into voltage form that suitable for PIC. The analog input PIC is used to monitor the current in the system. The microcode studio is the program that used to write the program to the PIC. It converts the pbp file to hex file. This hex file used to program PIC using PICkit programmer. Before program is writing we need to study the features of the PIC that used. After programming is finish the hardware is test using the single phase motor that located in the library.

### 4.3 Proposed Design

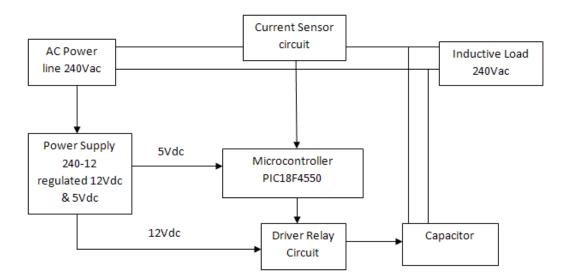

Figure 4.1: Propose Design of APFC

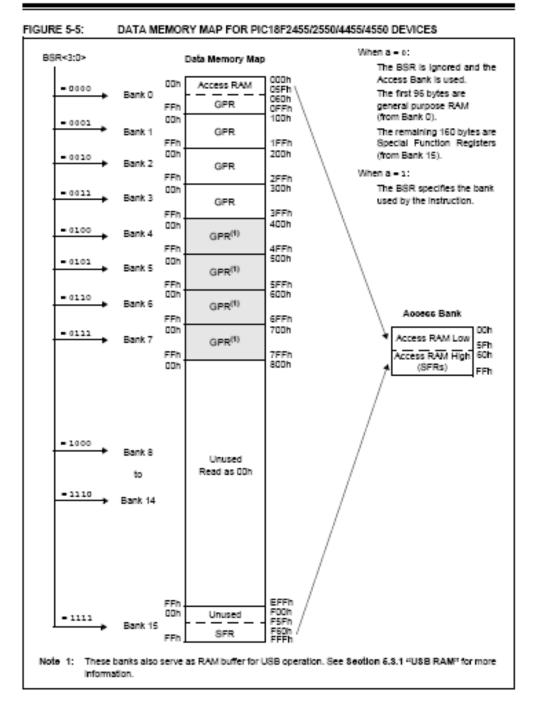

Figure 3.1 above show the proposed design for single phase automatic power factor correction device. It divide into four parts, the first part is power supply. The