## DEVELOPMENT OF AUTO RE-CLOSER EARTH LEAKAGE CIRCUIT BREAKER FOR DOMESTIC APPLIANCES

MUHAMMAD SYAFI'I BIN ALI

UNIVERSITI MALAYSIA PAHANG

# UNIVERSITI MALAYSIA PAHANG

| BORANG PENGESAHAN STATUS TESIS*                                                                                  |                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JUDUL: <u>DEVELOPMENT OF AUTO RE-CLOSER EARTH LEAKAGE</u><br>CIRCUIT BREAKER FOR DOMESTIC APPLIANCES             |                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                                                                                                  | SI PENGAJIAN: <u>2007/2008</u>                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Saya <u>MUHAM</u>                                                                                                | MAD SYAFI'I BIN ALI ( 860827-46-5253)                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                                                                                  | (HURUF BESAR)                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| mengaku membenarkan tesis (<br>Perpustakaan dengan syarat-sy                                                     | Sarjana Muda/ <del>Sarjana</del> / <del>Doktor Falsafah</del> )* ini disimpan di<br>⁄arat kegunaan seperti berikut:                                                                                                                                                                                                                                        |  |  |  |

| 2. Perpustakaan dibenarkan t                                                                                     | iversiti Malaysia Pahang (UMP).<br>membuat salinan untuk tujuan pengajian sahaja.<br>membuat salinan tesis ini sebagai bahan pertukaran antara institusi                                                                                                                                                                                                   |  |  |  |

| SULIT                                                                                                            | (Mengandungi maklumat yang berdarjah keselamatan<br>atau kepentingan Malaysia seperti yang termaktub<br>di dalam AKTA RAHSIA RASMI 1972)                                                                                                                                                                                                                   |  |  |  |

| TERHAD                                                                                                           | (Mengandungi maklumat TERHAD yang telah ditentukan oleh organisasi/badan di mana penyelidikan dijalankan)                                                                                                                                                                                                                                                  |  |  |  |

| $\checkmark$ TIDAK TE                                                                                            | $\checkmark$ TIDAK TERHAD                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                                                                                                  | Disahkan oleh:                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| (TANDATANGAN PENULIS)<br>Alamat Tetap:                                                                           | (TANDATANGAN PENYELIA)                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 265,KG PANTAI MERCHA<br>21610 MARANG,TERENGO<br>TERENGGANU DARUL IN                                              | GANU (Nama Penyelia)                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Tarikh: 23 NOVEMBER 200                                                                                          | <u>)9</u> Tarikh:                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| <ul> <li>** Jika tesis ini<br/>berkuasa/org<br/>dikelaskan s</li> <li>◆ Tesis dimaks<br/>Penyelidikar</li> </ul> | g tidak berkenaan.<br>SULIT atau TERHAD, sila lampirkan surat daripada pihak<br>ganisasi berkenaan dengan menyatakan sekali tempoh tesis ini perlu<br>ebagai atau TERHAD.<br>sudkan sebagai tesis bagi Ijazah doktor Falsafah dan Sarjana secara<br>n, atau disertasi bagi pengajian secara kerja kursus dan<br>n, atau Laporan Projek Sarjana Muda (PSM). |  |  |  |

"I hereby acknowledge that the scope and quality of this thesis is qualified for the award of the Bachelor Degree of Electrical Engineering (Electronics)"

| Signature | :                         |

|-----------|---------------------------|

| Name      | : MOHD REDZUAN BIN AHMAD  |

| Date      | : <u>23 NOVEMBER 2009</u> |

# DEVELOPMENT OF AUTO RE-CLOSER EARTH LEAKAGE CIRCUIT BREAKER FOR DOMESTIC APPLIANCES

## MUHAMMAD SYAFI'I BIN ALI

This thesis is submitted as partial fulfillment of the requirements for the award of the Bachelor of Electrical Engineering (Power System)

Faculty of Electrical & Electronics Engineering Universiti Malaysia Pahang

NOVEMBER, 2009

"All the trademark and copyrights use herein are property of their respective owner. References of information from other sources are quoted accordingly; otherwise the information presented in this report is solely work of the author."

| Signature | :                                 |

|-----------|-----------------------------------|

| Author    | : <u>MUHAMMAD SYAFI'I BIN ALI</u> |

| Date      | : <u>6 NOVEMBER 2009</u>          |

Specially dedicated to my beloved family, sibling, supervisor and those people who giving me constant source of support and encouragement

### ACKNOWLEDGEMENT

First and foremost, I am very grateful to the almighty ALLAH S.W.T for letting me to finish my Final Year Project.

Here, I wish to express my sincere appreciation to my supervisor, En. Mohd Redzuan bin Ahmad for encouragement, guidance, suggestions, critics and friendship throughout finishing this project.

I also thanked to En.Fadhil bin Abbas, En.Rosmadi bin Abdullah and all of the lecturer in FKEE for their accommodation, suggestion and opinion during the project progress in university. In particular, I would like to thank also to thank, staff and technicians, for their cooperation, indirect or directly contribution in finishing my project.

Most importantly, special thank also to my family for their external support when I told them I wanted to continue my education and especially friends for encouraging me done by research. Without their support the ideas could not have been realized.

## ABSTRACT

System protection is the important requirement in electrical power system. The using of protection system can avoid and prevent system from damaged. Electrical energy has caused dangers to human life and machine. Earth leakage circuit breaker (ELCB) is one from protection device that introduced to protect the system. This device is the brain of protection system that monitors input current from power line by it sensor Zero Current Transformer (ZCT), then sending the tripping signal to mechanical switch to disconnected system. ELCB is widely applied by consumer weather is for resident, factory, laboratory and also in power distribution. Because industrial operation requires protection of their Equipment from the lightning, short-circuit and also over-current, so the ELCB will serve the purpose as the protection of their system. This project will focused to improve the ability of current ELCB so that it have ability in identify fault, act accordingly, display the fault(permanent fault and temporary fault) and also re-close it back to normal condition.PIC will execute their instruction when different current from both of current transducer is exceed pre-determine value of sensitivity,100mA. In this project PIC microcontroller will control and operate solid state relay which replacing the application of current mechanical switch.

### ABSTRAK

Sistem perlindungan adalah keperluan penting di dalam sistem kuasa elektrik.Penggunaan sistem perlindungan boleh mencegah dan melindungi sistem dari kerosakan. Tenaga elektrik telah menyebabkan bahaya kepada kehidupan manusia dan mesin.Pemutus litar bocor ke bumi(ELCB) adalah salah satu sistem perlindungan yang diperkenalkan untuk melindungi sistem. Peralatan ini adalah otak bagi sistem perlindungan dimana ia bertindak sebagai pemerhati arus masukan daripada talian kuasa oleh pengesan Zero Pengubah Tanpa Arus (ZCT), seterusnya menghantar isyarat pemutus kepada mekanikal suis untuk memutuskan litar. ELCB digunakan secara menyeluruh oleh pengguna sama ada untuk kediaman, kilang, makmal dan juga pembahagian kuasa. Oleh kerana operasi industri memerlukan perlindungan mesin mereka daripada kilat, litar pintas dan juga lebihan arus, maka ELCB ini akan digunakan bagi tujuan perlindungan kepada sistem mereka.Projek ini menumpukan kepada penambah baikan keupayaan ELCB sedia ada yang mana ELCB berupaya dalam mengenalpasti kesilapan, bertindak sepatutnya, menunjukkan kesilapan dan juga menyambung kembali litar ELCB kepada keadaan asal.PIC akan melaksanakan arahan apabila perbezaan arus antara dua alat pengesan arus melebihi nilai sensitiviti ELCB,100mA. Dalam projek ini,pengawal PIC akan mengawal dan menghidupkan relay keadaan tetap(SSR) yang mana menggantikan penggunaan suis mekanikal yang sedia ada.

# TABLE OF CONTENTS

## CHAPTER

1

## TITLE

## PAGE

| TITLE                  | i    |

|------------------------|------|

| DECLARATION            | ii   |

| DEDICATION             | iv   |

| ACKNOWLEDGEMENTS       | V    |

| ABSTRACT               | vi   |

| ABSTRAK                | vii  |

| TABLE OF CONTENTS      | viii |

| LIST OF TABLES         | xii  |

| LIST OF FIGURES        | xiii |

| LIST OF ABBREVIATIONS  | XV   |

| LIST OF APPENDICES     | xvi  |

| INTRODUCTION           |      |

| 1.1 Project Background | 1    |

| 1.2 Objectives         | 3    |

| 1.3 Scope of Project   | 3    |

| 1.4 Literature Review  | 4    |

| 1.5 Thesis Outline     | 5    |

2

3

# TITLE

| EARTH LEAKAGE CIRCUIT BREAKER |                                             |    |

|-------------------------------|---------------------------------------------|----|

| 2.1                           | Introduction                                | 7  |

| 2.2                           | Earth Leakage Circuit Breaker Device        | 7  |

|                               | 2.2.1 Voltage Earth Leakage Circuit Breaker | 8  |

|                               | 2.2.2 Current Earth Leakage Circuit Breaker | 9  |

| 2.3                           | Problem Of ELCB                             | 9  |

| 2.4                           | Electrical faults                           | 10 |

| 2.5                           | ELCB Features                               | 11 |

| 2.6                           | ELCB Design                                 | 12 |

|                               | 2.6.1 Zero Current Transducer               | 13 |

|                               | 2.6.2 Black Box                             | 13 |

|                               | 2.6.3 Mechanical Switch                     | 14 |

|                               | 2.6.4 Reset Button                          | 14 |

|                               | 2.6.5 High Level Resistor                   | 14 |

| 2.7                           | Operation of ELCB                           | 15 |

| 2.8                           | Summary                                     | 16 |

| CO                            | NTROL ELEMENT CIRCUIT                       |    |

| 3.1                           | Introduction                                | 17 |

| 3.2                           | Microcontroller Feature                     | 18 |

|                               | 3.2.1 PIC18F4550 Features                   | 18 |

|                               | 3.2.2 Input and Output Port Used            | 22 |

|                               | 3.2.3 Crystal oscillator                    | 23 |

| 3.3                           | Software and Hardware Implementation        | 24 |

|                               | 3.3.1 Microcode Studio                      | 24 |

| 3.3.2 CYTRON USB Programmer                    | 25 |

|------------------------------------------------|----|

| 3.3.2.1 Plugging the Microcontroller           | 27 |

| 3.3.2.2 How To Program The PIC Microcontroller | 30 |

|                                                |    |

3.3.3 PIC Driver Circuit Hardware 34

| CHAPTER | TITLE                                     | PAGE       |

|---------|-------------------------------------------|------------|

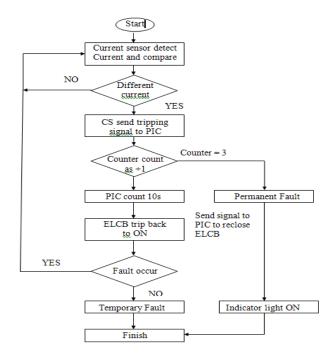

|         | 3.4 Programming Flowchart                 | 35         |

|         | 3.5 Summary                               | 36         |

| 4       | DEVELOPMENT EARTH LEAKAGE CIRCUI          | Т          |

|         | BREAKER WITH AN AUTO RE-CLOSER UNI        | [ <b>T</b> |

|         | 4.1 Introduction                          | 37         |

|         | 4.2 Project Flow                          | 37         |

|         | 4.3 Proposed Design                       | 38         |

|         | 4.4 Stage 1 Circuit                       | 39         |

|         | 4.5 Stage 2 Circuit                       | 40         |

|         | 4.6 Stage 3 Circuit                       | 42         |

|         | 4.6.1 Voltage Regulator                   | 43         |

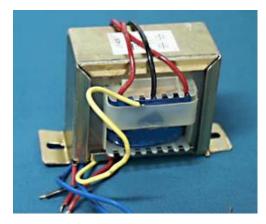

|         | 4.6.2 Centre tap Transformer 240Vac/12Vac | 43         |

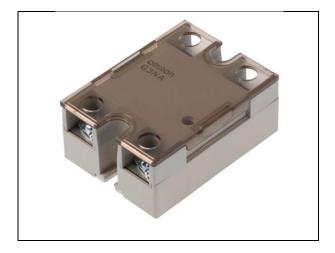

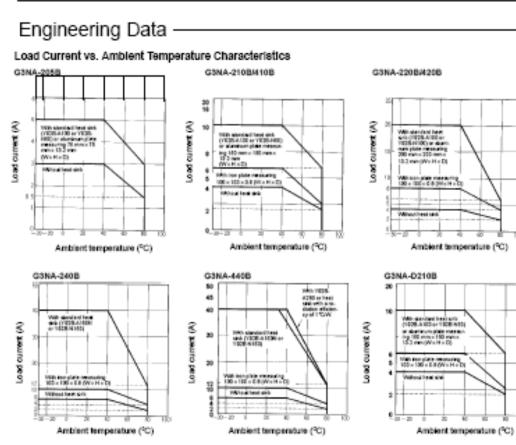

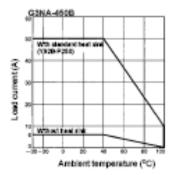

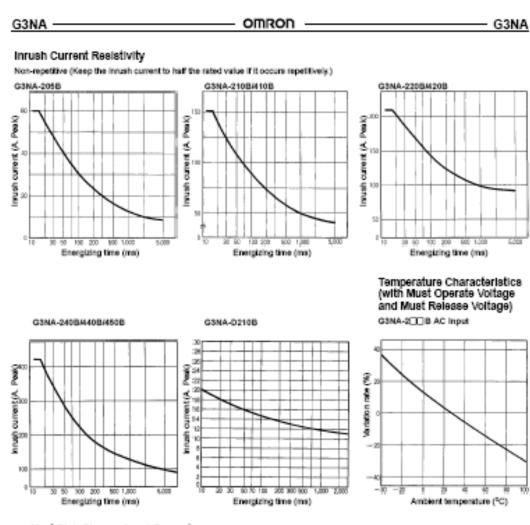

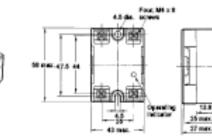

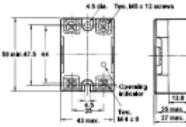

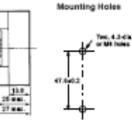

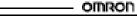

|         | 4.6.3 Solid State Relay                   | 44         |

|         | 4.6.4 Bridge Rectifier                    | 46         |

|         | 4.6.5 One Way Switch                      | 47         |

|         | 4.6.6 Light Emitting Diode (LED)          | 47         |

|         | 4.6.7 Liquid Crystal Display              | 48         |

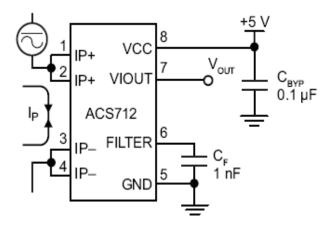

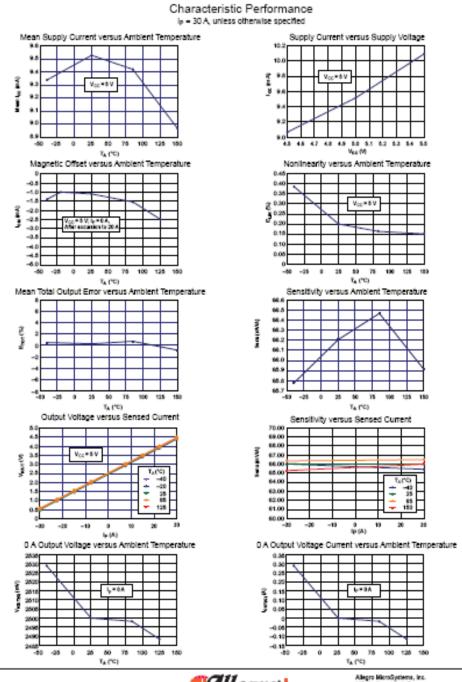

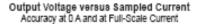

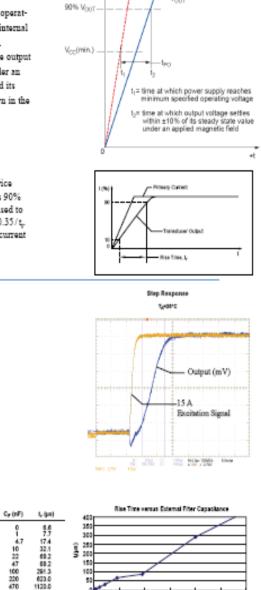

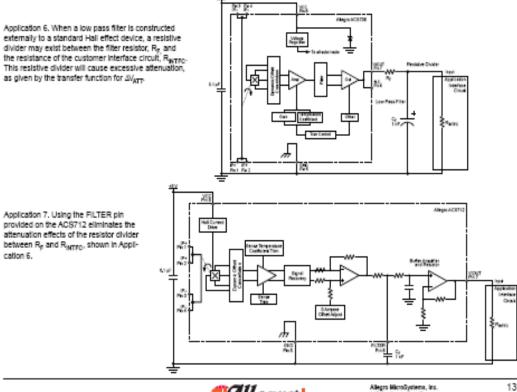

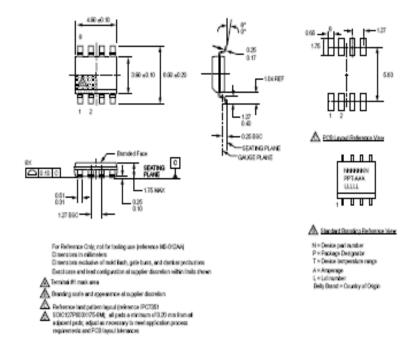

|         | 4.6.8 Half Effect Current Sensor          | 49         |

|         | 4.6.9 Adaptor SMD Current Sensor          | 51         |

|         | 4.6.10Metal Oxide Varistor (MOV)          | 51         |

|         | 4.6.11Fuse                                | 52         |

|         | 4.7 Final Stage Circuit                   | 52         |

|         | 4.8 Flow Chart                            | 53         |

|         | 4.9 Hardware Operation Process            | 54         |

|         | 4.10 Summary                              | 55         |

Х

## 5

# **RESULTS & DISCUSSIONS**

| 5.1 | Introduction                  | 57 |

|-----|-------------------------------|----|

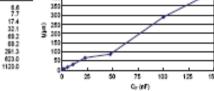

| 5.2 | Measurement of ZCT            | 57 |

| 5.3 | Measurement of Current Sensor | 58 |

| 5.4 | Arrangement of Fault Model    | 62 |

| 5.5 | Project Results               | 62 |

| 5.6 | Discussions                   | 63 |

| 5.7 | Summary                       | 63 |

# 6 CONCLUSIONS & SUGGESTIONS

| 6.1 | Conclusions                   | 64 |

|-----|-------------------------------|----|

| 6.2 | Suggestions                   | 65 |

| 6.3 | Costing and Commercialization | 66 |

|     | 6.3.1 Costing                 | 67 |

|     | 6.3.2 Commercialization       | 69 |

# REFERENCES

Appendices A-H 70-149

# LIST OF TABLES

## TABLE NO.

## TITLE

## PAGE

| 3.4  | PIC18F4550 Features            | 21 |

|------|--------------------------------|----|

| 4.4  | PIC18F4550 pin used detail     | 41 |

| 4.15 | Current Sensor Pin Description | 50 |

| 5.4  | Current Sensor Induce Current  | 60 |

| 6.1  | The cost of components         | 67 |

# LIST OF FIGURES

| FIGURE | TITLE                                        | PAGE |

|--------|----------------------------------------------|------|

| NO.    |                                              |      |

| 2.1    | Home ELCB/RCCB with housing                  | 11   |

| 2.2    | ELCB Structure                               | 12   |

| 2.3    | Earth Leakage Circuit Breaker design         | 13   |

| 2.4    | Earth Leakage Circuit Breaker Operation Flow | 15   |

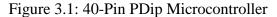

| 3.1    | 40-Pin PDip Microcontroller                  | 19   |

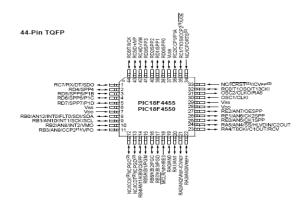

| 3.2    | 44-Pin TQFP Microcontrollers                 | 19   |

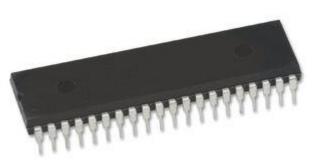

| 3.3    | PIC18F4550                                   | 20   |

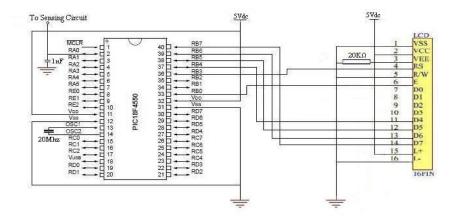

| 3.5    | Interfacing LCD and PIC18F4550               | 22   |

| 3.6    | Crystal Oscillator Basic Instruction         | 23   |

| 3.7    | Basic program Written in Microcode Studio    | 25   |

| 3.8    | UP00A CYTRON USB programmer                  | 27   |

| 3.9    | Flow of Programming Software                 | 35   |

| 4.1    | Basic Operation of Auto Re-closer ELCB       | 39   |

| 4.2    | 5Vdc Power Supply Circuit                    | 40   |

| 4.3    | PIC Microcontroller and LCD circuit          | 41   |

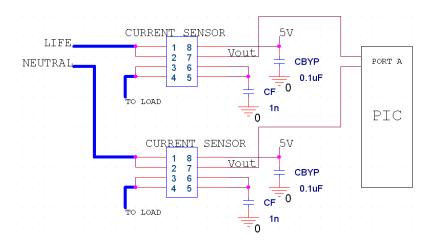

| 4.5    | Sensing Circuit                              | 42   |

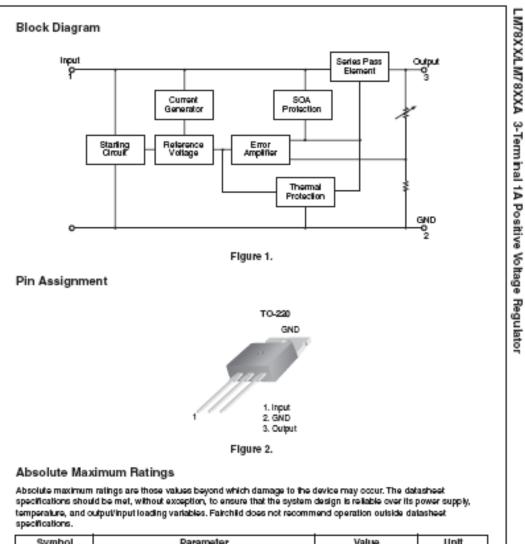

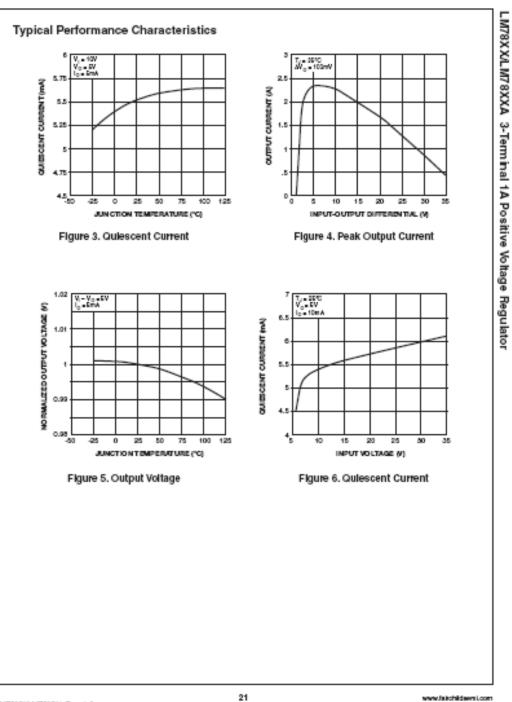

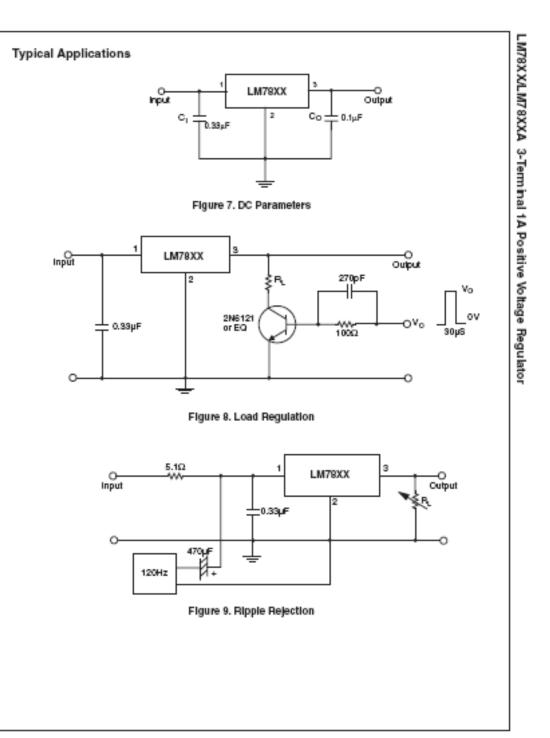

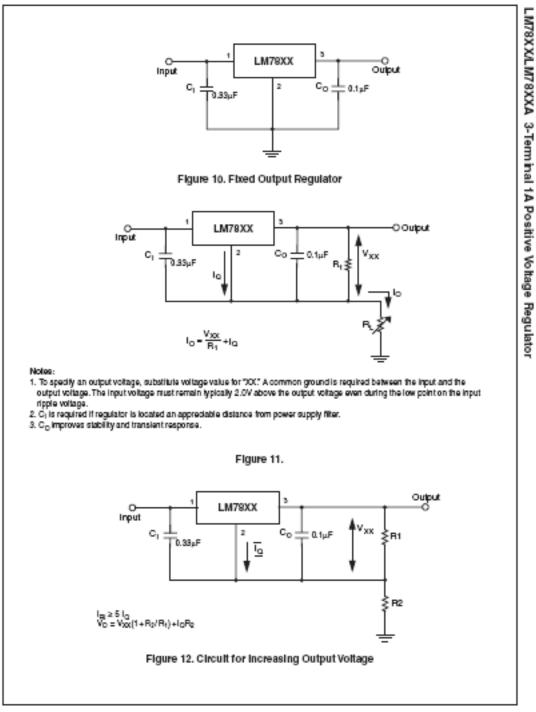

| 4.6    | LM7805 Voltage Regulator                     | 43   |

| 4.7    | Centre Tap Transformer                       | 44   |

| 4.8    | Solid State Relay                            | 45   |

| 4.9    | Bridge Rectifier                             | 46   |

| 4.10   | One Way Switch                               | 47   |

| 4.11   | Light Emitting Diode (LED)                   | 47   |

| •  |   |

|----|---|

| X1 | V |

| NO.  |                                                   |    |

|------|---------------------------------------------------|----|

| 4.12 | Liquid Crystal Display                            | 48 |

| 4.13 | Half Effect Current Sensor                        | 50 |

| 4.14 | Current Sensor Pin Configuration                  | 50 |

| 4.16 | Adaptor SMD                                       | 51 |

| 4.17 | Metal Oxide Varistor                              | 51 |

| 4.18 | Fuse                                              | 52 |

| 4.19 | Final Stage Circuit                               | 52 |

| 4.20 | Flow chart of the system                          | 53 |

| 4.21 | Hardware operation process of Auto Re-Closer ELCB | 55 |

| 5.1  | Operation of ZCT                                  | 58 |

| 5.2  | Connection for Current Sensor Measurement         | 59 |

| 5.3  | Pressure DC Motor 6A                              | 60 |

| 5.4  | Fault Model Arrangement Circuit                   | 62 |

TITLE

FIGURE

# LIST OF ABBREVIATIONS

| AC       | _ | Alternate Current                 |

|----------|---|-----------------------------------|

| ADC      | _ | Analog to Digital Converter       |

| DC       | _ | Direct Current                    |

| Ii       | _ | Input Current                     |

| Io       | _ | Output Current                    |

| LED      | _ | Light Emitting Diode              |

| LCD      | _ | Liquid Crystal Display            |

| PIC      | _ | Programmable Intelligent Computer |

| SSR      | _ | Solid State Relay                 |

| V        | _ | Voltage                           |

| $V_{in}$ | _ | Input Voltage                     |

| Vo       | _ | Output Voltage                    |

| ZCT      | _ | Zero phase Current Transformer    |

| Ω        | _ | Ohm                               |

# LIST OF APPENDICES

## APPENDIX

# TITLE

## PAGE

| А | PIC18F4550 Microcontroller, Addressing Modes, and | 71  |

|---|---------------------------------------------------|-----|

|   | Instruction Set                                   |     |

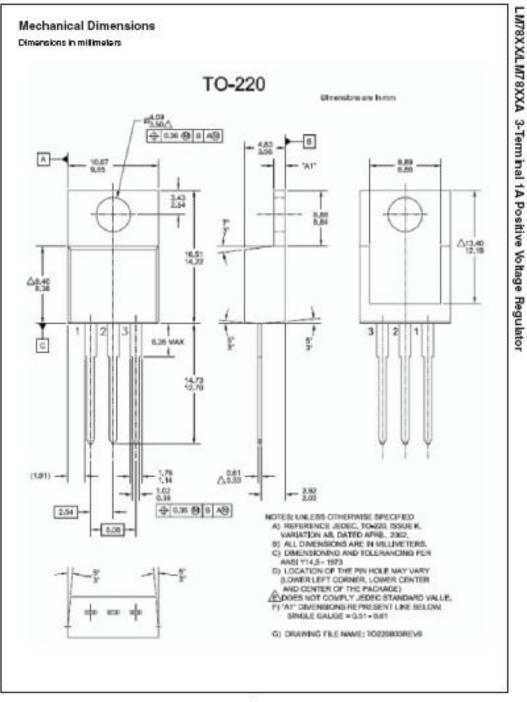

| В | LM7805 Voltage Regulator Datasheet                | 103 |

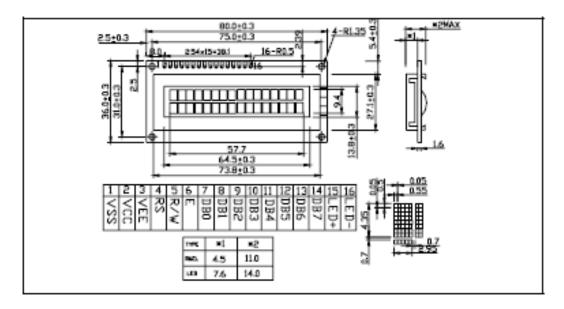

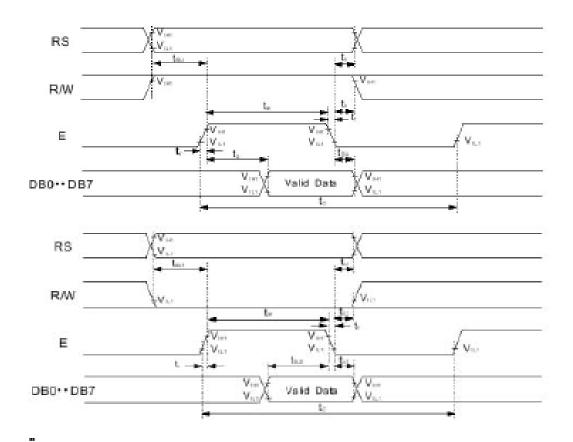

| С | JHD162A Series Datasheet                          | 112 |

| D | Omron G3NA-220B Solid State Relay                 | 118 |

| Е | Half-Effect Linear Current Sensor Datasheet       | 126 |

| F | AR-ELCB Programming                               | 141 |

| G | AR-ELCB Hardware Picture                          | 146 |

| Η | Biodata of the Author                             | 148 |

## **CHAPTER 1**

## INTRODUCTION

#### 1.1 **Project Background**

The idea of the project is refer on the problems and weakness of ELCB. Nowadays, ELCB that available in market is controlled manually and cannot turn ON automatically. Beside that, ELCB today cannot differentiate between permanent fault and temporary fault. According from that problem, it bring the problem to consumer who were not at home and do not understand the danger of permanent fault if the kind of fault happen.

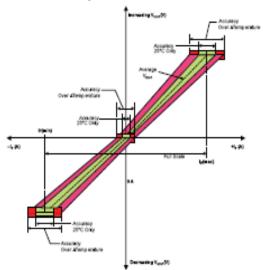

This project s focused in the development and new design a unit of auto re-closer earth leakage circuit breaker (AR-ELCB).The main purpose of this project is more to upgrade the ability of ELCB. Auto re-closer ELCB can differentiate and act differently with different type of fault. The concept is easy to understand which if fault happen, ELCB will trip automatically and disconnect the circuit. If temporary fault lie lighting happen, ELCB will close back automatically and circuit is connected back in interval time that has been set. If permanent fault like electrical, electronic device or short circuit is detected, ELCB will eternally trip and permanent faulty lamp/buzzer will function as alert to consumer. When fault root cause is removed, the consumer need to manually switch ON the ELCB and that case is just especially for permanent fault. In this project, I have planned to use the programmable interfacing controller (PIC) as control element and can make system more efficient and accurate. To get new auto re-closer ELCB, we must combined control element and old ELCB. In this combination, we must consider all power and source value for voltage and currents of each device and for it, we must know to design the new additional circuit to fix the voltage and currents which the value is suitable to interface with control element and could work together.

### 1.2 **Objective**

The objectives of this project are:

- i. To develop the auto re-closer earth leakage circuit breaker(AR-ELCB)

- ii. To improve the ability of earth leakage circuit breaker(ELCB) unit

- iii. To notify the type of fault whether temporary or permanent fault

## **1.3** Scope of Project

The scopes of this project are:

- i. Studied and explored about all the function of ELCB

- ii. This project focused to modify and improve the ability of ELCB to assign whether permanent or temporary fault.

- iii. Different output on the AR-ELCB device depend on the fault detected

- iv. Development programmable interfacing controller (PIC) application as control element of circuit

### **1.4.** Literature Review

There are two types of ELCB, the voltage operated device and the differential current operated device. For the convenience of this article only (and at the risk of causing even more confusion) I will refer to these as vELCB and iELCB. vELCBs were first introduced about sixty years ago and iELCBs were first introduced about forty years ago.

vELCB is a voltage operated circuit breaker, the device will function when the Current passes through the ELCB. vELCB contains relay loop which it being connected to the metallic load body at one end and it is connected to ground wire at the other end. If the voltage of the load body is rise which could cause the difference between earth and load body voltage, the danger of electric shock will occur. This voltage difference will produce an electric current from the load metallic body passes the relay loop and to earth. When voltage on the load metallic body raised to the danger level which exceed to 50Volt, the flowing current through relay loop could move the relay contact by disconnecting the supply current to avoid from any danger electric shock.

iELCB is current operated circuit breaker. The device will function with when the Current passes through ELCB. This current admitted to current transform device and on the load. Current from the load also admitted again to transform device. In normal state, total current applied to load is equal with total current out of the load. Because of the balance of in and out of current, it does not affect the current transform device. If there is any earth current leakage caused by earth damage, then the in and out current.[1]

In Europe, where electromechanical ELCB's are used almost exclusively, the question of reliability of installed ELCB's has become a subject of major concern and attention. The popular hype regarding perceived reliability of electronic components was not sufficient to prevent the major South African manufacturer, some five years ago

from changing their entire ELCB range from electromechanical to electronic technology ELCB's. The improvements in reliability that resulted from this decision are complemented by their freedom from safety performance limitations often found in lower specification electromechanical earth leakage circuit breakers. The pioneering South African developments in sensitive earth leakage protection originally used magnetic amplifier technologies to reach the required sensitive residual current tripping levels necessary for shock hazard protection in human beings. Respite the lack of maturity in electronic components during those early days, a move was made away from magnetic amplifiers to solid state electronic technology in order to overcome the identified problems of noise, size and cost. [2]

This paper traced the development of earth leakage circuit breaker and indicated the very real need for such protection against both shock hazard and fire risk. Largely influenced by the highly sensational issues of the effects of electricity on the human body. Most publicity and media coverage relating to earth circuit breaker has, quite naturally concentrated on shock hazard protection and the related life saving capabilities of the device. it is only, that understanding prevails in regard to the dramatic reduction of potential fire hazard in premises that have been fitted with sensitive earth leakage protection.[3]

Most problems in discrete relay schemes is that of contact racing and timing tolerance on pick-up and drop-off of the various relay elements within the schemes. To overcome this problem, it often necessary to add additional element, or very selective in the type relay used. Beside that, lightning never strike the same place twice. This means that in any one auto-reclose sequence several different types of fault could be present [4]

### 1.5. Report outline

Chapter 1 will explain about the early process before begin that project. It include the project background, objectives, scope of project and literature review. Project background is about ELCB today altogether with their problem. Objectives and scope of project is target to resolve that problem. Then, before we start that project, literature review about that device is most important to get more data and information about that device.

Chapter 2 will explain detail definition of ELCB. From that, we can find all information about that device. Beside that, we can see two type of ELCB available in market which has different characteristic and method operation. According from analytical about that device, this chapter is include the problem of ELCB with more detail.

From chapter 3, we will see the construction inside the ELCB device. It include component of Zero current transducer, black box, mechanical switch, reset button and high level resistor. From combination of that component, it will integrated together to perform ELCB operation.

Chapter 4 will explain about the development auto re-closer ELCB. It include project flow how to start that project. Other planning is proposed design circuit to replaced old circuit of ELCB. After that, we can see the flow chart how that new device is operate and how PIC application of PIC make the system more reliable and effective.

At chapter 5, it will explain about expected result and conclusion about early planning along produce the new device ELCB. From expected result, we can conclude whether the project will be successful or not.

Finally at end of chapter 6, this chapter will explain about costing and commercialization. We can estimate the cost for design one unit of auto re-closer earth leakage circuit breaker

## **CHAPTER 2**

#### EARTH LEAKAGE CIRCUIT BREAKER

### 2.1 Introduction

This chapter describe about nowadays earth leakage circuit breaker that used in 240Vac for domestic appliances. Before start any project about that device, it is important to analyze and understand the basic of the ELCB device and know how the device work actually. To achieve the objective for this chapter, the research of earth leakage circuit breaker is done by exploring the 240Vac ELCB that normally used for domestic appliances.

The objectives of this chapter are:

- i. To know the system of basic Earth Leakage Circuit Breaker

- ii. To understand how the device work

- iii. To analyze the problem of ELCB

## 2.2. Earth Leakage Circuit Breaker (ELCB) Device

An Earth Leakage Breaker (ELCB) is devices that detect leakage current and protect consumer from electric shock if leakage current occurred. the device is used to directly detect current leaking to earth from and installation and cut the power. For example, if any fault happens, ELCB will detect and trip, so the electrical supply is disconnected.

ELCB must fitted in main switchboard in every home to prevent electric accident and this is very effective way. If we using electric water heater equipment, additional ELCB need to be specially fixed in order to monitor the heater water. This precaution is god in ensuring your house safety.

There are two type of ELCB mostly used and available in market. That type is voltage earth leakage circuit breaker (vELCB) and current earth leakage circuit breaker. Few years ago, the was vELCB is mostly used, but its utilization was currently had been abolished because it was less effective. Then, iELCB is introduced to replaced vELCB immediately. The iELCB is more sensitive to any damaged in assembly and electrical appliances at domestic

#### 2.2.1 Voltage Earth Leakage Circuit Breaker (vELCB)

vELCB is a voltage operated circuit breaker, the device will function when the current passes through the ELCB. The principle of operation of the vELCB is as follows. Under normal conditions the closed contacts of the vELCB feed the supply current to the load. The load is protected by a metal frame, such as in an electric cooker. The vELCB also has a relay coil, one end of which is connected to the metal frame and one end connected directly to ground. A shock risk will arise if a breakdown in the insulation occurs in the load which causes the metal frame to rise to a voltage above earth. A resultant current will flow from the metalwork through the relay coil to earth and when the frame voltage reaches a dangerous level, e.g. 50 volts, the current flowing through

the relay coil will be sufficient to activate the relay thereby causing opening of the supply contacts and removal of the shock risk.

As can be seen from the above description, this type of ELCB is essentially a voltage sensing device intended to detect dangerous touch voltages. The level of shock protection provided by the vELCB was somewhat limited as these devices would not provide shock protection in the event of direct contact with a live part. An additional problem with the vELCB was its tendency to be tripped by earth currents originating in other installation

#### 2.2.2 Current Earth Leakage Circuit Breaker (iELCB)

The iELCB was introduced in the late 1950's. It operates on the following principle. Under normal conditions the closed contacts of the iELCB feed the supply current to the load. The load conductors are passed through a current transformer (CT), a doughnut shaped device. The load conductors act as primary windings of the transformer. The CT is fitted with a secondary winding. Under normal conditions, the total current flowing from the supply to the load will be the same as the total current flowing back to the supply from the load. As the current in both directions is equal but opposite, it has no effect on the CT. However, if some current flows to earth after the iELCB, possibly due to an earth fault, the current flowing to the load and from the load will be different. This differential current will cause a resultant output from the CT. This output is detected and if above a predetermined safe level, it will cause the iELCB to trip and disconnect the supply from the load.

## 2.3 **Problem of ELCB**

Earth leakage circuit breaker is one type of device used especially as a protection device. The main function of ELCB is to cut off the electrical supply when the fault is detected. But, the disadvantage for ELCB device nowadays, it cannot turn on itself and back to normally condition if fault occurred. To connect the electrical supply back, the consumer must turn on manually. But, if any person not in home, the electrical supply is remain in turn off condition.

Beside that, ELCB cannot recognize fault whether temporary fault or permanent fault. The principles of operation just to trip and disconnect circuit, but it actually not recognize the type of fault. The ELCB will trip depend on temporary fault only and for permanent fault problem, there is no output is created to ensuring the consumer safety.

The device is also cannot act differentially for these two types of fault. ELCB device just detect and trip depend on temporary fault only. If permanent fault happen, the consumer know the root of that problem and can see the reaction from ELCB. But in permanent fault case, there is no output showed at ELCB, so it can create the danger like electrical shock and other problem to consumer.

### 2.4 Electrical Fault

A fault is any abnormal situation in an electrical system in which the electrical current may or may not flow through the intended parts. Also equipment failure attributable to some defect in a circuit (loose connection or insulation failure or short circuit etc.). Types of faults in a distribution network circuit are:

i) Over-load

- ii) Faults on electrical equipments

- iii) Transmission lines faults

Over-load faults are caused by the unexpected increasing of loads. Faults on electrical equipments are caused by lightning, insulator breakage, Product design which is out of specification and Improper installations of equipments.

Most faults on transmission lines of 100kV and higher are caused by lightning, which results in the flash over of insulators. Transmission lines faults are caused by, lightning, storm, fallen trees, Snow. One of the temporary fault, is a fault lightning. Where example of permanent fault is faults on electrical equipment.

#### **2.5 ELCB Features**

Figure 2.1: Home ELCB/RCCB with housing

Figure 2.2: ELCB Structure

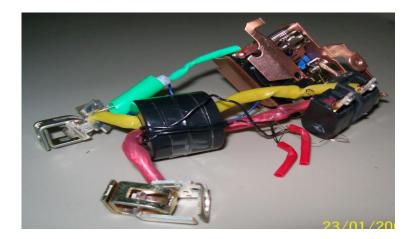

The figure 3.1 shows the ELCB home with the housing. figure 3.2 show the basic construction inside ELCB.After separate that device, we can see all component inside ELCB include ZCT, blackbox, result button. Three cable connection cable are labeled with red, yellow and green to show the connection life, neutral and earth inside ELCB.

### 2.6 ELCB Design

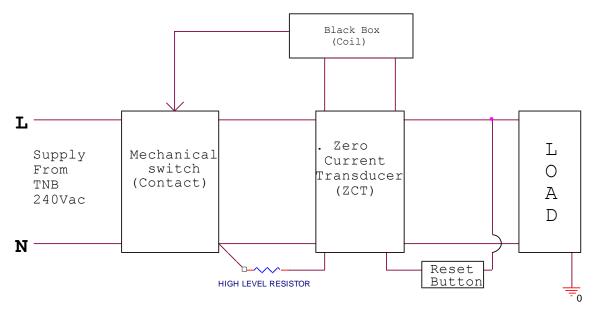

The earth leakage circuit breaker consist the black box (coil),mechanical switch, zero current transducer, high level resistor and reset button. Every component has different operation and it combined in one circuit to create ELCB device. With supply from TNB 240Vac, those devices flow through every component and lastly go to load.

Figure 2.3: Earth Leakage Circuit Breaker design

#### 2.6.1. Zero Transducer Current (ZCT)

Zero current transformers are used to detect unbalance current and send signal to black box. In unbalance current condition, induced current is produced and it flow from ZCT to other device in system.

### 2.6.2. Black Box

Black box in ELCB consist a coil. The function of black box is received the signal (induced current) from zero current transducer. The coil in black box will activate the mechanical switch after received the minimum current level 100mA from ZCT.

## 2.6.3. Mechanical switch

Mechanical switch act as contact of black box and it used especially to cut off the power and disconnect circuit immediately. Mechanical switch is directly connect with coil which if coil is activated, it will removed the mechanical switch.

#### 2.6.4. Reset Button

The main function of the reset button is to reset back the device to initial condition. It is also used as a point to detect whether the device in good condition or damage.

### 2.6.5. High Level Resistor

The high level resistor is used to limit the current flowing through its line when reset button is pushed. When unbalance current happen, that device will fully function to control the flow of current.

## 2.7 Operation of ELCB

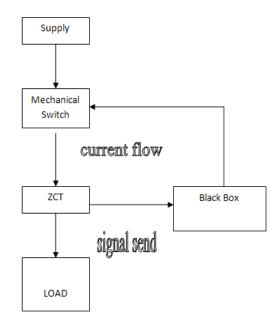

Figure 2.4: Earth Leakage Circuit Breaker Operation Flow

This flow showed the operation of ELCB during fault happen. In normal condition, mechanical switch is already closed and give permission to supply through ELCB and directly go to load. When the fault occurred, the unbalance phenomena are detected by ZCT in ELCB. So the induced current will happened at ZCT. Induced current that reached the min value level will send to black box and automatically will activate the coil in black box. Then, when the coil is activated, it will remove the contact of mechanical switch to trigger and cut off the supply instantaneously. If the condition back to normal and has no fault detected, reset button is pushed to connect the electrical flow.

## 2.8 Summary

ELCB is an important device in electrical system and it available with two type. iELCB and vELCB is the kind of type but both device is used for protection device for electrical equipment and protect consumer from danger and hazard. Both device has different operation to detect the current leakage and different characteristic. The main purpose of ELCB is to cut-off the power when fault occurred. To make that ELCB device more effective, ELCB must be able to act differentially following the kind of faulty, so it can improve ELCB ability.

### **CHAPTER 3**

#### **CONTROL ELEMENT CIRCUIT**

### 3.1 Introduction

Control element circuit is the main controller for overall of the system. In this project, it focused on using PIC18F4550 microcontroller as brain element for our system. Earlier project, there is 3 type of PIC is considered to used in our project as PIC18F2255,PIC18F4455 and PIC 18F4550.But in final decision,PIC18F4550 is choosed based on their feature and it mostly used in many project before. PIC18F4550 microcontrollers use flash technology to allow rapid erasing and reprogramming to speed program debugging. PIC18F4550 offer twelve different oscillator options, allowing users a wide range of choices in developing application hardware. With the click of the mouse in the programming software, the flash PIC micro MCU can be instantly erased and then reprogrammed again and again. PIC18F4550 have large amounts of RAM memory for buffering and Enhanced Flash program memory thus make it ideal for embedded control and monitoring applications that require periodic connection with a (legacy free) personal computer via USB for data upload or download and firmware updates. Programming the PIC18F4550 is done by using C-language. Besides, Microcode Studio software has been used to write the programming coding of the PIC. Finally compile this type of programming language, the use of PIC Basic Compiler have been used.

#### **3.2 PIC Microcontroller Feature**

PIC is a family of Harvard architecture microcontrollers made by Microchip Technology, derived from the PIC1640 originally developed by General Instrument's Microelectronics Division. The name PIC initially referred to "Programmable Interface Controller", but shortly thereafter was renamed "Programmable Intelligent Computer".

PICs are popular with developers and hobbyists alike due to their low cost, wide availability, large user base, extensive collection of application notes, availability of low cost or free development tools, and serial programming (and reprogramming with flash memory) capability.

PIC microcontrollers are frequently used in automatically controlled products and devices, such as automobile engine control systems, remote controls, office machines, appliances, power tools, and toys. By reducing the size, cost, and power consumption compared to a design using a separate microprocessor, memory, and input/output devices, microcontrollers make it economical to electronically control many more electrical and mechanical devices.

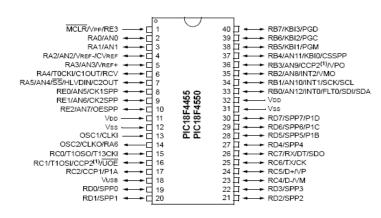

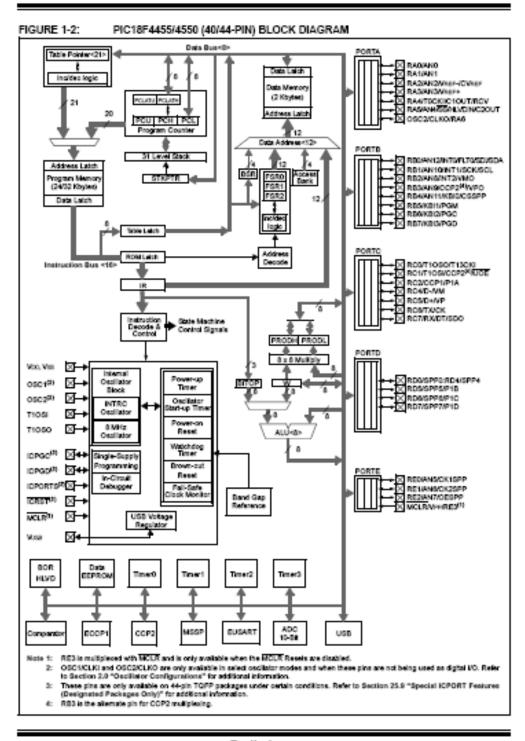

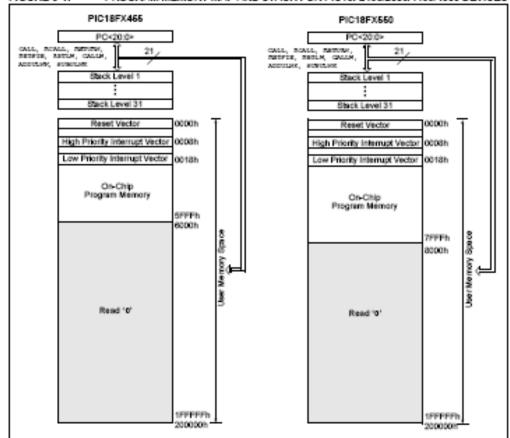

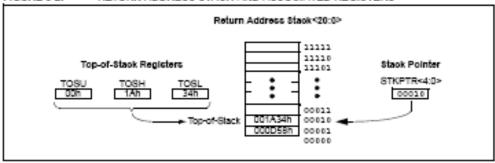

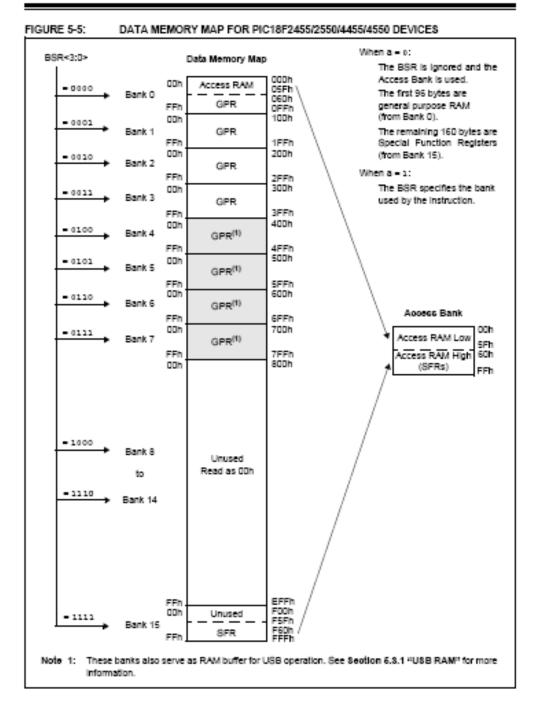

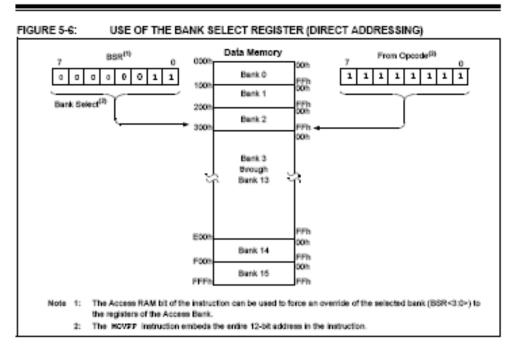

#### 3.2.1 PIC 18F4550

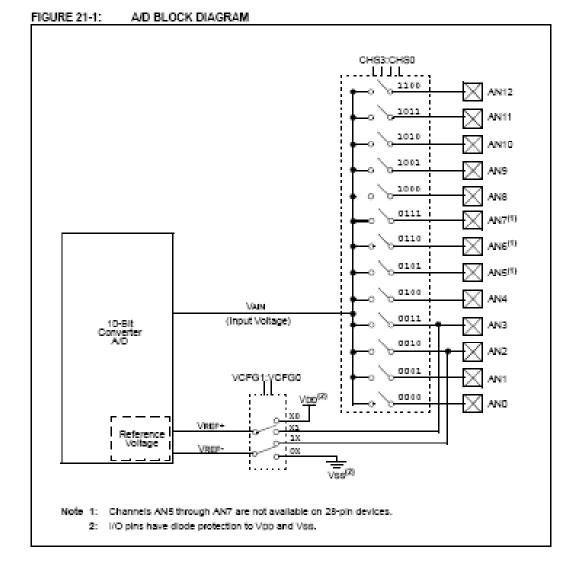

In this project, the PIC18F4550 is choose to used as brain for our system, thus it can make system more reliable and beside high computational performance. This PIC is attached with 40 pin and every pin has different function. In this PIC, there are 4 type port available like port A, port B, port C and port D. Port A is design especially with ADC (analog digital converter). The function of ADC is to convert analog form to digital form. It actually used to interface with PIC which PIC can operate if they understand the information given in digital signal form. In PIC reader, PIC just can

assign the logic signal whether logic 0 (0Vdc) logic 1 (5Vdc). From the PIC port configuration, this port can be set whether be output or input depend on the user programming. To set the port, user must be decide early and make programming to choose whether used port as input or output, thus PIC can understand and can perform their instruction. Beside that, the crystal oscillator is used to generate the frequency (pulse form) to the PIC. the relationship oscillator and PIC showed if high value oscillator generate, PIC will execute the instruction more faster and in this project, oscillator 20MHz is used to generate the pulse form. The figure 3.1 and 3.2 show the two type of PIC18F4550 that usually used in other project. The number of pin is different and method installation for pin TQFP microcontroller are more difficult to compare with PDIP microcontroller.

40-Pin PDIP

# Figure 3.2: 44-Pin TQFP Microcontrollers

Figure 3.3: PIC18F4550

Below is the detail information about PIC 18F4550 features

- 8BIT FLASH MCU, 18F4550, DIP40

- Series:PIC18F

- Memory Size, Flash:32KB

- EEPROM Memory Size:256Byte

- RAM Memory Size:2048Byte

- No of I/O Lines:35

- No. of ADC Inputs:13

- No. of Timers:4

- No. of PWM Channels:5

- Clock Frequency:48MHz

- Interface Type: EUSART, I2C, SPI, SPP, USB

- Voltage, Supply Min:4.2V

- Voltage, Supply Max:5.5V

- Termination Type: Through Hole

- Case Style: DIP

- No. of Pins:40

- Operating Temperature Range:-40°C to +85°C

- Max Operating Temperature:85°C

- Min Temperature Operating:-40°C

- Base Number:18

- Bits, Number In Timer:16

- Bits, Number in ADC:10

# Table 3.4: PIC18F4550 Features

| Pin Name                                                                 | Pin<br>Number<br>PDIP,<br>SOIC | Pin<br>Type | Buffer<br>Type                      | Description                                                                                                                                                                                               |

|--------------------------------------------------------------------------|--------------------------------|-------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLR/VPP/RE3<br>MCLR                                                     | 1                              | I           | ST                                  | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.                                                                     |

| VPP<br>RE3                                                               |                                | P<br>I      | ST                                  | Programming voltage input.<br>Digital input.                                                                                                                                                              |

| OSC1/CLKI<br>OSC1<br>CLKI                                                | 9                              | 1           | Analog<br>Analog                    | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>External clock source input. Always associated with pin<br>function OSC1. (See OSC2/CLKO pin.) |

| OSC2/CLKO/RA6<br>OSC2                                                    | 10                             | 0           | -                                   | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or resonator in<br>Crystal Oscillator mode.                                                                         |

| CLKO                                                                     |                                | 0           | -                                   | In select modes, OSC2 pin outputs CLKO which has 1/4 the<br>frequency of OSC1 and denotes the instruction cycle rate.                                                                                     |

| RA6                                                                      |                                | ₽O          | TTL                                 | General purpose I/O pin.                                                                                                                                                                                  |

|                                                                          |                                |             |                                     | PORTA is a bidirectional I/O port.                                                                                                                                                                        |

| RA0/AN0<br>RA0<br>AN0                                                    | 2                              | ⊮o<br>I     | TTL<br>Analog                       | Digital I/O.<br>Analog input 0.                                                                                                                                                                           |

| RA1/AN1<br>RA1                                                           | 3                              | Iю          | TTL                                 | Digital I/O.                                                                                                                                                                                              |

| AN1                                                                      |                                | I           | Analog                              | Analog input 1.                                                                                                                                                                                           |

| RA2/AN2/VREF-/CVREF<br>RA2<br>AN2<br>VREF-                               | 4                              | 10 0        | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (low) input.                                                                                                                                     |

| CVREF                                                                    | -                              | 0           | Analog                              | Analog comparator reference output.                                                                                                                                                                       |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+                                     | 5                              | ⊮0<br> <br> | TTL<br>Analog<br>Analog             | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (high) input.                                                                                                                                    |

| RA4/T0CKI/C1OUT/RCV<br>RA4<br>T0CKI<br>C1OUT<br>RCV                      | 6                              | ⊮0<br>- 0 - | ST<br>ST<br>TTL                     | Digital I/O.<br>Timer0 external clock input.<br>Comparator 1 output.<br>External USB transectiver RCV input.                                                                                              |

| RA5/AN4/SS/<br>HLVDIN/C2OUT<br>RA5<br>AN4<br>33<br>HLVDN<br>C2CUT<br>RA6 | 7                              | S0          | TTI<br>Aralog<br>TTL<br>Aralog<br>— | Digital I/O<br>Analog input 4.<br>OPI slave select input.<br>High/Low-Voltage Detect input.<br>Comparator 2 output.<br>See the OSC2/CLKO/RA6 pin.                                                         |

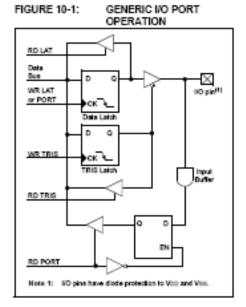

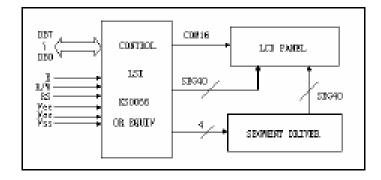

### 3.2.2 Input and Output Port Used

According from circuit project, the output PIC is LCD and solid state relay and the PIC input is signal/data from op-amp LM358.Port A is set with input which port A is special pin with ADC attachment and it desired to send logic signal digital to PIC. The source of port A is come from op-amp which that device convert current to voltage and from there, it directly give signal to PIC whether logic low(0) or logic high(1).Meanwhile for port C, it set with output connected to LCD and solid state relay. If fault occurred, PIC will send signal to operate the solid state relay which it will trigger switch off and automatically disconnected the circuit. Then, at the same time PIC will send output signal to LCD to display what happen to user. Pin 13 and pin 14 is built in to directly connect with crystal oscillator 20 MHz. Beside that, pin 11 and 32 will connected together as Vcc that act as supply to on the PIC. Lastly, pin 12 and 31 is connected together to flow go directly to ground.

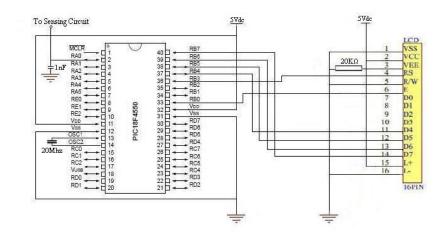

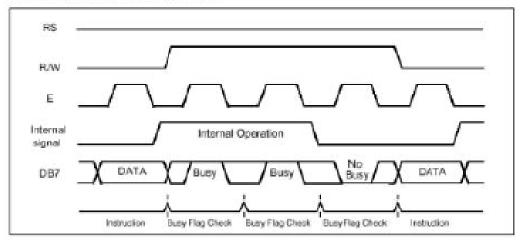

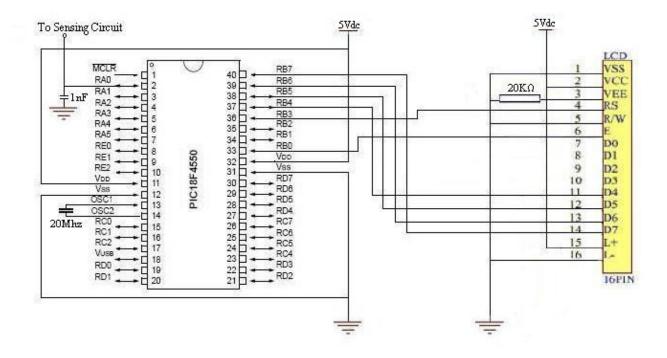

Figure 3.5: Interfacing LCD and PIC18F4550

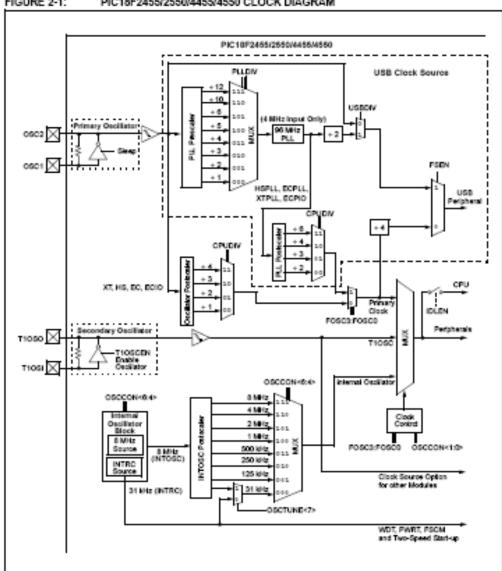

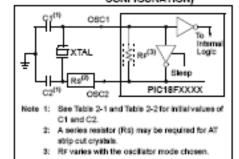

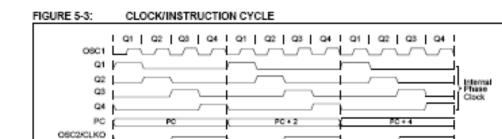

### 3.2.3 Crystal Oscillator

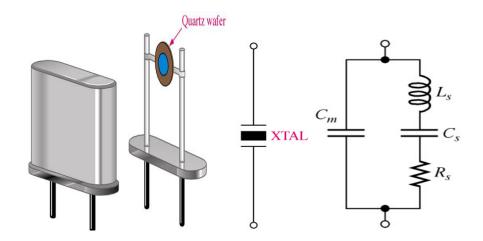

A crystal oscillator is electronic circuit device that designed to generate electrical signal with accurate frequency. It work using mechanical resonance of a vibrating crystal of piezoelectric material to create an electrical signal. The using of precise frequency is to keep track of time, to provide a stable clock signal for digital integrated circuit, and to stabilize frequencies for radio transmitter and receivers. The most common type of piezoelectric resonator used is the quartz crystal, so oscillator circuits designed around them were called "crystal oscillators". A crystal has a natural frequency of resonance. Build in with quartz material, it can be shaped or cut to have a certain frequency. When a crystal of quartz is properly cut and mounted, it can be made to distort in an electric field by applying a voltage to an electrode near or on the crystal. This property is known as piezoelectricity. When the field is removed, the quartz will generate an electric field as it returns to its previous shape, and this can generate a voltage. The result is that a quartz crystal behaves like a circuit composed of an inductor, capacitor and resistor, with a precise resonant frequency. In this project, crystal oscillator 20 MHz is choosed to interface with PIC. The 20MHZ or more below than that is suitable to generate the precise frequency, so the PIC can operate better.

Figure 3.6: Crystal Oscillator Basic Instruction

## 3.3 Software and Hardware Implementation

This section will discuss about software which has been implemented in this project which are PicBasic Pro Compilers (MicroCode Studio) for programming PIC18F4550, OrCAD Capture CIS for designing the circuit and PicBasic Pro Compilers (Micro Code Studio) for the programming and also Cytron Programmer for writing the programming language into the PICF4550.

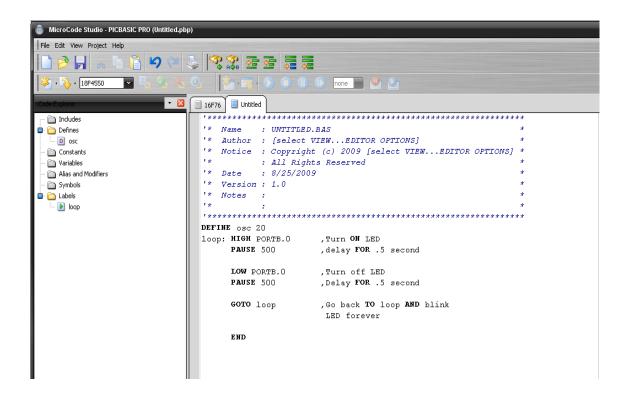

#### 3.3.1 Microcode Studio

Microsoft studio is software that has been used to convert source file to HEX file code and act as assembler. To interface with PIC, all the source file must be converted to HEX file because PIC just can read and understand the hex file only.

MicroCode Studio is a powerful, visual Integrated Development Environment (IDE) with In Circuit Debugging (ICD) capability designed specifically for microEngineering Labs PICBasic PRO compiler. The code explorer allows you to automatically jump to include files, defines, constants, variables, aliases and modifiers, symbols and labels that are contained within your source code. It's easy to set up your compiler, assembler and programmer options or you can let MicroCode Studio do it for you with its built in autosearch feature. Compilation and assembler errors can easily be identified and corrected using the error results window. MicroCode Studio even comes with a serial communications window.

Figure 3.7: Basic program Written in Microcode Studio

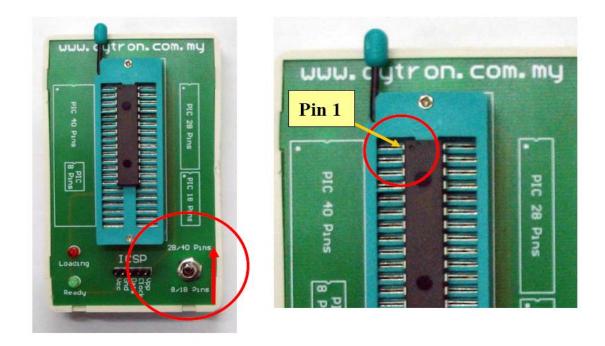

#### 3.3.2 CYTRON USB Programmer

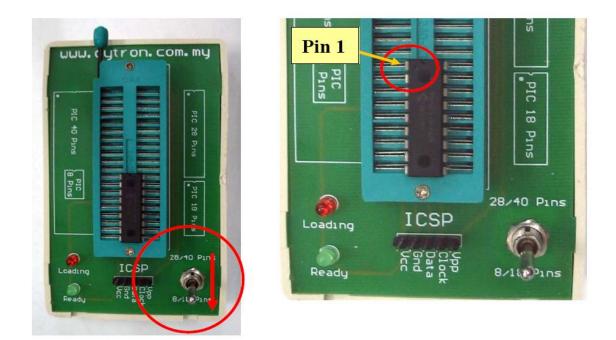

In this project, UP00A CYTRON USB programmer is used and it attached with PIC programmer and winpic800. It fully functions as burner device and both of software and hardware act as medium to write the c- language in the PIC18F4550. CYTRON USB programmer UP00A provides an effective and low-cost solution in developing wide range of Microchip PIC microcontroller. That device has not using external supply, just directly connect to USB desktop PC or laptop and we can start write the program.

UP00A CYTRON USB programmer is equipped with 40 pin universal ZIF socket that provide a comfort and easy operation during plug in and plug out the chip. Besides ZIF socket, header pin for ICSP (In-Circuit Serial Programming) also provided.

This header pin can be used for in-circuit programming and to program the PIC with different socket which is not supported by the ZIF-socket. That device is comes with 28/40 pin and 8/18 pin and it used depend on the number of IC pins. Other than that, that device complete with LED that will showed the loading and ready signal. The ready signal will ON when the USB programmer is plugged in onto the USB computer. Then, during that data is burner to PIC, the loading lamp will ON and it will show how the device work completely.

### Features:

- Designed for Intel based PC, DO NOT support AMD based system.

- Fast, reliable and low-cost.

- Do not support Window Vista

- Require USB port only.

- Can be used in desktop PC and laptop.

- ZIF socket and ICSP header pin are prepared.

- The programmer can be used for Windows Me/NT/2000/XP.

- 12F, 16F and 18F PIC MCU are supported.

- USB cable, user manual and programming software are provided.

Package Including:

- UP00A Programmer Unit

- USB Cable

- User Manual and Programming software in CD Rom

- 6 months warranty against factory defect only

Figure 3.8: UP00A CYTRON USB programmer

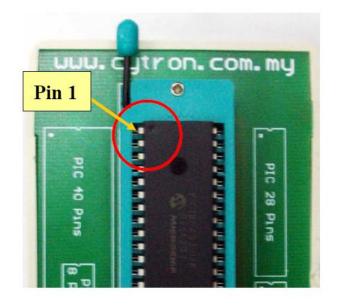

# **3.3.2.1 Plugging The Microcontroller**

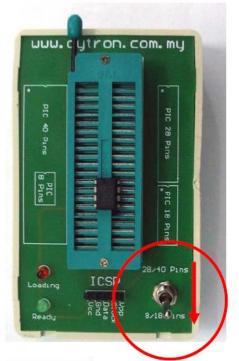

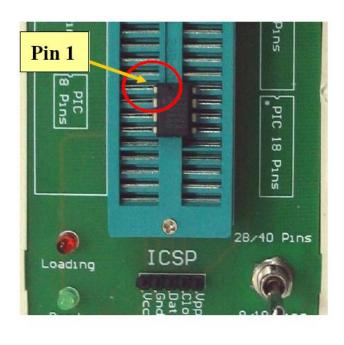

40-pin Microcontroller

• Plug in the microcontroller at the socket (indicated on the board) and **push forward the toggle switch** as shown.

28-pin Microcontroller

• Plug in the microcontroller at the upper portion of the socket (indicated on the board) and **push forward the toggle switch** as shown.

18-pin Microcontroller

• Plug in the microcontroller at the lower portion of the socket (indicated on the board) and **push backwards the toggle switch** as shown.

8-pin Microcontroller

• Plug in the microcontroller at the center portion of the socket (indicated on the board) and **push backwards the toggle switch** as shown.

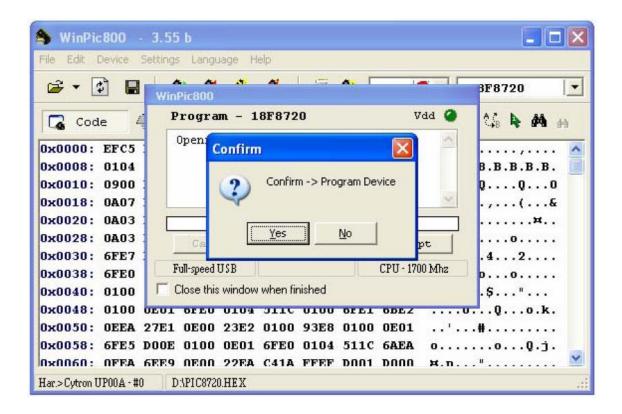

# **3.3.2.2** How to Program The PIC Microcontroller

1. Now WinPic800 is ready to program the PIC. This programmer is able to detect the PIC. By clicking the icon shown, the programmer will detect the type of PIC on the programmer.

| 🛸 WinPic800 - 3.55 b                           |

|------------------------------------------------|

| File Edit Device Settings Language Help        |

| 😂 🔹 🗘 📓 👒 🦠 🐐 🍃 🎒 PIC F 🐼 💌 18F8720 🔍          |

| Code 🖓 Data 🏈 Setting 🗁 🖉 🖓 🎲 🏘 🚧              |

| 0×0000: FFFF FFFF FFFF FFFF FFFF FFFF FF       |

| $0{	imes}0008$ : FFFF FFFF FFFF FFFF FFFF FFFF |

| 0×0010: FFFF FFFF FFFF FFFF FFFF FFFF FFFF     |

| 0×0018: FFFF FFFF FFFF FFFF FFFF FFFF FFFF     |

| 0×0020: FFFF FFFF FFFF FFFF FFFF FFFF FFFF     |

| 0×0028: FFFF FFFF FFFF FFFF FFFF FFFF FFFF     |

| 0×0030: FFFF FFFF FFFF FFFF FFFF FFFF FFFF     |

| 0×0038: FFFF FFFF FFFF FFFF FFFF FFFFF FFFF    |

| 0×0040: FFFF FFFF FFFF FFFF FFFF FFFFF FFFF    |

| 0×0048: FFFF FFFF FFFF FFFF FFFF FFFFF FFFF    |

| 0×0050: FFFF FFFF FFFF FFFF FFFF FFFF FFFF     |

| 0×0058: FFFF FFFF FFFF FFFF FFFF FFFF FFFF     |

| ADAMAS AND |

| Har.>Cytron UP00A - #0                         |

2. To write Hex code to PIC we must first open the hex file. By clicking the icon shown, a browse window will appear, open the hex file by clicking the file.

| S WinPic800 - 3.55 b                                 |

|------------------------------------------------------|

| File Edit Device Settings Language Help              |

| 🕞 💈 🖶 🛸 🛸 🌾 🃁 🏂 PIC F 🖉 🔽 18F8720 🖃                  |

| Copen de 🖓 Data 🏈 Setting 🗈 🖱 🐰 🕼 🏘 🙌                |

| 0x0000: EF1A F000 FFFF FFFF D014 FFFF FFFF FFFF¶ 🔼   |

| 0x0008: FFFF FFFF FFFF FFFF CFD8 F061 CFE8 F060a` 📃  |

| 0x0010: CFE0 F062 C062 FFE0 C060 FFE8 C061 FFD8b.b`a |

| 0x0018: 0010 0011 FFFF FFFF FFFF FFFF FFFF FFF       |

| 0x0020: FFFF FFFF FFFF FFFF FFFF FFFF FFFF           |

| 0x0028: FFFF FFFF FFFF FFFF FFFF FFFF FFFF           |

| 0x0030: FFFF FFFF FFFF FFFF FFFF FFFF FFFF           |

| 0x0038: FFFF FFFF FFFF FFFF FFFF FFFF FFFF           |

| 0x0040: FFFF FFFF FFFF FFFF FFFF FFFF FFFF           |

| 0x0048: FFFF FFFF FFFF FFFF FFFF FFFF FFFF           |

| 0x0050: FFFF FFFF FFFF FFFF FFFF FFFF FFFF           |

| 0x0058: FFFF FFFF FFFF FFFF FFFF FFFF FFFF           |

| חאחה: איז        |

| Har.>Cytron UP00A - #0                               |

| Open                              |                 |         |   |          | ? 🛛    |

|-----------------------------------|-----------------|---------|---|----------|--------|

| Look in:                          | 🧼 Local Disk (D | :)      | • | 🗢 🗈 💣 🎫  |        |

| My Recent<br>Documents<br>Oesktop | PIC8720.HEX     |         |   |          |        |

| My Documents                      |                 |         |   |          |        |

| My Computer                       |                 |         |   |          |        |

| S                                 |                 |         |   |          |        |

| My Network<br>Places              | File name:      | PIC8720 |   | •        | Open   |

|                                   | Files of type:  | *.hex   |   | <b>_</b> | Cancel |

2. Program the file to PIC by clicking the icon shown.

| 🌢 WinPic800 - 3.55 b                                        |

|-------------------------------------------------------------|

| File Edit Device Settings Language Help                     |

| 🖙 🔹 📓 👒 🛞 🐝 🛸 🗦 🕸 PIC F 🚳 🔽 18F8720 🖃                       |

| Code 🥝 Data Program All 🕞 🖱 🐰 🖧 🏘 🙌                         |

| 0x0000: EFC5 F02E 0012 FFFF EFB4 F02C 0012 FFFF             |

| 0x0008: 0104 5118 0B60 42E8 42E8 42E8 42E8 42E8Q`B.B.B.B.B. |

| 0x0010: 0900 E001 D055 5119 0A07 E051 0A0B E04FVQQQ         |

| 0x0018: 0A07 E040 0A01 E02C 0A0B E028 0A02 E026@,(&         |

| 0x0020: 0A03 E022 0A08 E012 0A01 E00E 0A0F E00A"            |

| 0x0028: 0A03 E001 D03C 0100 0E01 6FE0 0100 0E04<            |

| 0x0030: 6FE7 D036 D836 D034 D890 D032 0100 0E01 06.6.42     |

| 0x0038: 6FE0 0100 0EE9 6FE1 0E00 6FE2 0100 93E8             |

| 0x0040: 0100 0E01 6FE5 D024 D8A8 D022 D8F4 D020o\$"         |

| 0x0048: 0100 0E01 6FE0 0104 511C 0100 6FE1 6BE2oQo.k.       |

| 0x0050: 0EEA 27E1 0E00 23E2 0100 93E8 0100 0E01'#           |

| 0x0058: 6FE5 D00E 0100 0E01 6FE0 0104 511C 6AEA ooQ.j.      |

| ∩×∩∩6∩: OFEA 6EE9 0EO0 22EA C41A FFEF DO01 DO00 ¥.n"        |

| Har.>Cytron UP00A · #0 D:\PIC8720.HEX .::                   |

4. A confirmation window will appear, click Yes to proceed programming PIC.

| _                                                            |                                                                                                                    |           |  |  |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------|--|--|

| 🛎 🔹 🖬                                                        | WinPic800                                                                                                          | BF8720    |  |  |

| Code 4                                                       | Program - 18F8720 Vaa 🥝                                                                                            | 16 A 44 A |  |  |

| 0x0000: EFC5<br>0x0008: 0104<br>0x0010: 0900<br>0x0018: 0A07 | PIC detected -> 18F8720<br>PIC is Erased .: 0k<br>[ Verifying during programming ]<br>Programming Code: 65536 word |           |  |  |

| 0x0020: 0A03                                                 | 16%                                                                                                                | ¤         |  |  |

| Dx0028: 0A03                                                 | Cancel Progress Accept                                                                                             |           |  |  |

| Dx0030: 6FE7                                                 | .42.                                                                                                               |           |  |  |

| 0x0038: 6FE0                                                 | Full-speed USB Pgm - 1 ms CPU - 1700 Mhz po                                                                        |           |  |  |

| Dx0040: 0100                                                 | Close this window when finished                                                                                    | .\$"      |  |  |

| Dx0048: 0100 br                                              |                                                                                                                    | 0Qo.k.    |  |  |

|                                                              | YE1 0E00 23E2 0100 93E8 0100 0E01'.                                                                                | #         |  |  |

| 0x0050: 0EEA 27                                              | EI 0E00 23E2 0100 33E0 0100 0E01                                                                                   |           |  |  |

5. When it is completed, the window will show the status. Click *Accept* and the PIC is ready to be plug out.

|                              | tings Language Help                      |          |  |  |  |

|------------------------------|------------------------------------------|----------|--|--|--|

| 🖻 🕶 🔁                        | WinPic800                                | BF8720   |  |  |  |

| Code 4                       | Program - 18F8720 Vaa 🥝                  | 15 A # # |  |  |  |

| Dx0000: EFC5<br>Dx0008: 0104 | Code: 0k<br>ID: 0k<br>Config. : 0k       |          |  |  |  |

| 0x0010: 0900<br>0x0018: 0A07 | Data: 0k                                 |          |  |  |  |

| 0x0020: 0A03                 | 100%                                     | ¤        |  |  |  |

| 0x0028: 0A03<br>0x0030: 6FE7 | Cancel Progress Accept                   | 0        |  |  |  |

| 0x0038: 6FE0                 | Full-speed USB Pgm · 1 ms CPU · 1700 Mhz |          |  |  |  |

| 0x0040: 0100                 | 🗖 Close this window when finished        | .\$"     |  |  |  |

| 0x0048: 0100 or              | OI OFEU UIU4 JIIC UIUU OFEI OBEZ         | 0Qo.k.   |  |  |  |

| 0x0050: 0EEA 27              | E1 0E00 23E2 0100 93E8 0100 0E01'.       |          |  |  |  |

| 0x0058: 6FE5 DC              | OE 0100 0E01 6FE0 0104 511C 6AEA o       | Q.j.     |  |  |  |

| NXAAAA ( NFEA AF             | E9 NENN 22EA C41A FFEF DANI DANN H.n.    |          |  |  |  |

6. To disconnect UP00A, simply plug the USB out. No extra configuration or setting needed. Same applied when plug-in for the 2nd time, installation of driver is not required.

## 3.33 PIC Driver Circuit Hardware

At this part, it more focused on control element. The main component that control our system is PIC microcontroller. In this circuit there are consisted of oscillator 20MHz, Capacitor to reduced ripple for ADC, Connector to LCD and also output relay and also input ADC. This driver circuit has fewer components than the actual PIC driver circuit. It has been test that by reducing the capacitor in the circuit, there is not much changing in the operation of the circuit. Because the 5Volt input voltage that have been

supply to the driver circuit is already stable, and there is no reverse current from the Solid State Relay. So by using this driver circuit, the space and troubleshooting is easier to be done.

#### **3.4 Programming Flowchart**

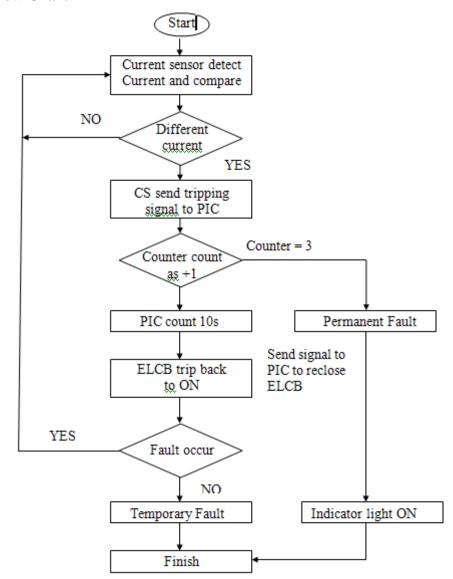

Figure 3.9: Flow of Programming Software

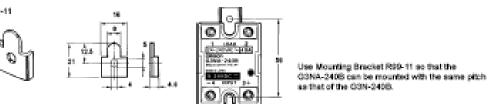

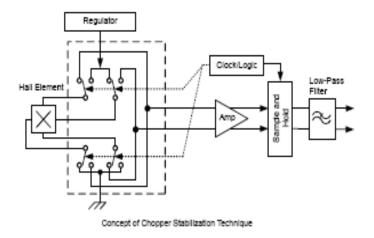

From the figure, when a fault occur current sensor will sense the imbalance current and then it will induced a signal current. This signal then is send to PIC microcontroller via sensing circuit.PIC controller will calculate the differential value of current between two of current sensor and if differential exist, it show fault exist and assigned.PIC will send signal to trip ELCB. At this moment the counter in the PIC will start count as 1. After 10 second, the ELCB will automatically switch back to normal condition. If there is no fault detect after the ELCB is turn on the LCD will display temporary fault and the ELCB will stay connected until next fault occurred and the counter will be reset. Meanwhile if there is fault occurred instantly after the ELCB is turning back to on, the current sensor will detect the imbalance current and then will send back the signal to PIC. The ELCB then will turn on back after being trip. At this time PIC counter will count as 2, this process will be cycle until the counter reach 3. After PIC counter reach 3, PIC microcontroller will identify the fault as permanent fault such like short circuit and over-current. At the end, ELCB is permanently tripped and to turn on back the circuit, someone should manually turn on itself.

### 3.5 Summary

From this chapter, we are able to understand more about PIC basic configuration and their development. The advantage using PIC are the capability to interface directly with other device such as LCD, solid state relay are more reliable. Beside of that, PIC programming is much more simpler compared to other microcontroller. Based on pin configuration, there are four port in PIC that freely to used either input or output. Then from this chapter, we can learn much more about microcode studio that has been used to write programming in HEX file. Then for the next step, we can learn the using of CYTRON USB programmer as a device to transfer HEX file programming to PIC18F4550.From our observation, PIC can make system more reliable, faster and easier to handle.

### **CHAPTER 4**

### DEVELOPMENT OF AUTO-RECLOSER EARTH LEAKAGE CIRCUIT BREAKER

### 4.1 Introduction

This chapter explains our process to develop auto re-closer earth leakage circuit breaker include project flow, circuit design, hardware operation process and software implementation. This chapter also explains about designing the basic PIC circuit, LCD, current sensor circuit, interfacing PIC to circuit breaker, PIC programming.

This chapter will explain detail early process to design new auto re-closer earth leakage circuit breaker until last stage that connected our device and PIC. Beside that, this chapter also explains our component that has been used in this project and their advantage. Thus, to design effective ELCB, several changed has been made so that the size and the cost are acceptable for commercial purpose.

### 4.2 **Project Flow**

This project starts with study the basic design of an ELCB. This is done by explore and open a unit of ELCB rating 40A with sensitivity 100mA.From there, it showed our component that involve to build ELCB and how their function. The next stage is to think how to renovate in order to change from mechanical switching to electrical switching. Next is to identify where the suitable component to connect with PIC microcontroller. After that process, new circuit of new auto re-close ELCB are designed. For early stage, the first thing to do are designing the basic of power circuit that include voltage regulator, bridge rectifier, transformer to produce 5Vdc that will be used to supply PIC, current sensor and LCD. Then follow by designing the controller circuit involve the application of PIC microcontroller. The next stage is designing the electronic switching circuit which needs to be used instead of original mechanical switch. The last stage of circuit is to design sensing circuit using current sensor that will sense to any fault occurred. Then finally stage, all the circuit is combined together and then trouble shooting is done to check our circuit connection. After hardware is finished, programming can be made to make the flow of process following the in flow chart. By using different method to different any fault, new auto re-closer is tested according each fault and when there were problem occur, the hardware is troubleshoot and the problem is correct. The process was done when the new auto re-closer ELCB running following the objective requirement.

### 4.3 proposed design

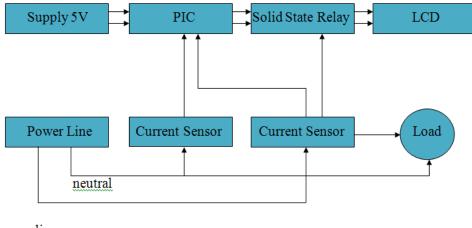

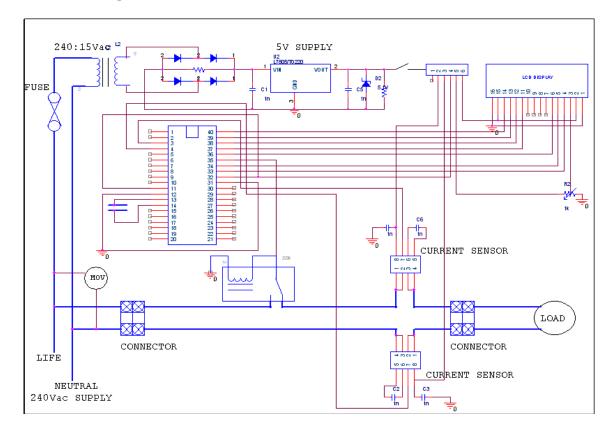

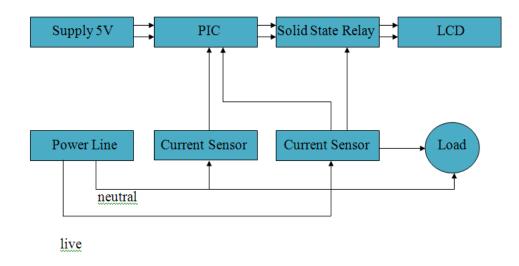

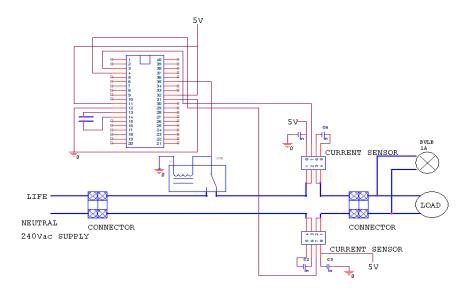

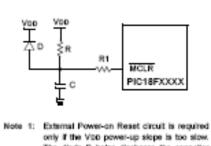

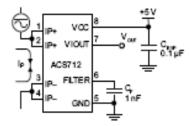

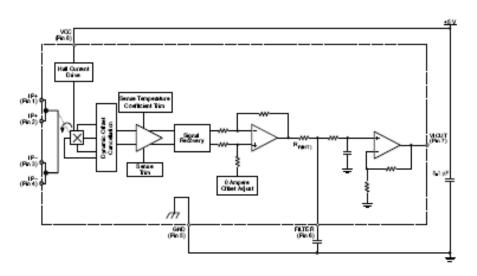

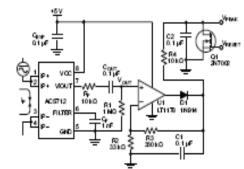

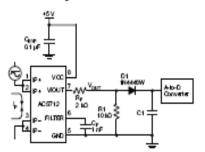

Based from proposed design in figure 3.1 below, transformer 240/15Vac step down is used to converting 240Vac from power line to 5Vdc by using full wave rectifier circuit. The 5Vdc will used to energize the LCD, PIC and current sensor. An protection at power line, metal oxide varistor 275V (MOV) is used to protect component in power circuit if fault like over current happen.

From that figure, the application of solid state relay is used as switch to replaced mechanical switch in old ELCB. SSR is selected as switching is because the reliability of the SSR itself as Electronic switch that can be operated at high voltage and current. LM 7805 voltage regulator will be used to step down the voltage from 15Vdc to 5Vdc to ensure it suitable to supply to PIC, LCD and current sensor.

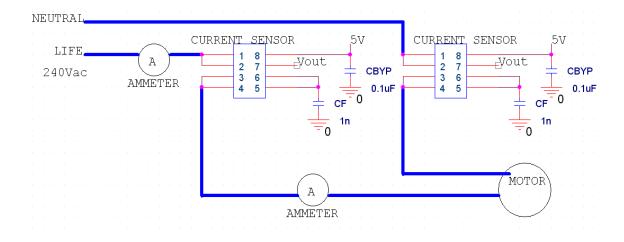

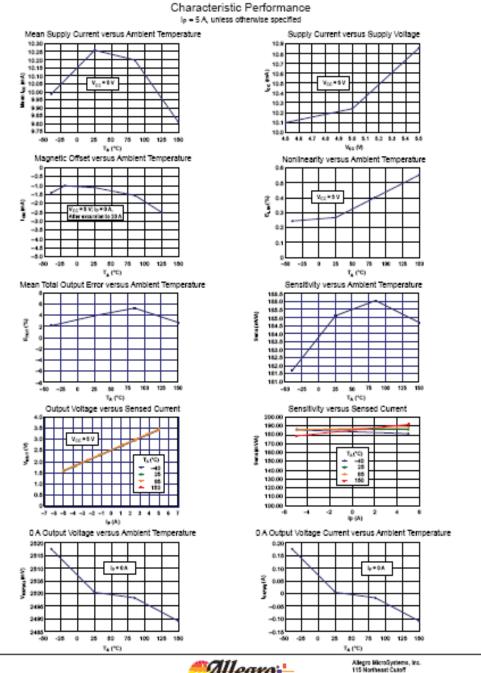

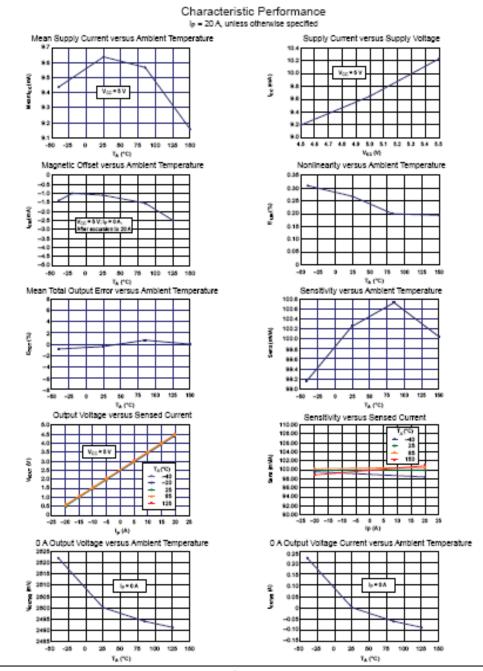

For sensing circuit, half effect current sensor with rating 5A is used to detect the any leakage current between neutral and phase then send tripping signal to PIC which assigned the fault are occurred. The output of current sensor is fixed 5V and it will easier PIC to understand the information received.

For the control element, PIC 18F4550 is choosed to control our system. That PIC will receive the data information from current sensor and decide to connect or disconnected circuit. It can be done by connect PIC with solid state relay which PIC will control switching of SSR.

live

Figure 4.1: Basic Operation of Auto Re-closer ELCB

#### 4.4 Stage 1 circuit

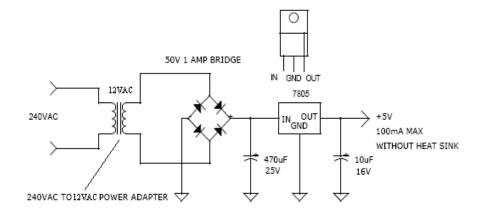

Refer from figure 4.2, this power circuit is the combination between transformer 240Vac/12Vac, bridge rectifier, LM7805, capacitor 470uF and capacitor 10uF.Transformer will step down the 240Vac to 15Vac then bridge will change from ac source current to dc source. After that, LM7805 will used to regulate voltage from

15Vdc to 5Vdc supply. Lastly, LED will connected at the end of 5V terminal to show that 5V is already give supply to LCD, PIC, and current sensor.

Figure 4.2: 5Vdc Power Supply Circuit

### 4.5 Stage 2 circuit

Based from that figure, it showed the interfacing between PIC and JHD162A LCD display. The LCD is used as output and PIC will assign connection of LCD pin with 0.If PIC receive tripping signal following fault occurred, PIC will send data to LCD to display either temporary fault or permanent fault was detected. To make system more simple and tidy, ribbon cable is used as connector between LCD and PIC. Both of PIC and LCD need 5V that come from power circuit to execute their operation. For PIC driver, 20Mhz crystal oscillator is used to control the clock cycle of the system. variable resistor 20K is used to control the LCD screen .

Figure 4.3: PIC Microcontroller and LCD circuit

According from the table 4.4, it show the total connection pin used for PIC18F4550.PIC18F4550 is connected with LCD, solid state relay and current sensor and total pin used is 16 pin. Pin 11 and 13 assigned as VDD pin, it connected together to receiving 5V supply. Beside that, pin 12 and 31 is assigned as Vss pin which it connected together directly go to ground.Meabwhile,OSC1 and OSC2 is connected to 20Mhz oscillator which act as clock for PIC 18F4550.Next,RA1 and RA2 is the pin from port A which it especially for analog input, which that port will understand any information in analog signal form from sensing circuit. Then, port B is placed by LCD and solid state relay and both of them is used as output.

| Table 4.4: PIC18F4550 | ) pin | used | detail |

|-----------------------|-------|------|--------|

|-----------------------|-------|------|--------|

| Pin Name  | Pin No. | Description           | Application         |

|-----------|---------|-----------------------|---------------------|

| VDD       | 11, 32  | Positive supply (+5V) | Power supply to PIC |

| VSS       | 12, 31  | Ground references     | Ground references   |

| MCLR      | 1       | Input                 | For reset button    |

| OSC1,OSC2 | 13, 14  | For oscillator        | Connected to 20MHz  |

|              |                           |                    | crystal                                    |

|--------------|---------------------------|--------------------|--------------------------------------------|