# DEVELOPMENT OF MICROHYDRO GENERATOR SYSTEM

AHMAD ZUBAIDI BIN ABDUL AZIZ @ MD RANI

UNIVERSITI MALAYSIA PAHANG

# UNIVERSITI MALAYSIA PAHANG

| BORAN                                                                                     | G PENGESAHA                                                                  | N STATUS TESIS*                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| judul: <u>DEVELOPN</u>                                                                    |                                                                              | HYDRO GENERATOR                                                                                                                                                                        |

|                                                                                           | SESI PENCA HAN                                                               |                                                                                                                                                                                        |

|                                                                                           | SESI PENGAJIAN:                                                              |                                                                                                                                                                                        |

| Saya <u>AHMAD ZUB</u>                                                                     | AIDI BIN ABDUL AZI<br>(HURUF BESA                                            | Z @ MD RANI (870210-11-5607)<br>AR)                                                                                                                                                    |

| mengaku membenarkan te<br>Perpustakaan dengan syar                                        |                                                                              | <del>na</del> / <del>Doktor Falsafah</del> )* ini disimpan di<br>ti berikut:                                                                                                           |

| 2. Perpustakaan dibenar                                                                   |                                                                              | aang (UMP).<br>cuk tujuan pengajian sahaja.<br>is ini sebagai bahan pertukaran antara institusi                                                                                        |

| SULIT                                                                                     | atau kepenting                                                               | maklumat yang berdarjah keselamatan<br>an Malaysia seperti yang termaktub<br>A RAHSIA RASMI 1972)                                                                                      |

|                                                                                           |                                                                              | maklumat TERHAD yang telah ditentukan<br>i/badan di mana penyelidikan dijalankan)                                                                                                      |

| √ TIDAK                                                                                   | TERHAD                                                                       | Disahkan oleh:                                                                                                                                                                         |

| (TANDATANGAN PENU                                                                         |                                                                              | (TANDATANGAN PENYELIA)                                                                                                                                                                 |

| , , , , , , , , , , , , , , , , , , ,                                                     | (13)                                                                         | (TAUDATAIOAN LEVILLA)                                                                                                                                                                  |

| Alamat Tetap:<br><u>1111 KAMPUNG PANT</u><br>20400 KUALA TERENG<br>TERENGGANU DARU        | GGANU,                                                                       | MOHD REDZUAN BIN AHMAD<br>( Nama Penyelia )                                                                                                                                            |

| Tarikh: <u>30 NOVEMBER</u>                                                                | 2010                                                                         | Tarikh: <u>30 NOVEMBER 2010</u>                                                                                                                                                        |

| <ul> <li>** Jika tesi</li> <li>berkuasi</li> <li>dikelask</li> <li>◆ Tesis dit</li> </ul> | a/organisasi berkenaan d<br>an sebagai atau TERHA<br>maksudkan sebagai tesis | AD, sila lampirkan surat daripada pihak<br>engan menyatakan sekali tempoh tesis ini perlu<br>D.<br>bagi Ijazah doktor Falsafah dan Sarjana secara<br>pengajian secara kerja kursus dan |

penyelidikan, atau Laporan Projek Sarjana Muda (PSM).

"I hereby acknowledge that the scope and quality of this thesis is qualified for the award of the Bachelor Degree of Electrical Engineering (Power System)"

| Signature | :                               |

|-----------|---------------------------------|

| Name      | : <u>MOHD REDZUAN BIN AHMAD</u> |

| Date      | : <u>30 NOVEMBER 2010</u>       |

## DEVELOPMENT OF MICROHYDRO GENERATOR SYSTEM

### AHMAD ZUBAIDI BIN ABDUL AZIZ @ MD RANI

This thesis is submitted as partial fulfillment of the requirements for the award of the Bachelor of Electrical Engineering (Power System)

Faculty of Electrical & Electronics Engineering Universiti Malaysia Pahang

NOVEMBER, 2010

"All the trademark and copyrights use herein are property of their respective owner. References of information from other sources are quoted accordingly; otherwise the information presented in this report is solely work of the author."

| Signature | :                                               |

|-----------|-------------------------------------------------|

| Author    | : <u>AHMAD ZUBAIDI BIN ABDUL AZIZ @ MD RANI</u> |

| Date      | : <u>30 NOVEMBER 2010</u>                       |

Specially dedicated to my beloved family To My beloved Mother and Dad And those people who have guided and inspired me throughout my journey of education

Thanks for everything...

### ACKNOWLEDGEMENT

First and foremost, I am very grateful to the almighty ALLAH S.W.T for letting me to finish my Final Year Project.

Here, I wish to express my sincere appreciation to my supervisor, En. Mohd Redzuan bin Ahmad for encouragement, guidance, suggestions, critics, friendship and advices which gave inspiration in accomplishing my final year project.

Special thanks to Universiti Malaysia Pahang for supporting and providing equipment and information sources that assisted my studies and projects.

My sincere appreciation to the lecturer of Faculty of Electrical and Electronic Engineering who are put in effort to the lectures and always nurture and guide us with precious advices. Thank you for sharing those experiences.

Lastly, I wish my gratitude to my parents for their support, encouragement, understanding, sacrifice and love.

# ABSTRACT

The chief sources of energy used for the generation of electrical energy are water, fuels and nuclear energy. Micro-Hydro Generator Systems (MHGS) converts potential energy of water into electricity. It is a clean source of energy. Hydro electric power plants generate from few kW to thousands of MW. It can be classified as Micro Hydro power system for the generating capacity less than 100kW. Micro hydro can provide alternative renewable energy sources especially in areas with small rivers or stream flowing. Other renewable energy source, such as solar and wind, can be used to produce electrical power. The choice of energy source depends on several factors, including availability, economic and energy and power requirements. Micro hydro power is almost always more cost-effective than any other form of renewable power. Micro hydro designates projects with power output of less than 500W. This project is also using a Programmable Interface Controller (PIC) and power electronic components in designing hardware. In the end of the project, the proposed micro hydro-generator work properly as designed and produce output power as high as 500W or more and can be used for lighting, bulk, and battery charge and electronics devices.

# ABSTRAK

Sumber utama tenaga yang digunakan untuk penjanaan tenaga elektrik adalah air, bahan api dan tenaga nuklear. Sistem penjanaan kuasa mikro hidro adalah sistem menukar tenaga keupayaan air kepada tenaga elektrik. Ini merupakan sumber tenaga bersih. Tenaga penjanaan air elektrik menghasilkan dari beberapa kW ribuan kepada MW. Hal ini boleh diklasifikasikan sebagai sistem tenaga elektrik Mikro hidro untuk kapasiti menghasilkan kurang dari 100kW. Mikro hidro dapat menyediakan sumber tenaga alternatif terbaru terutama di daerah-daerah dengan air sungai kecil atau air sungai yang mengalir. Selain itu, sumber tenaga yang boleh diperbaharui ialah seperti solar dan angin, boleh digunakan untuk menghasilkan tenaga elektrik. Pemilihan sumber tenaga bergantung pada beberapa faktor, termasuk yang sedia ada, ekonomi dan tenaga dan keperluan kuasa. Kuasa Mikro hidro hampir selalu lebih jimat berbanding daripada bentuk lain dari tenaga yang boleh diperbaharui. Projek Mikro hidro ini direkabentuk supaya dapat menghasilkan kuasa lebih kurang dari 500W. Projek ini juga menggunakan komponen (PIC) pengawal mikro dan skematik elektronik dalam perancangan. Pada akhir projek, dicadangkan sistem penjana mikrohidro dapat bekerja dengan baik seperti yang dirancang dan menghasilkan kuasa keluaran setinggi 500W atau lebih dan boleh digunakan untuk pencahayaan, lampu rumah, dan pengecas bateri dan barangan elektronik.

# **TABLE OF CONTENTS**

| CHAPTER | TITLE                     | PAGE |

|---------|---------------------------|------|

|         | TITLE PAGE                | i    |

|         | DECLARATION               | ii   |

|         | DEDICATION                | iii  |

|         | ACKNOWLEDGEMENT           | iv   |

|         | ABSTRACT                  | V    |

|         | ABSTRAK                   | vi   |

|         | TABLE OF CONTENTS         | vii  |

|         | LIST OF TABLES            | Х    |

|         | LIST OF FIGURES           | xi   |

|         | LIST OF ABBREVIATIONS     | xii  |

|         | LIST OF APPENDICES        | xiii |

| 1       | INTRODUCTION              | 1    |

|         | 1.1 Project Background    | 1    |

|         | 1.2 Problem Statements    | 2    |

|         | 1.3 Objectives of Project | 2    |

|         | 1.4 Scope of Project      | 3    |

|         | 1.5 Literature Review     | 3    |

|         | 1.6 Thesis Outline        | 4    |

# MICROHYDRO GENERATOR SYSTEM

| (MI | HGS)                                      | 6  |

|-----|-------------------------------------------|----|

| 2.1 | Introduction                              | 6  |

| 2.2 | Operation of MHGS                         | 6  |

|     | 2.2.1 Measuring Head                      | 7  |

|     | 2.2.2 Measuring of Flow Rate              | 7  |

|     | 2.2.3 Measuring of Potential Power        | 8  |

| 2.3 | Overview of Micro hydropower potential in |    |

|     | Malaysia                                  | 8  |

| 2.4 | Advantages of MHGS                        | 10 |

| 2.5 | Disadvantages of MHGS                     | 10 |

| 2.6 | Summary                                   | 11 |

# **3 DEVELOPMENT OF MICROHYDRO**

| GE  | GENERATOR SYSTEM (MHGS)               |    |  |

|-----|---------------------------------------|----|--|

| 3.1 | Introduction                          |    |  |

| 3.2 | Hardware Development                  | 12 |  |

|     | 3.2.1 Mechanical System Design        | 13 |  |

|     | 3.2.2 Electrical System Design        | 16 |  |

| 3.3 | System Components of MHGS             | 17 |  |

|     | 3.3.1 Alternator                      | 17 |  |

|     | 3.3.2 Battery                         | 18 |  |

|     | 3.3.3 Charge Controller               | 18 |  |

|     | 3.3.4 Inverter                        | 19 |  |

|     | 3.3.5 Ballast Load                    | 19 |  |

|     | 3.3.6 Turbine                         | 20 |  |

|     | 3.3.6.1 Impulse Turbine               | 20 |  |

|     | 3.3.6.2 Reaction Turbine              | 21 |  |

| 3.4 | Software Implementation               | 23 |  |

|     | 3.4.1 MicroCode Studio (PBP) Compiler | 23 |  |

|     | 3.4.2 UP00B PIC USB Programmer        | 27 |  |

| 3.4.2.1 Board Layout                    | 28 |

|-----------------------------------------|----|

| 3.4.2.2 Installation (Software)         | 29 |

| 3.4.2.3 Plugging the Microcontroller    | 30 |

| 3.4.2.4 Program the PIC Microcontroller | 30 |

| 3.5 Summary                             | 35 |

| RESULTS AND DISCUSSIONS                 | 36 |

| 4.1 Introduction                        | 36 |

| 4.2 Alternator output                   | 37 |

| 4.3 Water Power Output                  | 40 |

| 4.4 Charge Controller Circuit           | 41 |

| 4.5 Summary                             | 47 |

| CONCLUSION                              | 48 |

| 5.1 Conclusion                          | 48 |

| 5.2 Recommendation                      | 49 |

| 5.3 Costing and Commercialization       | 49 |

| 5.3.1 Costing                           | 49 |

| 5.3.2 Commercialization                 | 51 |

| REFERENCES                              | 52 |

4

5

|                  | 52    |

|------------------|-------|

| Appendices A - E | 53-82 |

# LIST OF TABLES

| TABLE NO. | TITLE                                     | PAGE |  |

|-----------|-------------------------------------------|------|--|

|           |                                           |      |  |

| 3.1       | Function of Board Layout Identified       | 28   |  |

| 4.1       | Alternator speed without battery          | 37   |  |

| 4.2       | Alternator speed using battery            | 38   |  |

| 4.3       | Alternator output current                 | 39   |  |

| 4.4       | Theoretical of Water Power Output in Watt | 40   |  |

| 5.1       | The cost of components                    | 50   |  |

# LIST OF FIGURES

| FIGURE NO. | TITLE                                        | PAGE |  |

|------------|----------------------------------------------|------|--|

| 2.3        | Map of Peninsular Malaysia                   | 9    |  |

| 3.1        | Block Diagram of Microhydro Generator System |      |  |

|            | (MHGS)                                       | 13   |  |

| 3.2        | Hardware System of MHGS                      | 14   |  |

| 3.3        | Operation System of MHGS using AC Motor      | 15   |  |

| 3.4        | Circuit charge controller using PIC18F4550   | 16   |  |

| 3.5        | Automotive Alternator                        | 17   |  |

| 3.6        | Lead-acid batteries                          | 18   |  |

| 3.7        | Inverter                                     | 19   |  |

| 3.8        | Waterwheel                                   | 20   |  |

| 3.9        | Comparisons of Impulse and Reaction Turbine  | 22   |  |

| 3.10       | CYTRON USB Programmer                        | 28   |  |

| 3.11       | Board Layout USB Programmer UP00B            | 29   |  |

| 3.12       | Plug-in 40-pin Microcontroller               | 30   |  |

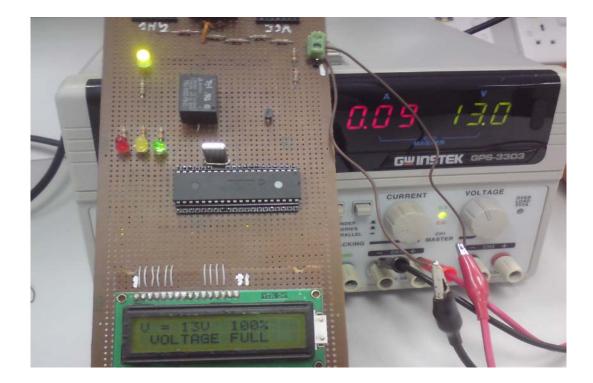

| 4.1        | Voltage Full at 12V using simulation         | 41   |  |

| 4.2        | Voltage Full at 13V and 100% using Power DC  |      |  |

|            | supply                                       | 42   |  |

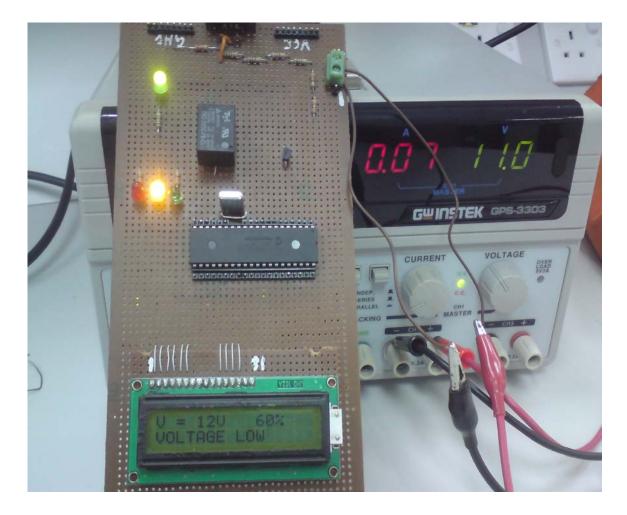

| 4.3        | Voltage Low at 7V using simulation           | 43   |  |

| 4.4        | Voltage low at 12V and 60%                   | 44   |  |

| 4.5        | Battery Charging at 4V using simulation      | 45   |  |

| 4.6        | Battery start charging at voltage 9V and 30% | 46   |  |

# LIST OF ABBREVIATIONS

| D,d | - | Diameter                                       |

|-----|---|------------------------------------------------|

| AC  | - | Alternating Current                            |

| DC  | - | Direct Current                                 |

| А   | - | Ampere                                         |

| V   | - | Volt                                           |

| W   | - | Watt                                           |

| Pth | - | Theoretical water power output in W            |

| Q   | - | Usable flow rate in m <sup>3</sup> /s          |

| Н   | - | Gross head in m                                |

| G   | - | Gravitational constant (9.8 m/s <sup>2</sup> ) |

| m   | - | meter                                          |

| mm  | - | millimeter                                     |

| sq  | - | square                                         |

| km  | - | kilometer                                      |

| VDC | - | Voltage Direct Current                         |

| ADC | - | Voltage Alternate Current                      |

| Hz  | - | Hertz                                          |

# LIST OF APPENDICES

# APPENDIXTITLEPAGE

| А | Charging System of Alternator             | 53 |

|---|-------------------------------------------|----|

| В | Micro Hydro Potential in West Malaysia    | 61 |

| С | PIC18F4550 Microcontroller and Addressing |    |

|   | Modes                                     | 64 |

| D | Programming of Charge Controller          | 75 |

| E | Flow Chart                                | 81 |

ii

**CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Project Background

Micro-Hydro Generator Systems (MHGS) convert the energy of moving water into electricity. Generator systems convert from mechanical to electrical energy. This project is to develop a Micro-Hydro generator system using battery based system to generate power. The battery based system that we will use is Lead-acid deep cycle batteries. This battery can be charge and discharge system. The prime mover of this project is water that means source of water pressure from a present water tank, pipes and to turn a turbine then the turbine spins an alternator and electricity is produces to charge the battery. Then an alternator converts the mechanical energy from the turbine into electrical energy. Many other components may be in a system, but it all begins with the energy already within the moving water. Other renewable energy source, such as solar and wind, can be used to produce electrical power. The choice of energy source depends on several factors, including availability, economic and energy and power requirements. Micro hydro power is almost always more cost-effective than any other form of renewable power. Micro hydro designates projects with power output of less than 100 kW. This project is also using a Programmable Interface Controller (PIC) and power electronic components in designing hardware. In the end of the project, the proposed micro hydro-generator will work properly as designed and will produce output power as high as 1kW or more and can be used for lighting, bulk, and battery charger and electronics devices.

#### **1.2 Problem Statements**

Hydro generator system in market is huge and high cost and no micro hydro generator in the market.

#### **1.3** Objectives of Project

The objectives of this project are:

- i. To produce electricity using renewable source of energy.

- ii. To implement the use of Programmable Intelligent Circuit (PIC) and Power Electronics switch in designing hardware.

- iii. To provide clean, environmentally friendly electricity in rural communities.

#### **1.4** Scope of project

The scope of this project is:

- i. To develop of Micro-Hydro Generator System using automotive alternator.

- ii. Using PIC 16F877 microcontroller as a control circuit.

- iii. Produce output power at least 500W

#### **1.5** Literature Review

Micro hydro power was once the world's prominent source of mechanical power for manufacturing. Micro hydro is making a comeback for electricity generation in homes. This system of the Micro hydro can be divide by two is Battery base systems and AC- Direct System.[1].

The battery base system is power can be supplied by a micro hydro system in two ways. In a battery-based system, power is generated at a level equal to the average demand and stored in batteries. Batteries can supply power as needed at levels much higher than that generated and during times of low demand the excess can be stored. If enough energy is available from the water, an AC-direct system can generate power as alternating current (AC). This system typically requires a much higher power level than the battery-based system. The input voltage to the batteries in a battery-based system commonly ranges from 12 to 48 Volts DC. If the transmission distance is not great then 12 Volts is often high enough. A 24 Volt system is used if the power level or transmission distance is greater. If all of the loads are inverter-powered the battery voltage is independent of the inverter output voltage and voltages of 48 or 120 may be used to overcome long transmission distances. Although batteries and inverters can be specified for these voltages, it is common to convert the high voltage back down to 12 or 24 Volts (battery voltage) using transformers or solid state converters.[1]

Most battery-based systems use an automotive alternator. If selected carefully, and rewound when appropriate, the alternator can achieve very good performance. A rheostat can be installed in the field circuit to maximize the output. Rewound alternators can be used even in the 100–200 Volt range.[1]

Micro hydro power is best where water supply is continuously available. Where supply is seasonal it may still be cost effective to install micro hydro as a stand-alone system. This will depend on whether the cost of installing the system is offset by the savings made during the period when the creek is flowing. Another renewable system, or a generator, will be required when water is not available.[2]

#### **1.6** Thesis Outline

This report contains 5 chapters which is every chapter have its own purpose. After viewing the entire chapter in this report, hopefully the viewer can understand the whole system design for this project.

Chapter 1 describe on the background of the project, problem statement, objectives, scope of the project and the literature review that referred to in the development of micro hydro generator system.

Chapter 2 is focused to the theory of the Micro Hydro Generator System (MHGS) where it described about operation of MHGS and measuring of head, flow and potential power. This chapter also include why we need to use MHGS.

Chapter 3 elaborated more on the method of micro hydro generator system. Besides it also describe the functions of each components used in the system and operation such as alternator, battery, charger controller, inverter and ballast load.

Chapter 4 present about result and discussion while in development process. The result of this project is also accompanied by the discussion for each problem statement.

Lastly in Chapter 5, in this chapter the conclusion has been made for the project from the whole aspect and there are also suggestions to improve the micro hydro generator system in the future, in case for the commercialization. **CHAPTER 2**

#### MICRO-HYDRO GENERATOR SYSTEM (MHGS)

#### 2.1 Introduction

This chapter explains about a theory of Micro Hydro Generator System (MHGS) included operation of MHGS, measuring of head, flow rate and potential power produces so that the reader will get a clear idea how the MHGS is working. To achieve that first we need to study more about MHGS and doing more research about the MHGS operation. This chapter also includes overview of Micro Hydropower potential in Malaysia.

### 2.2 Operation of MHGS

A Micro Hydro Generator System (MHGS) convert the energy of moving water into electricity. Instead, a portion of a stream or river is temporarily diverted into a pipe system and to the micro-hydro turbine and generator. It is then returned to its source. Because of this these types of system have far less impact on the environment than large scale hydro schemes. Micro hydro generator systems use the force of running water to turn turbine blades, which spin a shaft connected to a generator. These systems are best suited to rural sites, and can be set up wherever water falls from a higher lever to a lower level, such as a waterfall, hillside, stream, or where a reservoir discharges into a river. The type of turbine required will depend on the 'head' (the vertical fall) and the flow rate of the water. There are two basic of turbines such as impulse and reaction. These turbines are more details explanation in Chapter 3.

#### 2.2.1 Measuring of Head

Generally, the distance the water falls depends on the steepness of the terrain the water is moving across, or the height of a dam the water is stored behind. The farther the water falls, the more power it has. In fact, the power of falling water is 'directly proportional' to the distance it falls. In other words, water falling twice as far has twice as much as energy. It is important to note we are only talking about the vertical distance the water falls. The distance the water travels horizontally is consequential only in expense of the system and friction losses. Head is usually measured in 'feet'.

#### 2.2.2 Measuring of Flow Rate

More water falling through the turbine will produce more power. The amount of water available depends on the volume of water at the source. Power is also 'directly proportional' to river flow, or flow volume. A river with twice the amount of flowing water as another river can produce twice as much energy. This is also effect of choice a size of pipelines. Flow volume is usually measured in 'gallons per minute', or 'GPM'.

#### 2.2.3 Measuring of Potential Power

The amount of power available from a micro hydro generator system is directly related to the flow rate, head and the force of gravity. Once we have determined the usable flow rate (the amount of flow we can divert for power generation) and the available head for our particular site, we can calculate the amount of electrical power we can expect to generate. This is calculated using the following equation:

> Pth = Q x H x g Pth = Theoretical power output in kW Q = Usable flow rate in m3/s H = Gross head in m g = Gravitational constant (9.8 m/s2)

#### 2.3 Overview of Micro Hydropower Potential in Malaysia

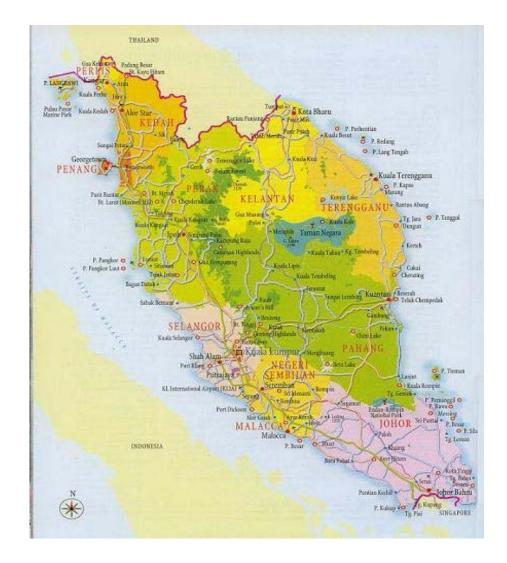

Malaysia comprises of two distinct region which are West Malaysia covering Peninsula Malaysia and East Malaysia covering North Borneo. In total, both regions cover land area of 330 000 sq. km in which 58% is lowland areas and 42% is highland areas []. The highland areas in Malaysia are created by numbers of well known ranges. In Peninsula Malaysia, the highland areas are created by ranges such as Titiwangsa, Tahan, Bintang, Kledang, and Pantai Timur. Barisan Titiwangsa range is the main range which is considered as the backbone of Peninsula. In Sarawak, the highland areas were created mainly by Tama Abu, Iran and Kapuas Hulu ranges. In Sabah the highland areas were created by Crocker, Maitland and Brassey. With average rainfall of 2540 mm in Peninsula, 2630 mm in Sabah and 3850 mm in Sarawak, Malaysia bless with abundant streams and rivers flowing from the highland areas created by these ranges []. Combinations of highland area with huge river networks promise Malaysia with a lot of micro hydropower potential. Figure 2.3 shows the map of Peninsular Malaysia.

Figure 2.3 Map of Peninsular Malaysia

#### 2.4 Advantages of MHGS

The advantages of MHGS is efficient energy, meaning that it only takes a small amount of flow or a drop as low as two feet to generate electricity with micro hydro. Electricity can be delivered as far as a mile away to the location where it is being used. Secondly, reliable electricity source, meaning that hydro produce a continuous supply of electrical energy in comparison to other small-scale renewable technologies. Lastly, the advantage of MHGS is no reservoir required, meaning that the water passing through the generator is directed back into the stream with relatively little impact on the surrounding ecology.

#### 2.5 Disadvantages of MHGS

The disadvantages of MHGS is suitable site characteristic required, meaning that factor to consider are distance from the power source to the location where energy is required, stream size and balance system component like inverter, batteries and controller. Second disadvantage is energy expansion not possible, meaning that the size and flow of small streams may restrict future site expansion as the power demand increases. Lastly, environmental impact, meaning that the ecological impact of small-scale hydro is minimal, however the low-level environment effect must be taken into consideration before construction begins.

# 2.5 Summary

From this Chapter 2, we can see that before we develop the Micro Hydro Generator System (MHGS), we must know to measure of head and flow rate. That is important to calculate output power of the system. Besides that, we also know for the long term, why we need to use MHGS this is because it can be more economical and also may be that we are interested in helping to protect the environment. In this chapter also explain about advantages and disadvantages of using MHGS.

# **CHAPTER 3**

### DEVELOPMENT OF MICRO HYDRO GENERATOR SYSTEM (MHGS)

### 3.1 Introduction

This chapter explains about how to develop of Micro Hydro Generator System with used battery based system. This chapter also will include project flow, flow chart, block diagram to develop Micro Hydro Generator system used battery based system. It also will cover about based component of MHGS, hardware and software implementation.

# **3.2 Hardware Development**

This project

#### **3.2.1** Mechanical System Design

#### 3.2.2 Electrical System Design

#### **3.3 Basic Components of MHGS**

This project is using battery based system so basic components to develop of micro hydro generator system is turbine, alternator, battery, charger controller and inverter.

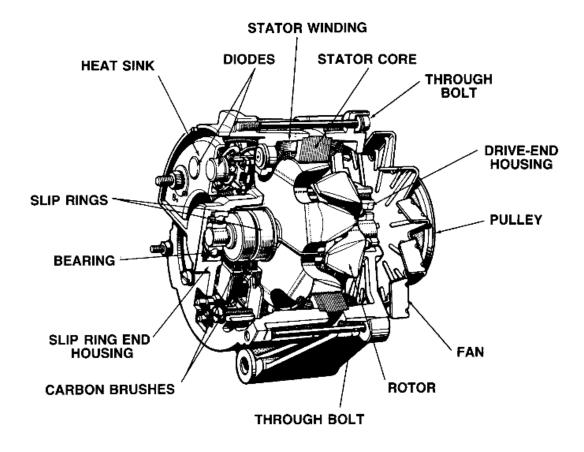

#### 3.3.1 Alternator

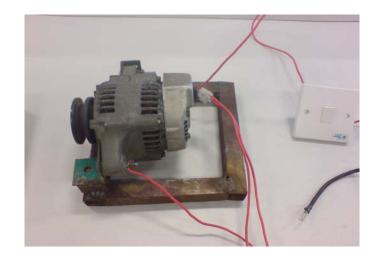

Alternator which has a built in rectifier to convert the generated AC signal to a DC signal. The specified turbines which convert mechanical energy into electrical energy use an alternator that outputs a DC signal. The DC signal is then sent to the battery where, along with the batteries a monitor will be needed this way you can determine how much electricity the turbine is generating, the consumption of that energy and battery capacity. Based on figure 3.3

Figure 3.3 Automotive Alternator

### 3.3.2 Battery

Deep cycle batteries are best to use for any renewable energy system. Batteries Lead-acid deep cycle batteries are usually used in hydro system. Deep cycle batteries are designed to withstand repeated charge and discharge cycles. The amount of batteries you use in your Micro-Hydro system will depend on your needs. The input voltage to the batteries in a battery based system commonly ranges from 12 to 48 Volts DC View our battery section to see how to calculate your needs.

### 3.3.3 Charge Controller

A charge controller is connected with the battery operation to prevent overcharging of the batteries. In the event of a power outage excess electricity could be produced and the charge controller would absorb the excess energy to protect the batteries. Hydro systems with lead-acid batteries require protection from overcharge and over-discharge.

#### 3.3.4 Inverter

A battery bank does not enable users to live with all the conveniences of modern living, as most appliances use high voltage AC (alternating current) while batteries can supply only DC (direct current). Inverters are used to convert DC to AC so that stored battery power may be used as needed by appliances and other loads. Modern inverters are available in virtually any wattage capacity, in recreational and commercial grades, in a variety of DC voltages, and with the220-240VAC, 50 Hz output for the rest of the world and 120VAC 60 Hz output for North American applications.

#### 3.3.5 Ballast Load

A ballast load takes the excess energy produced that is no longer needed to keep the batteries charged, and diverts it to a waste load. Most of the time, we will find dump loads consisting of water heater elements or air heaters. A ballast load is a very important component to the system.

#### 3.3.6 Turbines

Turbines are commonly used today to power micro generator system. The moving water strikes the turbine blades, much like a waterwheel, to spin a shaft. But turbines are more compact in relation to their energy output than waterwheels. There also have fewer gears and require less material for construction. Low head, low flow turbines may be difficult to find, and may have to be custom-made. There are two general types of turbines like impulse and reaction.

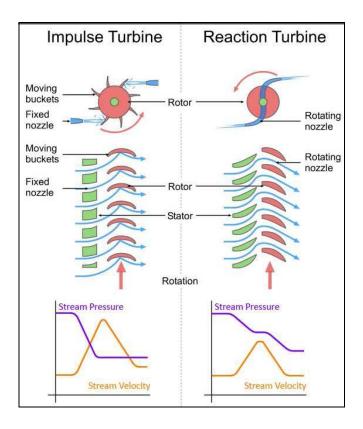

#### 3.3.6.1 Impulse Turbine

Impulse turbines, which have the least complex design, are most commonly used for high-head micro hydro system. The most common types of impulse turbines include the Pelton wheel and the Turgo wheel. That mean, the Pelton wheel uses the concept of jet to create energy. Pelton wheel turbines are also available in various sizes and operate best under low-flow and high-head condition. Another impulse turbine is Turgo impulse wheel is an upgraded version of the Pelton. The size of Turgo is half the size of the Pelton. Turgo wheel moves twice as fast. It is also needs few or no gears and good reputation for trouble-free operation. The Turgo can operate under low flow condition but requires a medium or high head.

#### 3.3.6.2 Reaction Turbine

Reaction turbines, which are highly efficient, depend on pressure rather than velocity to produce energy. All blades of the reaction turbine maintain constant contact with the water. These turbines are often used in large-scale hydropower sites. Because of their complexity and high cost, reaction turbines aren't usually used for micro hydropower projects. An exception is the propeller turbine, which comes in many different designs and works much like a boat's propeller. Propeller turbines have three to six usually fixed blades set at different angles aligned on the runner. The bulb, tubular, and Kaplan tubular are variations of the propeller turbine. The Kaplan turbine, which is a highly adaptable propeller system, can be used for micro hydro sites.

#### **3.4** Software Implementation

3.4.1 MicroCode Studio (PBP) Compiler

# 3.4.2 UP00B PIC USB Programmer

# 3.4.3 Programming the PIC 16F877 Microcontroller

# 3.5 Summary

The concept and method development of MHGS have been described in this chapter. Flow chart is very important before start the project. All the components of this

project must check specification and test. In Chapter 4 present more detail about result and discussion.

**CHAPTER 4**

# **RESULT AND DISCUSSION**

## 4.1 Introduction

This chapter explains about result and discussion for test automotive alternator with AC motor. This chapter also will discuss about data collection by using Tachometer for measure speed of motor and digital multimeter for measure voltage at alternator.

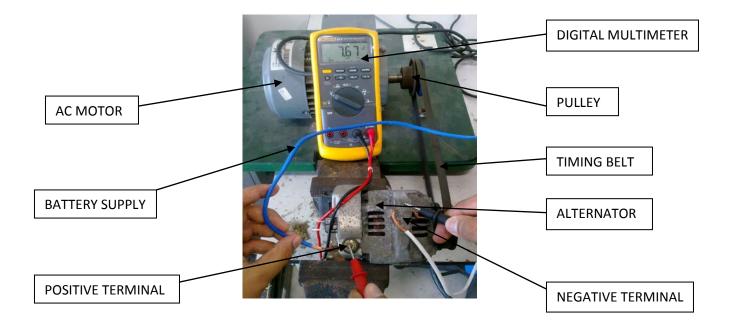

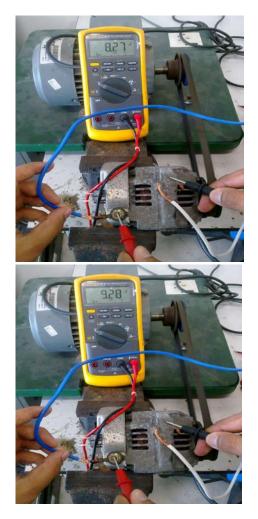

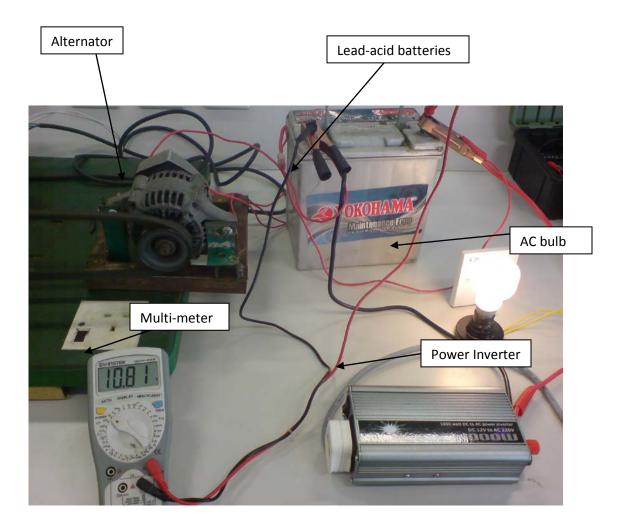

Figure 3: Testing Alternator using AC motor

# 4.2 Alternator Output

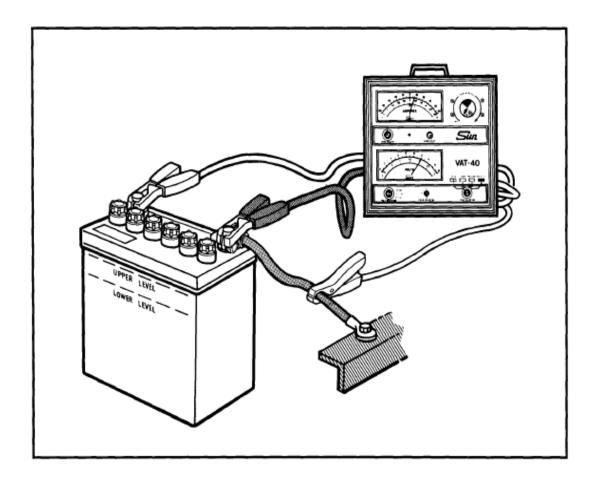

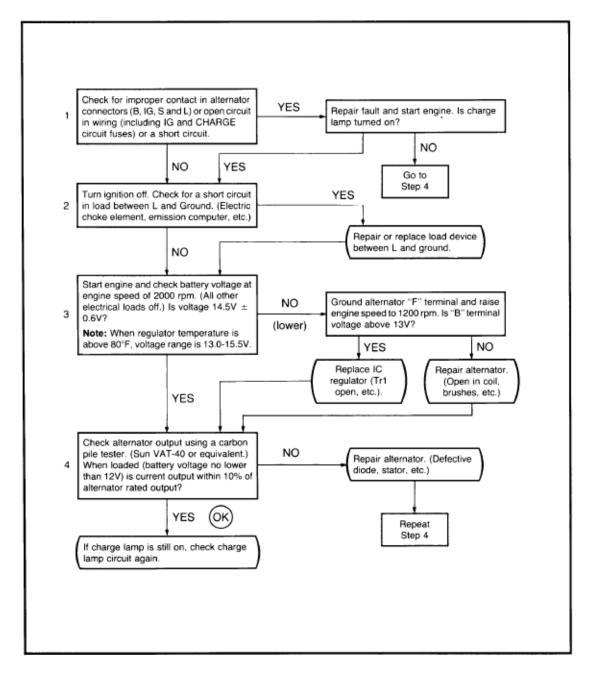

Based on Figure 3 (a), (b), (c), (d) alternator used is automotive alternator with specification speed is 1800 rpm, voltage is 14.0 VDC and current is 45A. The specification of AC motor is 1380 rpm and connected inverter to control their speed. We also used timing belt to joined alternator and AC motor.

Figure 3 (a) Figure 3 (c)

Figure 3 (b)

Figure 3 (d)

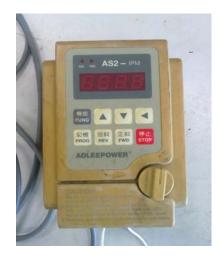

Figure 4: Inverter control speed

Figure 5: Tachometer measured speed motor (RPM)

Figure 6: Battery lead acid

| SPEED (RPM) | VOLTAGE DC (V)      |  |

|-------------|---------------------|--|

| 500         | 1.4                 |  |

| 1036        | 4.3                 |  |

| 1399        | 7.75                |  |

| 1679        | 10.35               |  |

|             | 500<br>1036<br>1399 |  |

Table 1: Data Collection

Based on the Table 1 is data collection using alternator and AC motor. We control the frequency of using inverter ADLEEPOWER. It is also control the speed AC motor. We also used Tachometer to measure speed of alternator and digital Multimeter to measure voltage at alternator. We see on the table, we know that when speed increase, voltage of alternator also increase. We can't get 14 V because we used AC Motor that speed RPM of AC motor is 1380 RPM. We refer the specification of Alternator to produce 14 V, the speed of alternator must 1800 RPM. So the speed of alternator is effect of Voltage. We also know that the voltage alternator must be higher than voltage of battery for charge the battery.

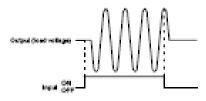

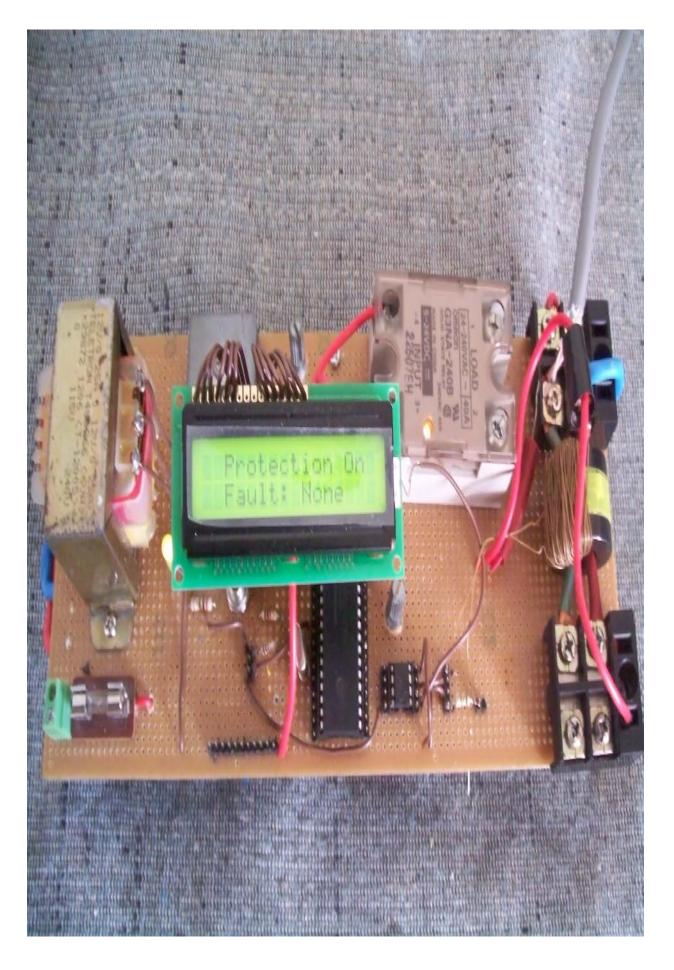

### 4.3 Charge Controller Circuit

# 4.5 **Project Results**

## 4.6 Summary

The preminalary result and discussion of data collection of alternator concept have been described in this chapter. The most important thing is to make sure that alternator can be function to charge the battery. The next Chapter is

## **CHAPTER 5**

### CONCLUSION

## 5.1 Introduction

As a conclusion, the system is not difficult to operate and maintain. This project is almost always more cost-effective than any other form of renewable power. The proposed Micro- Hydro Generator System (MHGS) will work properly as designed and will produce output power as high as 1kW or more and can be used for lighting, bulk, and battery charge and electronics devices. Another thing, the advantage of using Micro hydro system is to protect the environment and also non polluting energy source that has provided reliable power in the past and is one of the most promising renewable energy sources for the future. Lastly, for long term this project, in case for the commercialization especially in Malaysia.

### 5.2 Future Development

5.3 Costing and Commercialization

5.3.1 Costing

5.3.2 Commercialization

5.4 Conclusion

### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 **Project Background**

Micro-Hydro Generator Systems (MHGS) convert the energy of moving water into electricity. Generator systems convert from mechanical to electrical energy. This project is to develop a Micro-Hydro generator system using battery based system to generate power. The battery based system that we will use is Lead-acid deep cycle batteries. This battery can be charge and discharge system. The prime mover of this project is water that means source of water pressure from a present water tank and pipes to turn a turbine then the turbine spins an alternator and electricity is produces to charge the battery. Then an alternator converts the mechanical energy from the turbine into electrical energy. Many other components may be in a system, but it all begins with the energy already within the moving water. Other renewable energy source, such as solar and wind, can be used to produce electrical power. The choice of energy source depends on several factors, including availability, economic and energy and power requirements. Micro hydro power is almost always more cost-effective than any other form of renewable power. Micro hydro designates projects with power output of less than 500W. This project is also using a Programmable Interface Controller (PIC) and power electronic components in designing hardware. In the end of the project, the proposed micro hydro-generator can work properly as designed and produce output power as high as 500W or more and can be used for lighting, bulk, and battery charger and electronics devices.

## **1.2 Problem Statements**

Hydro generator system in market is huge and high cost and no micro hydro generator in the market. The problem also is less use of renewable energy source that convenient to supply for load. Difficulty to get data, meaning that lot of data have to be assumed because of there is no real site to survey, to make the calculations on site and to collect all the data needed and any more.

### **1.3** Objectives of Project

The objectives of this project are:

- i. To produce electricity using renewable source of energy.

- ii. To implement the use of Programmable Intelligent Circuit (PIC) and Power Electronics switch in designing hardware.

- iii. To provide clean, environmentally friendly electricity in rural communities.

### **1.4** Scope of project

The scope of this project is:

- i. To develop of Micro-Hydro Generator System using automotive alternator.

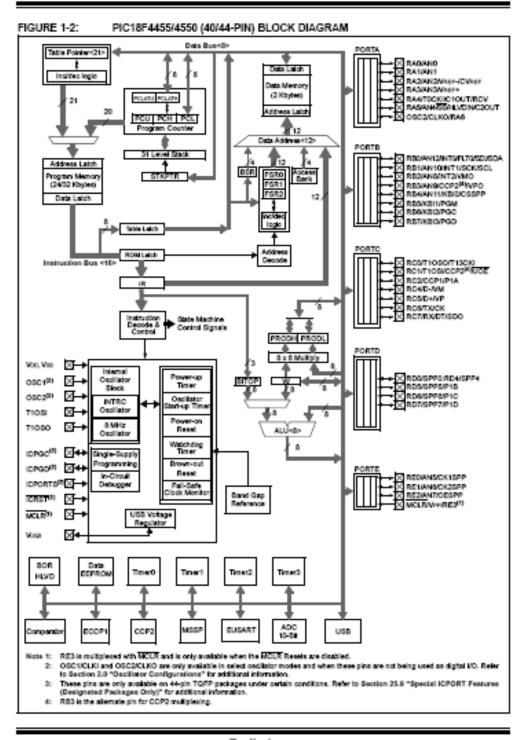

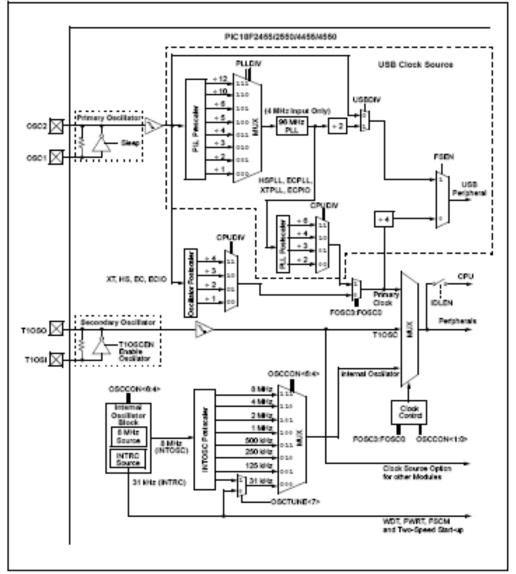

- ii. Using PIC 18F4550 microcontroller as a control circuit.

- iii. Produce output power at least 500W

### **1.5** Literature Review

Micro hydro power was once the world's prominent source of mechanical power for manufacturing. Micro hydro is making a comeback for electricity generation in homes. This system of the Micro hydro can be divide by two is Battery base systems and AC- Direct System [1].

The battery base system is power can be supplied by a micro hydro system in two ways. In a battery-based system, power is generated at a level equal to the average demand and stored in batteries. Batteries can supply power as needed at levels much higher than that generated and during times of low demand the excess can be stored. If enough energy is available from the water, an AC-direct system can generate power as alternating current (AC). This system typically requires a much higher power level than the battery-based system. The input voltage to the batteries in a battery-based system commonly ranges from 12 to 48 Volts DC. If the transmission distance is not great then 12 Volts is often high enough. A 24 Volt system is used if the power level or transmission distance is greater. If all of the loads are inverter-powered the battery voltage is independent of the inverter output voltage and voltages of 48 or 120 may be used to overcome long transmission distances. Although batteries and inverters can be specified for these voltages, it is common to convert the high voltage back down to 12 or 24 Volts (battery voltage) using transformers or solid state converters.[1]

Most battery-based systems use an automotive alternator. If selected carefully, and rewound when appropriate, the alternator can achieve very good performance. A rheostat can be installed in the field circuit to maximize the output. Rewound alternators can be used even in the 100–200 Volt range.[1]

Micro hydro power is best where water supply is continuously available. Where supply is seasonal it may still be cost effective to install micro hydro as a stand-alone system. This will depend on whether the cost of installing the system is offset by the savings made during the period when the creek is flowing. Another renewable system, or a generator, will be required when water is not available.[2]

## **1.6** Thesis Outline

This report contains 5 chapters which is every chapter have its own purpose. After viewing the entire chapter in this report, hopefully the viewer can understand the whole system design for this project.

Chapter 1 describe on the background of the project, problem statement, objectives, scope of the project and the literature review that referred to in the development of Microhydro Generator System (MHGS).

Chapter 2 is focused to the theory of the Microhydro Generator System (MHGS) where it described about operation of MHGS and measuring of head, flow and potential

power. In this chapter also include about theory overview of Micro hydropower potential in Malaysia. Lastly, this chapter also includes advantages and disadvantages of MHGS.

Chapter 3 elaborated more on the method of micro hydro generator system. Besides it also describe the hardware development that divide by two design which is mechanical system design and electrical system design. This chapter also include the functions of each components used in the system and operation such as alternator, battery, charger controller, inverter, load and turbine.

Chapter 4 presents the data and experimental about result and discussion while in development process. The results of this project are also accompanied by the discussion for each problems statement and reflect to the objective of this project.

Lastly in Chapter 5, in this chapter the conclusion has been made for the project from the whole aspect and there are also suggestions to improve the micro hydro generator system in the future, in case for the costing and commercialization. **CHAPTER 2**

### **MICRO-HYDRO GENERATOR SYSTEM (MHGS)**

## 2.1 Introduction

This chapter explains about a theory of Micro Hydro Generator System (MHGS) included operation of MHGS, measuring of head, flow rate and potential power produces so that the reader will get a clear idea how the MHGS is working. To achieve that first we need to study more about MHGS and doing more research about the MHGS operation. This chapter also includes overview of Micro Hydropower potential in Malaysia.

### 2.2 **Operation of MHGS**

A Micro Hydro Generator System (MHGS) convert the energy of moving water into electricity. Instead, a portion of a stream or river is temporarily diverted into a pipe system and to the micro hydro turbine and generator. It is then returned to its source. Because of this these types of system have far less impact on the environment than large scale hydro schemes. Micro hydro generator systems use the force of running water to turn turbine blades, which spin a shaft connected to a generator. These systems are best suited to rural sites, and can be set up wherever water falls from a higher lever to a lower level, such as a waterfall, hillside, stream, or where a reservoir discharges into a river. The type of turbine required will depend on the 'head' (the vertical fall) and the flow rate of the water. There are two basic of turbines such as impulse and reaction. These turbines are more details explanation in Chapter 3.

#### 2.2.1 Measuring of Head

Generally, the distance the water falls depends on the steepness of the terrain the water is moving across, or the height of a dam the water is stored behind. The farther the water falls, the more power it has. In fact, the power of falling water is 'directly proportional' to the distance it falls. In other words, water falling twice as far has twice as much as energy. It is important to note we are only talking about the vertical distance the water falls. The distance the water travels horizontally is consequential only in expense of the system and friction losses. Head is usually measured in 'feet'.

#### 2.2.2 Measuring of Flow Rate

More water falling through the turbine will produce more power. The amount of water available depends on the volume of water at the source. Power is also 'directly proportional' to river flow, or flow volume. A river with twice the amount of flowing water as another river can produce twice as much energy. This is also effect of choice a size of pipelines. Flow volume is usually measured in 'gallons per minute', or 'GPM'.

#### 2.2.3 Measuring of Potential Power

The amount of power available from a micro hydro generator system is directly related to the flow rate, head and the force of gravity. Once we have determined the usable flow rate (the amount of flow we can divert for power generation) and the available head for our particular site, we can calculate the amount of electrical power we can expect to generate. This is calculated using the following equation [2]:

Pth = Q x H x g Pth = Theoretical water power output in W Q = Usable flow rate in  $m^3/s$ H = Gross head in m g = Gravitational constant (9.8 m/s<sup>2</sup>)

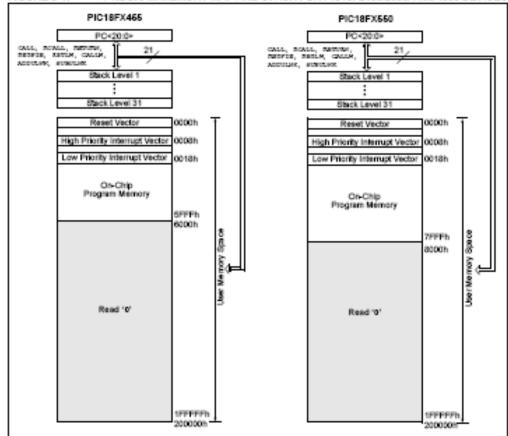

#### 2.3 Overview of Micro Hydropower Potential in Malaysia

Malaysia comprises of two distinct regions which are West Malaysia covering Peninsula Malaysia and East Malaysia covering North Borneo. In total, both regions cover land area of 330 000 sq. km in which 58% is lowland areas and 42% is highland areas [5]. The highland areas in Malaysia are created by numbers of well known ranges. In Peninsula Malaysia, the highland areas are created by ranges such as Titiwangsa, Tahan, Bintang, Kledang, and Pantai Timur. Barisan Titiwangsa range is the main range which is considered as the backbone of Peninsula. In Sarawak, the highland areas were created mainly by Tama Abu, Iran and Kapuas Hulu ranges. In Sabah the highland areas were created by Crocker, Maitland and Brassey. With average rainfall of 2540 mm in Peninsula, 2630 mm in Sabah and 3850 mm in Sarawak, Malaysia bless with abundant streams and rivers flowing from the highland areas created by these ranges [6]. Combinations of highland area with huge river networks promise Malaysia with a lot of micro hydropower potential. Figure 2.3 shows the map of Peninsular Malaysia.

Figure 2.3 Map of Peninsular Malaysia

## 2.4 Advantages of MHGS

The advantages of MHGS is efficient energy, meaning that it only takes a small amount of flow or a drop as low as two feet to generate electricity with micro hydro. Electricity can be delivered as far as a mile away to the location where it is being used. Secondly, reliable electricity source, meaning that hydro produce a continuous supply of electrical energy in comparison to other small-scale renewable technologies. Lastly, the advantage of MHGS is no reservoir required, meaning that the water passing through the generator is directed back into the stream with relatively little impact on the surrounding ecology.

## 2.5 Disadvantages of MHGS

The disadvantages of MHGS is suitable site characteristic required, meaning that factor to consider are distance from the power source to the location where energy is required, stream size and balance system component like inverter, batteries and controller. Second disadvantage is energy expansion not possible, meaning that the size and flow of small streams may restrict future site expansion as the power demand increases. Lastly, environmental impact, meaning that the ecological impact of small-scale hydro is minimal, however the low-level environment effect must be taken into consideration before construction begins.

## 2.5 Summary

From this Chapter 2, we can see that before we develop the Micro Hydro Generator System (MHGS), we must know to measure of head and flow rate include the pipes. That is important to calculate output power of the system. Besides that, we also know overview of micro hydropower potential in Malaysia that means suitable to install of micro hydropower depend on land area. In this chapter also explain about advantages and disadvantages of using MHGS.

## **CHAPTER 3**

#### DEVELOPMENT OF MICROHYDRO GENERATOR SYSTEM (MHGS)

### 3.1 Introduction

This chapter explains about how to develop of Micro Hydro Generator System. This chapter also will include hardware development system which is this system can divide by two design to develop Microhydro Generator system used battery based system. It also will cover about basic component of MHGS such as alternator, battery, charge controller, power inverter, ballast load and turbine. The hardware and software implementation also include about MicroCode Studio (PBP) Compiler, UP00B PIC USB Programmer device.

### **3.2** Hardware Development

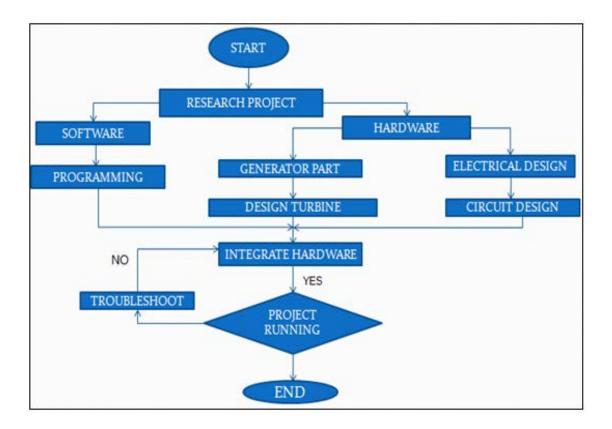

The main project development of Microhydro Generator System (MHGS) is hardware development. The hardware developments are included the mechanical system design and electrical system design.

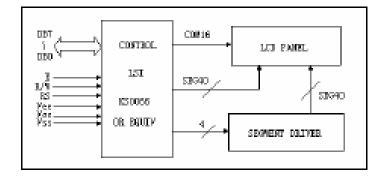

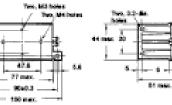

## 3.2.1 Mechanical System Design

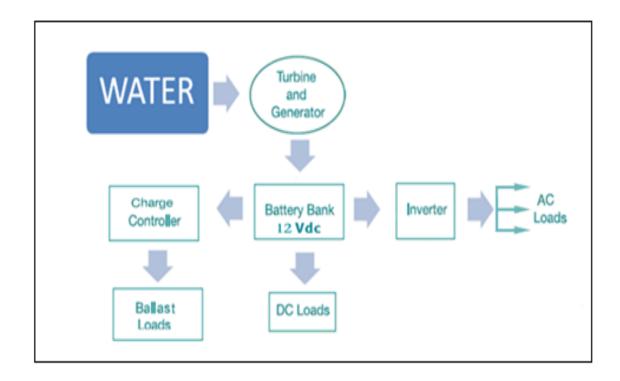

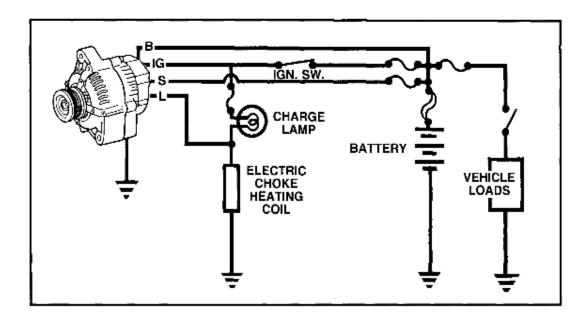

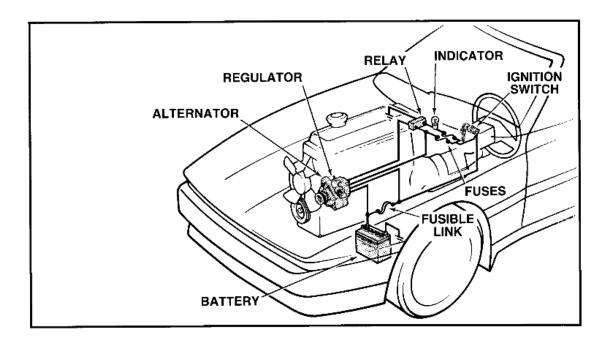

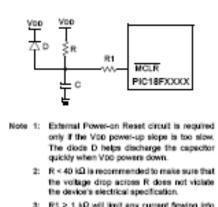

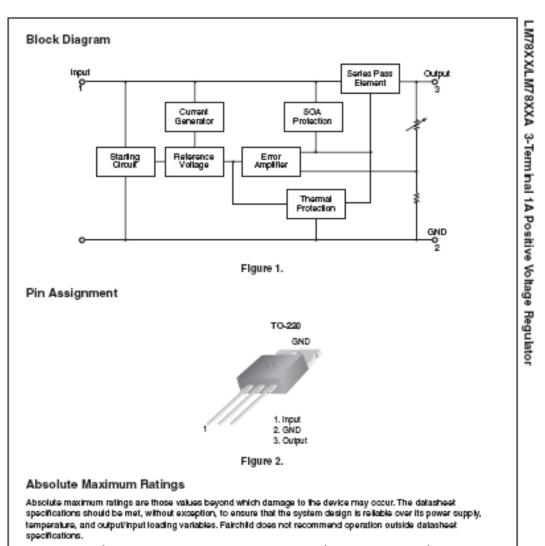

From this mechanical System design, Figure 3.1 shows that block diagram of Microhydro Generator System (MHGS). This system is included the prime mover as renewable source of energy is water. This project is used impeller turbine. The turbine and generator is connected to the battery. This project is used alternator that functions to charge the battery. The system charging of battery, voltage at generator must higher than voltage at battery. This project also used lead acid battery is rating voltage and current is 12V 45AH. The Lead-acid batteries require protection from overcharge and over-discharge. The charge controller in this project is operated that to prevent overcharging of the batteries. The ballast load in this system takes the excess energy produced that is no longer needed to keep the batteries charged, and diverts it to a waste load. This system also used power inverter that functions convert from DC to AC voltage.

Figure 3.1: Block Diagram of Microhydro Generator System (MHGS)

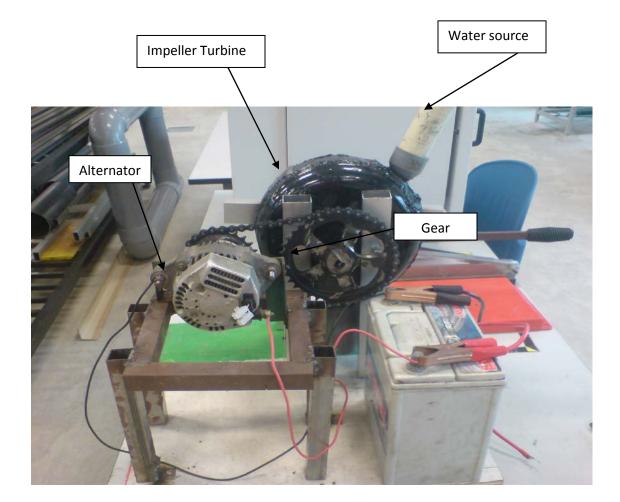

Figure 3.2 show that the hardware system of MHGS. The design is used impeller as a turbine. The gear is connected by shaft at impeller turbine to rotate the alternator using gear. In micro hydro system, water turns a wheel to rotate a turbine connected alternator using gearing concept and produce electricity. These projects want to more rotate and high speed to charge the battery. The concept of charging system, when the charging system's output is greater than that needed by the vehicle, it sends current into the battery to maintain the batter's state of charge.

Figure 3.2: Hardware System of MHGS

Figure 3.3 show that this operation system of MHGS using AC Motor. Before we installed at turbine, we must test using the AC Motor. Alternator is connected at the AC Motor to charge the battery. The power inverter is connected at lead-acid batteries to convert voltage from 12VDC to 220VAC. Power inverters are used to convert DC to AC so that stored battery power may be used as needed by appliances and other loads. The multi-meter at this figure is function to measure range of the voltage at lead-acid batteries. Voltage increase when speed of alternator is increase.

Figure 3.3: Operation System of MHGS using AC Motor

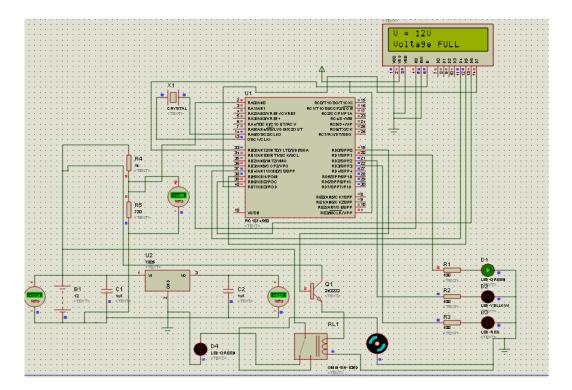

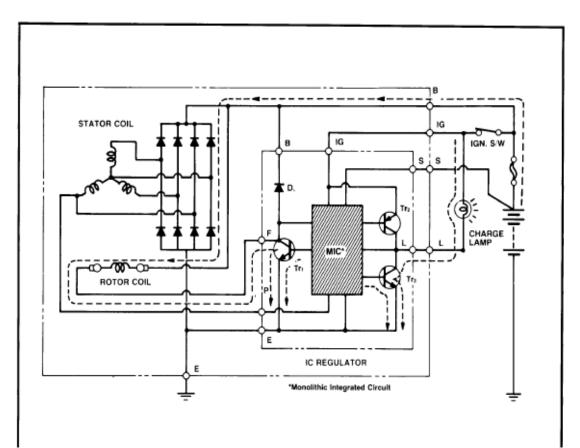

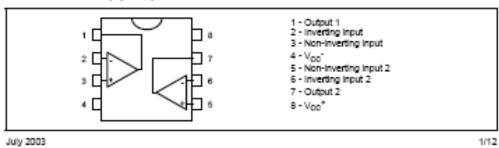

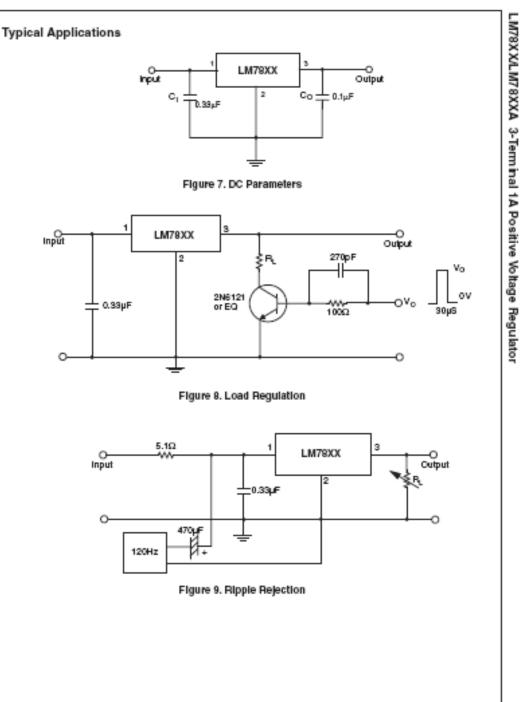

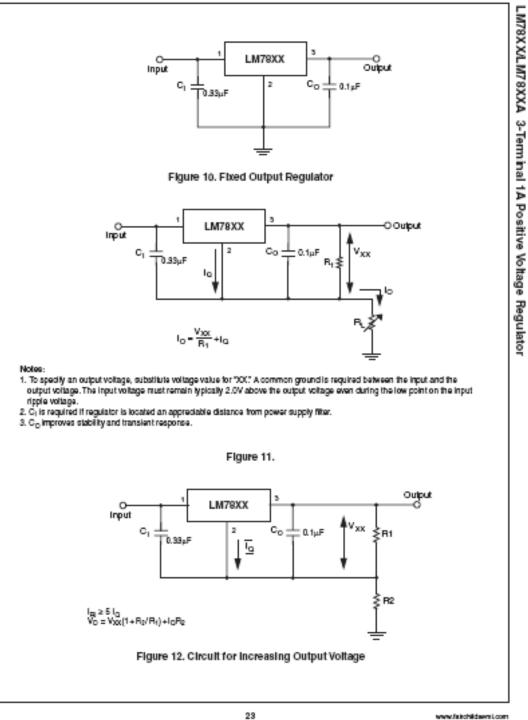

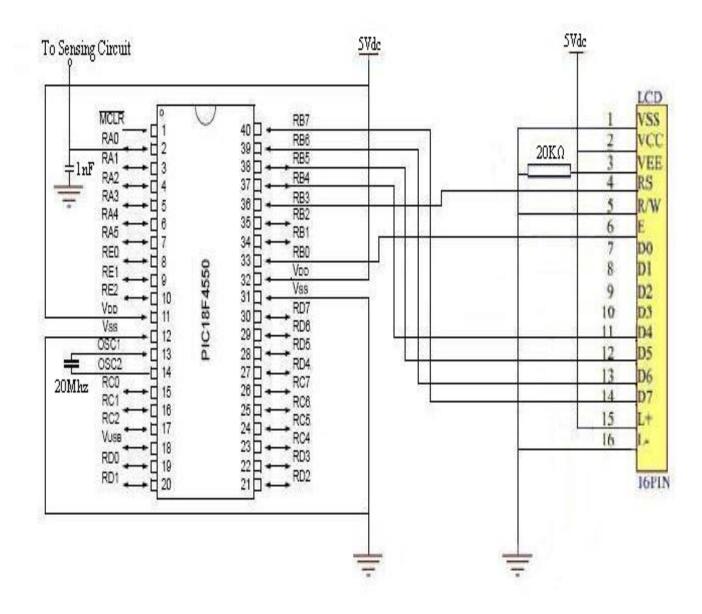

## 3.2.2 Electrical System Design

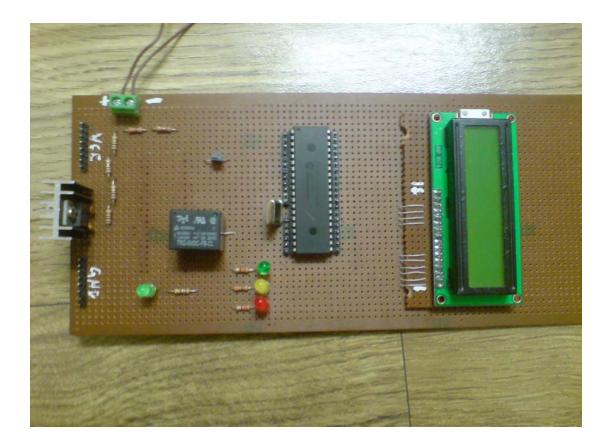

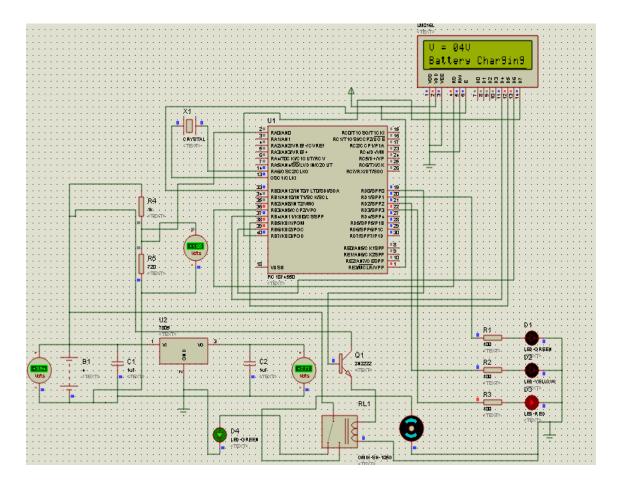

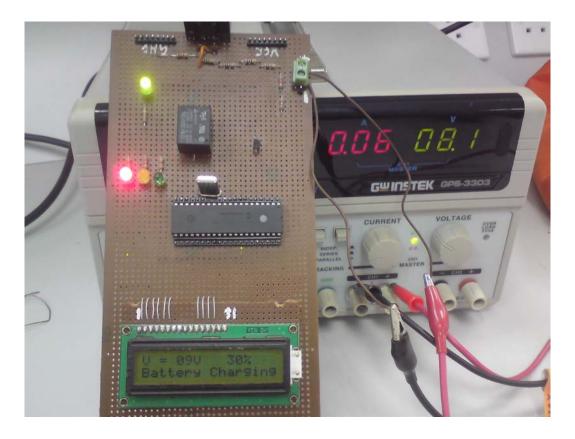

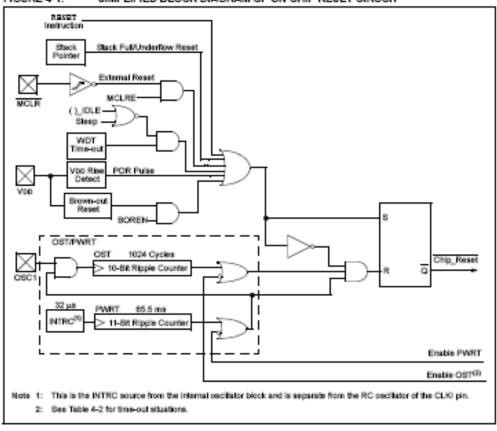

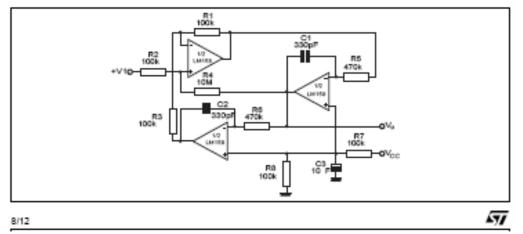

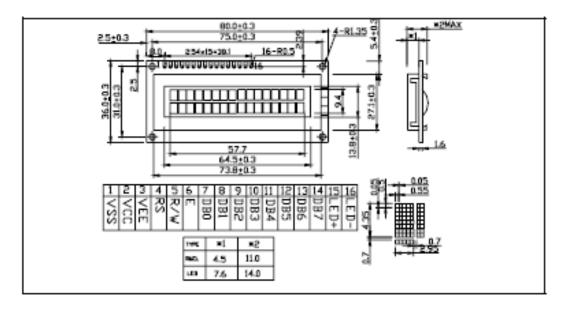

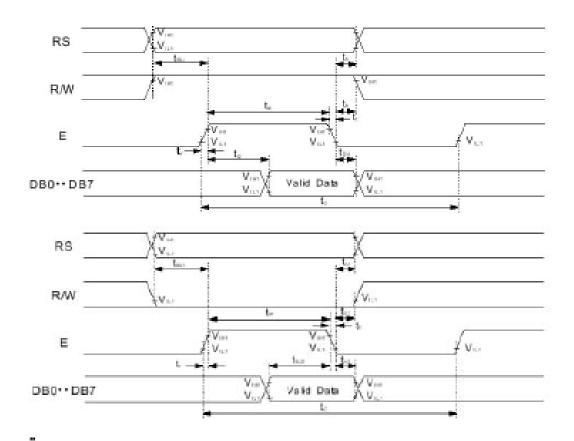

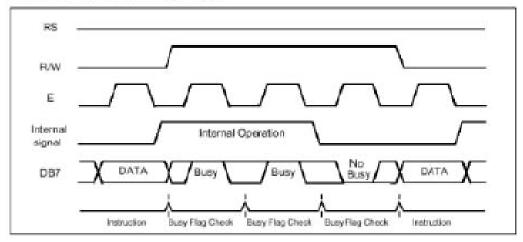

The second part of this project is electrical system design. Figure 3.4 show that the circuit charge controller. This project is used PIC 18F4550 as microcontroller. The components for whole this circuit is used such as LCD display, crystal, resistor, capacitor, transistor, LM7805, relay 5V, LED and DC motor 12V. The LCD is used to display rating voltage at the battery. The LED green, yellow and red as signal for this system. This circuit is operation base on voltage supply. When battery low, LCD can display Battery Charging and LED Red is shown.

Figure 3.4: Circuit charge controller using PIC18F4550

## **3.3** Basic Components of MHGS

This project is using battery based system so basic components to develop of Microhydro Generator System (MHGS) is turbine, alternator, battery, charger controller, ballast load, power inverter and turbine. This topic can explain more detail about the function for each component.

## 3.3.1 Alternator

An alternator differs from a dc motor in that it contains no permanent magnet. Figure 3.5 shows that alternator which has a built in rectifier to convert the generated AC signal to a DC signal. The specified turbines which convert mechanical energy into electrical energy use an alternator that outputs a DC signal. The DC signal is then sent to the battery where, along with the batteries a monitor will be needed this way you can determine how much electricity the turbine is generating, the consumption of that energy and battery capacity.

Figure 3.5: Automotive Alternator

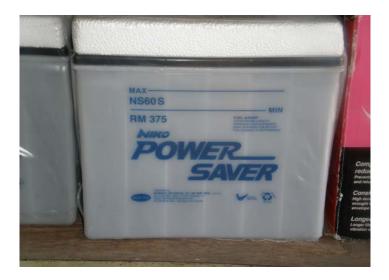

## 3.3.2 Battery

Deep cycle batteries are best to use for any renewable energy system. Figure 3.6 show that, Batteries Lead-acid deep cycles are usually used in hydro system. Deep cycle batteries are designed to withstand repeated charge and discharge cycles. The amount of batteries in Micro-Hydro system will depend on our needs. The input voltage to the batteries in a battery based system commonly ranges from 12 to 48 Volts DC.

Figure 3.6: Lead-acid batteries

## 3.3.3 Charge Controller

A charge controller is connected with the battery operation to prevent overcharging of the batteries. In the event of a power outage excess electricity could be produced and the charge controller would absorb the excess energy to protect the batteries. Hydro systems with lead-acid batteries require protection from overcharge and over-discharge.

## 3.3.4 Inverter

A battery bank does not enable users to live with all the conveniences of modern living, as most appliances use high voltage AC (alternating current) while batteries can supply only DC (direct current). Figure 3.7 show that inverters are used to convert DC to AC so that stored battery power may be used as needed by appliances and other loads. This power inverter is 1000W capacity to the load. Modern inverters are available in virtually any wattage capacity, in recreational and commercial grades, in a variety of DC voltages, and with the220-240VAC, 50 Hz output for the rest of the world and 120VAC 60 Hz output for North American applications.

Figure 3.7: Inverter

#### 3.3.5 Ballast Load

A ballast load takes the excess energy produced that is no longer needed to keep the batteries charged, and diverts it to a waste load. Most of the time, we will find dump loads consisting of water heater elements or air heaters. A ballast load is a very important component to the system.

## 3.3.6 Turbines

Turbines are commonly used today to power micro generator system. The moving water strikes the turbine blades, much like a waterwheel, to spin a shaft. But turbines are more compact in relation to their energy output than waterwheels. There also have fewer gears and require less material for construction. Low head, low flow turbines may be difficult to find, and may have to be custom-made [3]. There are two general types of turbines like impulse and reaction. Figure 3.8 show that the waterwheel is part of this system. This waterwheel has diameter 0.15m and 12 blades.

## Figure 3.8: Waterwheel

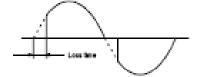

#### **3.3.6.1** Impulse Turbine

Impulse turbines, which have the least complex design, are most commonly used for high-head micro hydro system. The most common types of impulse turbines include the Pelton wheel and the Turgo wheel. That mean, the Pelton wheel uses the concept of jet to create energy. Pelton wheel turbines are also available in various sizes and operate best under low-flow and high-head condition. Another impulse turbine is Turgo impulse wheel is an upgraded version of the Pelton. The size of Turgo is half the size of the Pelton. Turgo wheel moves twice as fast. It is also needs few or no gears and good reputation for trouble-free operation. The Turgo can operate under low flow condition but requires a medium or high head.

#### 3.3.6.2 Reaction Turbine

Reaction turbines, which are highly efficient, depend on pressure rather than velocity to produce energy. All blades of the reaction turbine maintain constant contact with the water. These turbines are often used in large-scale hydropower sites. Because of their complexity and high cost, reaction turbines aren't usually used for micro hydropower projects. An exception is the propeller turbine, which comes in many different designs and works much like a boat's propeller. Propeller turbines have three to six usually fixed blades set at different angles aligned on the runner. The bulb, tubular, and Kaplan tubular are variations of the propeller turbine. The Kaplan turbine, which is a highly adaptable propeller system, can be used for micro hydro sites [4].

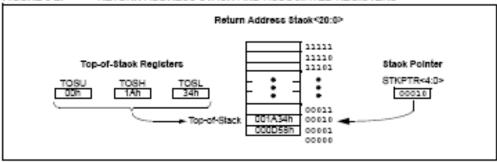

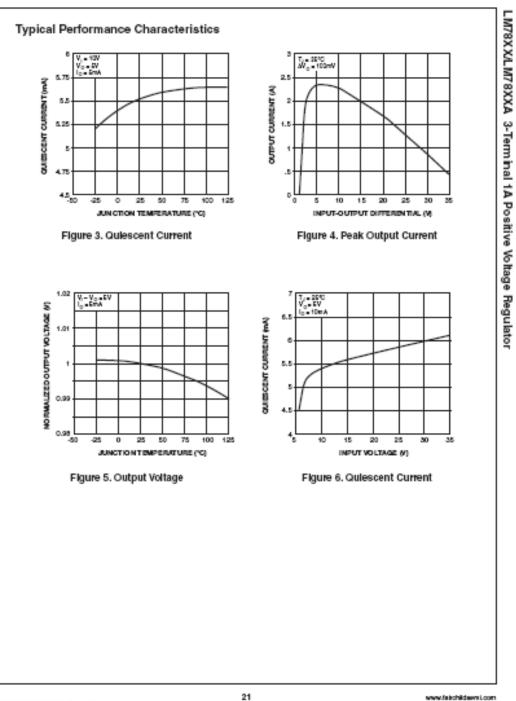

Figure 3.9 show that, Impulse and reaction turbine are two most widely used methods of obtaining energy from water, there is another version which is a hybrid of two. Called a Crossflow turbine, it converts energy from both the kinetic energy of water flow and the pressure loss of the flow. It does this by performing the flow, at the entrance of the turbine, into a rectangular jet and forcing this jet onto the blades of the turbine. The orientation of the turbine axis is perpendicular to the flow, and the turbine itself is hollow. Therefore, after the flow has struck the blades of the turbine, it falls through the center axis and strikes the blade again on the bottom side of the turbine. This imparts a loss of pressure in the flow and thus imparts more energy into the turbine [2].

Figure 3.9: Comparisons of Impulse and Reaction Turbine

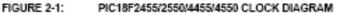

## **3.4** Software Implementation

This section will discuss about software which has been implemented in this project which are MicroCode Studio PicBasic Pro (PBP) Compiler for programming PIC18F4550, Proteus 7 Profesional for designing the circuit and simulation for the programming and also UP00B PIC USB Programmer for writing the programming language into the PIC18F4550

## 3.4.1 MicroCode Studio (PBP) Compiler

MicroCode Studio is a powerful, visual Integrated Development Environment (IDE) with In Circuit Debugging (ICD) capability designed specifically for microEngineering Labs PICBASIC<sup>TM</sup> and PICBASIC PRO<sup>TM</sup> compiler.

The main editor provides full syntax highlighting of your code with context sensitive keyword help and syntax hints. The code explorer allows you to automatically jump to include files, defines, constants, variables, aliases and modifiers, symbols and labels, which are contained within your source code. Full cut, copy, paste and undo is provided, together with search and replace features.

- Full syntax highlighting of your source code

- Quickly jump to include files, symbols, defines, variables and labels using the code explorer window

- Identify and correct compilation and assembler errors

- View serial output from your microcontroller

- Keyword based context sensitive help

- Support for MPASM

Below is the step to use the using MicroCode Studio software in charge controller and display LCD:

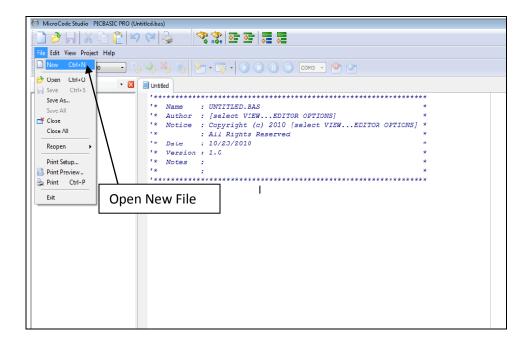

## **Step 1: Opening New File**

The first step to use the Microcode Studio is open the new file to create the program.

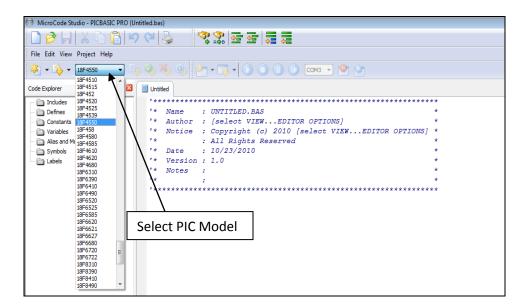

# **Step 2: Selecting PIC Model**

The second step is selecting the PIC model to use.

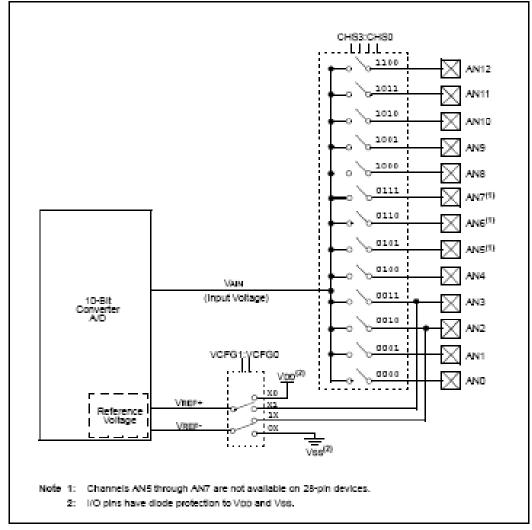

# **Step 3: ADC Coding**

After open the new file and select the PIC model, the third step is write the ADC coding.

| 向 MicroCode Studio - PICBASIC PRO (Icd5V.pbp)                |                                                              |  |  |  |

|--------------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| □ ▷ □ × □ □ □ ∨ ○ ↓ ♥ 20 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |                                                              |  |  |  |

| File Edit View Project Help                                  |                                                              |  |  |  |

| 🏝 + 💫 + 16F877 🐁 🜭 🧏 🖓 + 🟹 + 🕥 🛈 🛈 🔘 Coms - 😬 💽              |                                                              |  |  |  |

| Code Explorer 🔹 🔀                                            | lcd5v                                                        |  |  |  |

| - 📄 Indudes                                                  | ****                                                         |  |  |  |

| 🖻 🧰 Defines                                                  | '* Name : UNTITLED.BAS *                                     |  |  |  |

| D OSC                                                        | '* Author : [select VIEWEDITOR OPTIONS] *                    |  |  |  |

| ··· D ADC_bits                                               | '* Notice : Copyright (c) 2010 [select VIEWEDITOR OPTIONS] * |  |  |  |

| D ADC_CLOCK                                                  | '* : All Rights Reserved *                                   |  |  |  |

| D ADC_SAMPLEUS                                               | '* Date : 10/6/2010 *                                        |  |  |  |

| - 🗀 Constants                                                | '* Version : 1.0 *                                           |  |  |  |

| - 📄 Variables                                                | '* Notes : *                                                 |  |  |  |

| <ul> <li>Alias and Modifiers</li> </ul>                      | **                                                           |  |  |  |

| - 📄 Symbols                                                  | ***************                                              |  |  |  |

| - 🛅 Labels                                                   |                                                              |  |  |  |

|                                                              | DEFINE OSC 8                                                 |  |  |  |

|                                                              | DEFINE ADC_bits 8                                            |  |  |  |

|                                                              | DEFINE ADC_CLOCK 3 ADC Coding                                |  |  |  |

|                                                              | DEFINE ADC_SAMPLEUS 50                                       |  |  |  |

|                                                              |                                                              |  |  |  |

|                                                              | ADCON1 = 0                                                   |  |  |  |

|                                                              | ADCON0 = \$11000001                                          |  |  |  |

|                                                              |                                                              |  |  |  |

|                                                              |                                                              |  |  |  |

|                                                              |                                                              |  |  |  |

|                                                              |                                                              |  |  |  |

# Step 4: Define Variable & LCD Display

The fourth step is before start the all program we must define variable and declare instruction LCD display

| (iii) MicroCode Studio - PICBASIC PRO (coding18f4550.pbp) |                                                                         |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|

| ○ ▷ ▷ □ ▷ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○                   |                                                                         |  |  |  |

|                                                           |                                                                         |  |  |  |

| File Edit View Project Help                               |                                                                         |  |  |  |

| 🏂 🛪 🎝 🛪 (18F4550 💼 🖏 🌭 🦄 😓 🎽 🛪 🏹 🛪 🚫 🔘 🕕 💿 💷 🚳 🗠 🕐        |                                                                         |  |  |  |

| Code Explorer 🔹 🔀                                         | coding18f4550                                                           |  |  |  |

| Includes                                                  | <pre>'* Notice : Copyright (c) 2010 [select VIEWEDITOR OPTIONS] *</pre> |  |  |  |

| 🚊 🛅 Defines                                               | '* : All Rights Reserved *                                              |  |  |  |

| LCD_DREG                                                  | '* Date : 10/17/2010 *                                                  |  |  |  |

| - D LCD_DBIT                                              | '* Version : 1.0 *                                                      |  |  |  |

| — D LCD_RSREG                                             | '* Notes : *                                                            |  |  |  |

| - D LCD_RSBIT                                             | 1* · · · · · · · · · · · · · · · · · · ·                                |  |  |  |

| - D LCD_EREG                                              | ***************************************                                 |  |  |  |

| - D LCD_EBIT                                              | DEFINE LCD_DREG PORTB ' Set LCD data port to PORTB                      |  |  |  |

| D LCD_BITS                                                | DEFINE LCD_DBIT 4 ' Set data starting bit to 4                          |  |  |  |

| D LCD_LINES                                               |                                                                         |  |  |  |

| LCD_COMMANDUS                                             | DEFINE LCD_RSREG PORTB' Set RS register port to PORTB                   |  |  |  |

| LCD_DATAUS                                                | DEFINE LCD_RSBIT 3 ' Set RS register bit to 3                           |  |  |  |

| - D OSC                                                   |                                                                         |  |  |  |

| <ul> <li>D ADC_bits</li> </ul>                            | DEFINE LCD_EREG PORTB 'Set E register port                              |  |  |  |

| - D ADC_CLOCK                                             | DEFINE LCD_EBIT 0 'Set E register bit to 0                              |  |  |  |

| ADC_SAMPLEUS                                              |                                                                         |  |  |  |

| 🗄 🛅 Constants                                             | DEFINE LCD_BITS 4 ' Set 4 bit operation                                 |  |  |  |

| conv1                                                     | DEFINE LCD LINES 2 ' Set number of LCD rows                             |  |  |  |

| conv2                                                     |                                                                         |  |  |  |

| 🖃 🧰 Variables                                             | DEFINE LCD_COMMANDUS 2000 Define LCD                                    |  |  |  |

| Res                                                       | DEFINE LCD_DATAUS 255                                                   |  |  |  |

| volts1                                                    |                                                                         |  |  |  |

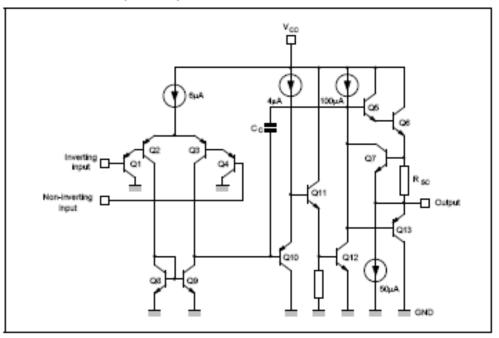

**Step 6: Compile Program & Error Checking**

| (m) MicroCode Studio - PICBASIC PRO (cc | dinq18f4550.pbp)                                       |          |  |  |

|-----------------------------------------|--------------------------------------------------------|----------|--|--|

|                                         |                                                        |          |  |  |

| File Edit View Project Help             |                                                        |          |  |  |

|                                         | 3 🗞 🎭 🎼 • 🟹 • 🜔 🔘 🕕 💿 coms 🔹 🐏 🖄                       |          |  |  |

|                                         |                                                        |          |  |  |

| Code Explorer 🔹 🔀                       | Coding 18f4550                                         |          |  |  |

| 🛅 Includes                              | * Notice : Copyright (c) 2010 [select VIEWEDITOR OPTIO | NS] *    |  |  |

| 🖃 🛅 Defines                             | '* : All Rights Reserved                               | *        |  |  |

| D LCD_DREG                              | '* Date : 10/17/2010                                   | *        |  |  |

|                                         | '* Version : 1.0                                       | *        |  |  |

| D LCD_RSREG                             | '* Notes :                                             | *        |  |  |

| D LCD_RSBIT                             | ** :                                                   | *        |  |  |

|                                         | MPASM v4.01                                            | ****     |  |  |

|                                         | EFINE LCD DREG PORTB ' Set LCD MPASM v4.01             |          |  |  |

| LCD_BITS                                | DEFINE LCD DBIT 4 ' Set data sta Assembling            |          |  |  |

| LCD_LINES                               | CODING~1.ASM                                           |          |  |  |

| LCD_COMMANDUS                           | DEFINE LCD_RSREG PORTB' Set RS 1                       |          |  |  |

| D LCD_DATAUS                            | DEFINE LCD_RSBIT 3 ' Set RS reg:                       |          |  |  |

| D OSC                                   | Errors:                                                | Compile  |  |  |

| ··· D ADC_bits                          | DEFINE LCD_EREG PORTB 'Set E reg Warnings:             | complie  |  |  |

| D ADC_CLOCK                             | DEFINE LCD_EBIT 0 'Set E registe Reported:             | Progress |  |  |

| D ADC_SAMPLEUS                          | Suppressed:                                            | Flogless |  |  |

| 🖃 🚞 Constants                           | DEFINE LCD_BITS 4 ' Set 4 bit op Messages:             |          |  |  |

| C conv1                                 | DEFINE LCD_LINES 2 ' Set number Suppressed:            |          |  |  |

| conv2                                   |                                                        |          |  |  |

| 🖃 🚞 Variables                           | DEFINE LCD_COMMANDUS 2000                              |          |  |  |

| ···· 💟 Res                              | DEFINE LCD_DATAUS 255                                  | Error    |  |  |

| ···· 💟 volts1                           |                                                        |          |  |  |

| 💟 volts2                                | DEFINE OSC 4                                           | Poport   |  |  |

| V adval1                                | DEFINE ADC_bits 8                                      | Report   |  |  |

| 🛅 Alias and Modifiers                   | DEFINE ADC_CLOCK 3                                     |          |  |  |

| 🛅 Symbols                               | DEFINE ADC_SAMPLEUS 50                                 |          |  |  |

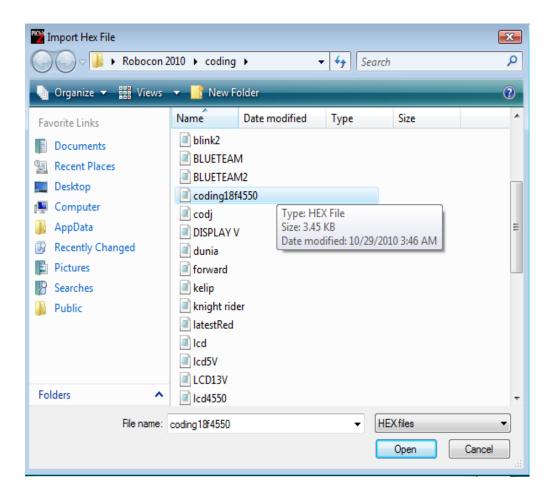

After all steps are done, the PIC is ready to write by using UP00B PIC USB Programmer.

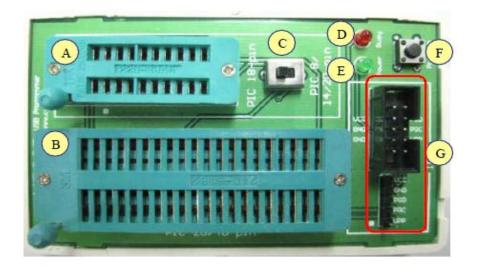

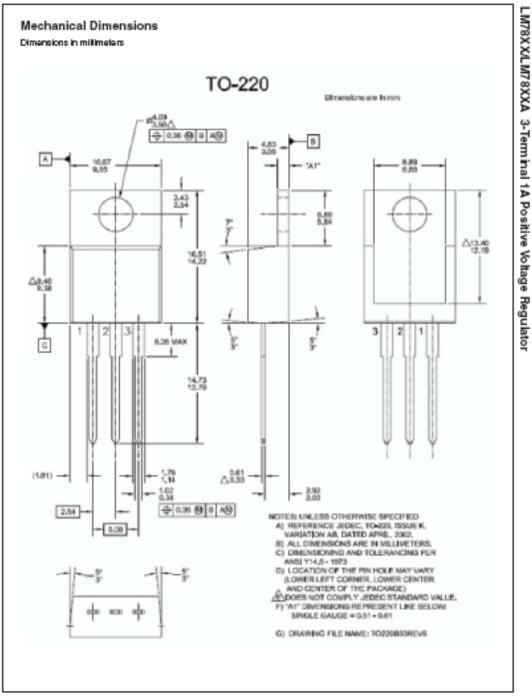

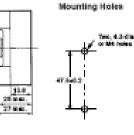

### 3.4.2 UP00B PIC USB Programmer

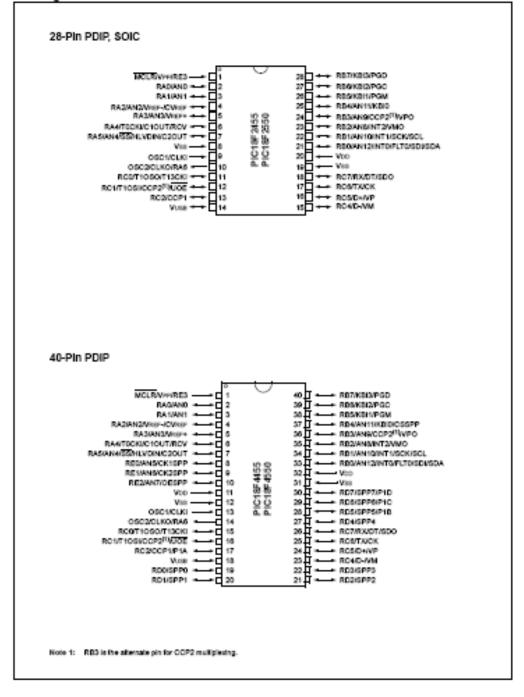

UP00B is the enhanced version of UP00A. As PIC MCU is gaining its popularity in market for student and hobbyist, more low cost and user friendly programmer is needed. Previous USB PIC Programmer, UP00A is obsolete because it cannot support Windows Vista, fail to program many new PIC MCU, further the firmware is not upgradeable. Hence, UP00B is now introduced to you! It comes with two ZIP sockets to offer program loading to 8 pin, 18 pin, 28 pin and 40 pin PIC MCU (8 bit) by using Microchip PICKit2 software. It offers a low cost yet convenience USB PIC Programmer to user. Loading program to PIC MCU will be as easy as 1, 2, 3. It has been designed with capabilities and features as below:

- USB powered, no extra power needed to load program

- Two ZIF sockets (20 pins and 40 pins) to ease program loading process

- Support most 8pin, 18pin, 28pin and 40pin PDIP 8 bit PIC MCU

- Support windows XP and Vista

- Support Intel and AMD based system

- Support Laptop and desktop PC

Package Including:

- 1 USB Programmer UP00B

- 1 USB Cable (B type)

- 1 Software Installation and User's Manual CD Rom

Figure 3.10: CYTRON USB Programmer

# 3.4.2.1 Board Layout

| Table 3.1 | Function of Board Layout Identified |

|-----------|-------------------------------------|

|-----------|-------------------------------------|

| Label | Function                                           |

|-------|----------------------------------------------------|

| A     | ZIF Socket 20 pins                                 |

| В     | ZIF Socket 40 pins                                 |

| С     | Switch selector for PIC pins of ZIF Socket 20 pins |

| D     | Busy LED                                           |

| E     | Power LED                                          |

| F     | Program Button                                     |

| G     | Connector for ICSP                                 |

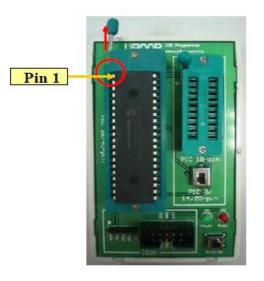

Figure 3.11: Board Layout USB Programmer UP00B

## 3.4.2.2 Installation (Software)