#### **PAPER • OPEN ACCESS**

### Temperature characteristics of Gate all around nanowire channel Si-TFET

To cite this article: Firas Natheer Abdul-kadir Agha et al 2021 J. Phys.: Conf. Ser. 1755 012045

View the <u>article online</u> for updates and enhancements.

**1755** (2021) 012045

doi:10.1088/1742-6596/1755/1/012045

# **Temperature characteristics of Gate all around nanowire channel Si-TFET**

## Firas Natheer Abdul-kadir Agha<sup>1</sup>, Yasir Hashim<sup>2,\*</sup>, Waheb Abduljabbar Shaif Abdullah<sup>3</sup>

<sup>1</sup>Department of Electrical Engineering, College of Engineering, University of Mosul, Mosul, Iraq

<sup>2</sup>Department of Computer Engineering, Faculty of Engineering, Tishk International University, Erbil-Kurdistan, Iraq

<sup>3</sup>Faculty of Electrical & Electronics Engineering Technology, Universiti Malaysia Pahan, 26600 Pekan, Pahang Darul Makmur, Malaysia

\*yasir.hashim@ieee.org

**Abstract**. This paper study the impact of working temperature on the electrical characteristics of gate all around nanowire channel Si-TFET and examines the effect of working temperature on threshold voltage, transcondactance (gm),  $I_{\rm ON}/I_{\rm OFF}$  ratio, drain induced barrier lowering (DIBL), and sub-threshold swing (SS). The (Silvaco) simulation tool has been used to investigate the working temperature on the Si-TFET characteristics. The temperature range in this study is from -25 to 150 °C. The results indicate that the TFET must work in electronic circuits with the lower temperature as possible to get better performances. Furthermore, the TFET has good performances as a temperature nanosensor with diode connection mode under ON conditions.

#### 1. Introduction

In nanotechnology regime, The nanowire Tunnel Field Effect Transistors (TFET) are good alternatives to replace the existing Metal Oxide Semiconductor Field Effect Transistor (MOSFET) and it has a potential candidate for electronic devices, because the TFET have low OFF current ( $I_{OFF}$ ), small subthreshold swing (less than 60 mV/decade), low power consumption and reduced Short Channel Effects (SCE) [1-5].

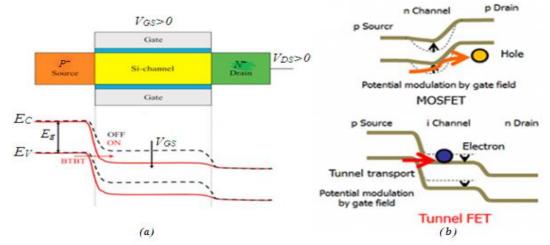

The physical mechanics of tunnel field effect transistor TFET is using quantum band-to-band tunneling effect (BTBT) to transport carriers from a valence band of Source (P) to a valance band of Drain (D) through the channel or Gate (G) which is totally different from conventional MOSFET devices that use thermionic emission as shown in Figure1[6-10]. There are two models for tunneling mechanism, local and non-local tunneling model, the non-local model can be considered very important model in the designing of TFET because it keeps sub-threshold swing up to 60 mV/decade [11]. Since the current in the TFETs is done by the valence band of the source that comprise lower energy the TFETs are considered thermally cooled regime and the SS are not anticipated to be limited

Published under licence by IOP Publishing Ltd

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

1755 (2021) 012045

doi:10.1088/1742-6596/1755/1/012045

by the temperature. On the other hand, in the case of ON current ( $I_{ON}$ ) for the device, the applied voltage at the gate ( $V_{GS}$ ) will pulls back the energy band of the channel area and decrease the height of the barrier. Subsequently the carriers will tunnel from source to channel regions and hence the tunneling current will constitute [10].

Fig. 1. (a) Schematic of a TFET cross section and band diagram along the channel in ON and OFF states, (b) Comparison between TEFET and MOSFET according to operation principle (b).

The basic structure of a TFET is consist of three region (P-I-N), where source is highly doped with (P+) type, channel is intrinsic doped (I) and drain is highly doped with (N<sup>+</sup>) type and oxide layer is surround the Si-channel as shown in Figure1.a [12]. A positive voltage is applied at the drain and gate terminals, and biases is reversed between source-channel and drain-channel. TFET fabricated in different types of topologies, depending upon tunneling junction electric field and gate electric field.

There are two most important types of topologies used in fabricated TFET:

- 1. Lateral Tunnel Field Effect Transistor (LTFET).

- 2. Vertical Tunnel Field Effect Transistor (VTFET).

But vertical TFETs have a smaller OFF state current and have a steeper sub-threshold swing as compared to lateral counterparts [13-14]. Surround gate or GAA structure as shown in Figure 2 permits more channel width per unit area of silicon nanowire [15].

#### 2. Methodology

A gate all around TFET device has been designed and simulated by using Silvaco program by the specified dimension of nanometers scales. Figure 3 shows a cross-sectional area of the geometric structure and limited dimension of the device. Where the radius of the silicon intrinsic channel is (R), the gate length  $(L_G)$  and thickness of the gate oxide dielectric material SiO2 is  $(T_{ox})$ .

Doping concentration of the channel is  $10^{17}$  per cm<sup>-3</sup> and doping concentrations for drain and source is  $10^{19}$  per cm<sup>-3</sup> respectively. The dimensions of the channel  $L_G$  is 200 nm, radius of the channel R is 35nm, SiO<sub>2</sub> thickness  $T_{ox}$  is 4.5 nm and dimensions for drain and source lengths ( $L_S$  and  $L_D$ ) is 80 nm respectively, other parameters illustrated in Table 1.

In this work, we used various temperature degrees, from -50°C to 150°C step-up by 25°C. The voltage taken at the drain terminal ( $V_{DS}$ ) is 1v and voltage applied at the gate terminal (VGS) is varied from 0v to 1v in step-up 0.1v. Various parameters and characteristics of GAA Si TFET are investigated and verified using Silvaco. Some of these parameters are  $I_{ON}/I_{OFF}$ , SS, DIBL (Drain Induced Barrier Lowering) and transconductance ( $g_m$ ), where the drain current  $I_D$  of a TFET, it dependence on the temperature degree according to the following equation [16]:

**1755** (2021) 012045

doi:10.1088/1742-6596/1755/1/012045

$$I_D = A \cdot V_{Gs}^2 \cdot exp\left(-\frac{B}{V_{GS}}\right)$$

.....(1)

$A \propto E_G^{-0.5}$

$B \propto E_G^{1.5}$

A and B are carrier effective mass and tunneling barrier

A relationship between the variations of the energy gap (Eg) with temperature (T) in semiconductors is proposed as [17]:

$$E_G = E_{0-}\alpha T^2/(T+\beta)$$

.....(2)

Where  $\alpha$  and  $\beta$  are constants.

As temperature decreases, the EG increases, leading to parameter B will increase and hence a decreasing tunneling current (ID). Also, the sub-threshold swing SS dependence upon the temperature degree as following equation [18]:

$$SS \cong \left(1 + \frac{c_d}{c_{ox}}\right) ln \frac{\kappa T}{q}$$

.....(3)

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \quad \dots \quad (4)$$

Finally, the transconductance (g<sub>m</sub>) will increased when ID increases as proposed as [18]:  $g_m = \frac{\partial I_D}{\partial V_{GS}} \dots (4)$  So, the temperature effect is dominated on performance of the TFETs due to the temperature variation of the band gap (EG). The important of this work lies in achieving low SS, low OFF state current, increase  $I_{\text{ON}}/I_{\text{OFF}}$  and increase gm at low-temperature degree.

Table- I: Parameters of simulated TFET

| Parameter                       | Value                       |

|---------------------------------|-----------------------------|

| Channel radius (R)              | (35) nm                     |

| Oxide thickness $(T_{OX})$      | (4.5)  nm                   |

| Channel Doping (P)              | $10^{17}  \mathrm{cm}^{-3}$ |

| Drain Doping (P <sup>+</sup> )  | $10^{19}  \mathrm{cm}^{-3}$ |

| Source Doping (N <sup>+</sup> ) | $10^{19}  \mathrm{cm}^{-3}$ |

| Drain length                    | 80 nm                       |

| Source length                   | 80nm                        |

| Channel length (L)              | (200) nm                    |

Fig. 2. GAA Si TFET structure

1755 (2021) 012045

doi:10.1088/1742-6596/1755/1/012045

#### 3. Results and Discussion

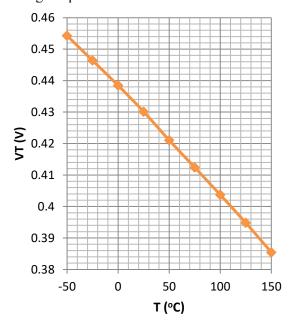

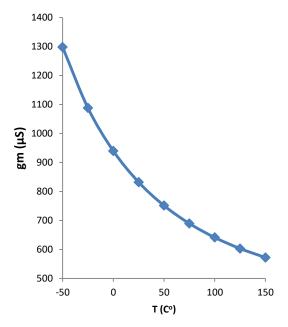

Figure 3 illustrates the dependence of threshold voltage on working temperature and the  $V_T$  decreases linearly with increasing working temperature. Figure 4 shows the variation of transconductance channel  $(g_m)$  of TFET with working temperature, the gm decreases exponentially with increasing working temperature.

Fig. 3. The dependence of threshold voltage on working temperature

Fig. 4. The variation of transconductance channel  $(g_m)$  of TFET with working temperature.

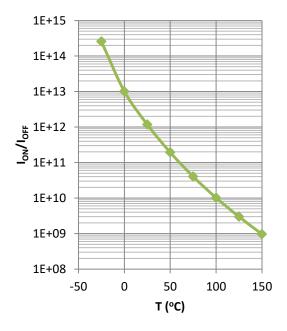

Figure 5 illustrates the impact of working temperature on drain ON to OFF current ( $I_{\rm ON}/I_{\rm OFF}$ ) ratio, which considered is one of the most significant parameters for using transistors in digital electronic circuits. According to Figure 5, the maximum ratio of  $I_{\rm ON}/I_{\rm OFF}$  occurs at -25 °C and then exponentially decreased. For numerous transistor applications in electronic circuit such as logic gates and amplifiers, the highest value of  $I_{\rm ON}/I_{\rm OFF}$  current ratio is the best for these applications. So, the findings of ON to OFF drain current ratio ( $I_{\rm ON}/I_{\rm OFF}$ ) with temperature characteristics may lead to use of TFET in electronic circuits with lower temperature to obtain a higher  $I_{\rm ON}/I_{\rm OFF}$  ratio as possible.

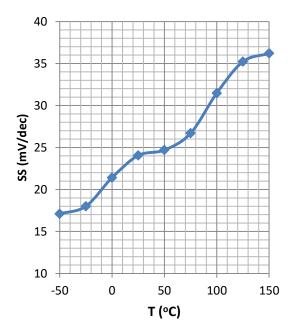

Figure 6 illustrates the change in subthreshold swing (SS) with working temperature. SS mathematically is known as the slope inverse of the transfer characteristics ( $I_d$  versus  $V_g$ ) curve under condition that the Id in a logarithmic scale. Depending on this figure, SS increases near to be linearly with increasing environmental temperature. The minimum SS value is at -50 °C, and it is possible to define it as a best SS. It is clear that all SS values much under the ideal value of SS in normal MOSFET (60 mV/dec). The outcome of SS with working temperature might drive to the use of TFET in switching circuits with minimum temperature as possible to get lower SS and then faster switching operation.

1755 (2021) 012045

doi:10.1088/1742-6596/1755/1/012045

Fig. 5. The impact of working temperature on  $(I_{ON}/I_{OFF})$  ratio.

Fig. 6. The subthreshold swing (SS) with working temperature characteristics.

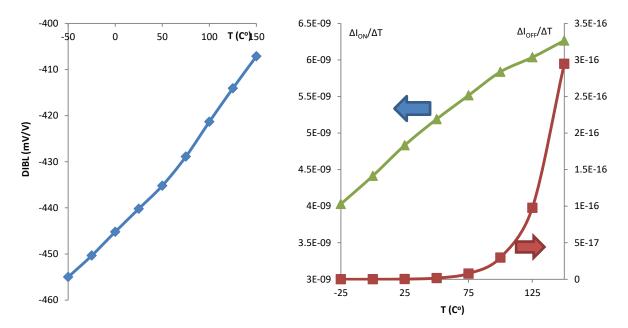

Drain induced barrier lowering (DIBL) is one of the important key parameters for test and evaluate the performances of FET structures. DIBL varied depending on environmental temperature of TFET, as shown in Fig. 7, which increases linearly as environmental temperature increases from -50 °C to 150 °C. So, the raise in working temperature has a serious effect on DIBL, making the TFET works with poor performances in electronic circuits.

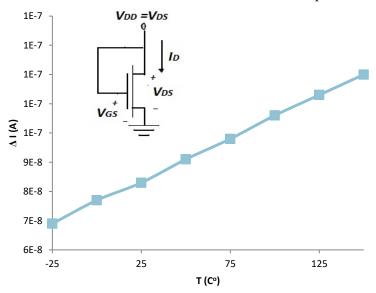

Figure 8 shows the temperature sensitivity of both OFF and ON currents with increasing environmental temperature. The evaluation of TFET as a temperature nanosensor is possible based on this figure. The OFF current temperature sensitivity ( $I_{OFF}/\Delta T$ ) increases exponentially with increasing environmental temperature, and the maximum value is  $2.94 \times 10^{-16}$  A/°C, while, the temperature sensitivity of ON current ( $I_{ON}/\Delta T$ ) increases linearly with increasing environmental temperature, and the maximum value is  $6.26 \times 10^{-9}$  A/°C. It is clear that the  $I_{ON}$  current has the higher temperature sensitivity and it is the suitable current for using the TFET as a temperature nanosensor. MOSFET structure can be used as a temperature sensor by connecting the diode mode by connecting the gate with drain (circuit in Figure 9). Fig. 9 shows the increment of current  $\Delta I$  with increasing environmental temperature at  $V_g = V_{DS} = V_{DD} = 1V$ , the  $\Delta I$  increased linearly with temperature, so, the TFET has a good performances as a temperature nanosensor.

Finally, the importance impact of working temperature on  $I_D$  in TFET could be referring to the higher carrier velocity for n-type NWs as the radius minimized [19]. Furthermore, in highly FETs scaled-down, the saturation current of drain is controlled by the effective carrier injection velocity  $(V_{inj})$  from the source to the channel. The ballistic transport does not depends on the concept of mobility, and the controlling of current will depends on the carrier injection velocity, that is a semiconductors material features.

**1755** (2021) 012045

doi:10.1088/1742-6596/1755/1/012045

Fig. 7. The DIBL with working temperature characteristics.

Fig. 8. The temperature sensitivity of both OFF and ON currents with increasing environmental temperature.

Fig. 9. The increment of current  $\Delta I$  with increasing environmental temperature at  $Vg = V_{DS} = V_{DD} = 1V$ .

#### 4. Conclusion

This paper presents the investigation of environmental temperature characteristics of TFET. Silvaco simulation tool has been used in this investigation. The findings of  $V_T$ ,  $g_m$ ,  $I_{ON}/I_{OFF}$ , SS, and DIBL with working temperature indicate that the TFET must work in electronic circuits with the lower temperature as possible to get better and lower SS and DIBL with higher  $I_{ON}/I_{OFF}$  ratio. Furthermore, the using of TFET as a temperature nanosensor must happen under the ON conditions because of the higher ON current temperature sensitivity ( $I_{ON}/\Delta T$ ), the TFET has good performances as a temperature nanosensor with diode connection mode.

**1755** (2021) 012045

doi:10.1088/1742-6596/1755/1/012045

#### References

- [1] D.K. Ferry, R. Akis, D. Vasileska, "Quantum effects in MOSFETs: use of an effective potential in 3D Monte Carlo simulation of ultra-short channel devices," IEDM Tech. Digest, pp. 287-290, 2000.

- [2] H. R. Khan, D. Mamaluy, and D. Vasileska, "Approaching optimal characteristics of 10-nm high-performance devices: A quantum transport simulation study of Si FinFET," IEEE Trans. on Elect. Dev., Vol. 55(3), pp.743-753, 2008.

- [3] Ajith Ravindran, Abraham George, C S Praveen, Nisha Kuruvilla, Gate All Around Nanowire TFET with High ON/OFF Current Ratio, Materials Today: Proceedings, Volume 4, Issue 9, 2017, Pages 10637-10642.

- [4] H. AlAriqi, W. Jabbar, Y. Hashim, H. B. Manap, "Channel Length-Based Comparative Analysis of Temperature and Electrical Characteristics for SiNWT and GeNWT", International Journal of Computing and Digital Systems, vol. 9, no. 1, pp. 87-95, 2020.

- [5] Y. Atalla, Y. Hashim, A. Ghafar, W. Jabbar, "A temperature characterization of (Si-FinFET) based on channel oxide thickness", TELKOMNIKA, vol. 17, no. 5, pp. 2475-2480, 2019.

- [6] A. Mahmood, W. Jabbar, Y. Hashim, H. B. Manap, "Effects of downscaling channel dimensions on electrical characteristics of InAs-FinFET transistor", International Journal of Electrical and Computer Engineering (IJECE), vol. 9, no. 4pp. 2902~2909, August 2019.

- [7] Koga J., Toriumi A., "Three-terminal silicon surface junction tunneling device for room temperature operation," IEEE Electron Device Lett. 1999, 20, 529–531.

- [8] Settino F., Lanuzza M., Strangio S., Crupi F., Palestri P., Esseni D., Selmi L. "Understanding the potential and limitations of tunnel fets for low-voltage analog/mixed-signal circuits", IEEE Trans. Electron Devices 2017, 64, 2736–2743.

- [9] A.C. Seabaugh, Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic", Proc. IEEE, 98 (12), (2010), 20952110.

- [10] A.M. Ionescu, H. Riel, Tunnel field-effect transistors as energy efficient electronic switches, Nature 479 (7373) (2011) 329337.

- [11] Shashi K. Dargar and Viranjay M. Srivastava, "Performance Analysis of High-k Dielectric Based Silicon Nanowire Gate-All-Around Tunneling," FET, International Journal of Electrical and Electronic Engineering & Telecommunications Vol. 8, No. 6, November 2019.

- [12] Prabhat Tamak, Rajesh Mehra "Review of Tunnel Field Effect Transistor (TFET)" Int. Res. J. Eng. Tech., Vol. 4(7), pp. 1195-1200, 2017

- [13] Kartik Ganapathi, Youngki Yoon et al., "Analysis of InAs Vertical and Lateral Band-to-Band Tunneling Transistors: Leveraging Vertical Tunneling for Improved Performance"

- [14] Z. Jiuren; et al., "Experimental Validation of Depolarization Field Produced Voltage Gains in Negative Capacitance Field-Effect Transistors", IEEE Transactions on Electron Devices, vol. 66, no. 10, pp. 4419-4424, Oct. 2019.

- [15] Praveen C S, Ajith Ravindran and Arathy Varghese. Article: Analysis of GAA Tunnel FET using MATLAB. IJCA Proceedings on International Conference on Emerging Trends in Technology and Applied Sciences ICETTAS 2015(1), September 2015, pp. 30-35.

- [16] K. K Bhuwalka, J. Schulze and I. Eisele, "A Simulation Approach to Optimize the Electrical Parameters of a Vertical Tunnel FET," IEEE Trans. Electron Devices, vol. 52, pp. 1541-1547, 2005.

- [17] S. M. Sze: Physics of Semiconductor Devices (Wiley, New York, 1981) 2nd ed.

- [18] M. I. Dewan, M. T. B. Kashem, and S. Subrina, "Characteristic analysis of triple material trigate junctionless tunnel field effect transistor," in Proc. 9th Int. Conf. on Electrical and Computer Engineering (ICECE), Dhaka, Bangladesh, 2016, pp. 333-336.

- [19] N. Neophytou, H. Kosina, and G. Klimeck, "A Comprehensive Atomistic Analysis of Bandstructure Velocities in Si Nanowires", 14th International Workshop on Computational Electronics (IWCE), 2010.