ELECTRONIC WAU CONTROLLER

NOR HASYIMAH BINTI MAT ALI

UNIVERSITI MALAYSIA PAHANG

# UNIVERSITI MALAYSIA PAHANG

| Sa                   | ya                                                                                                     | 2008/2009                                                                                 |

|----------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 54                   | NOR HASYIMAH MAT                                                                                       | SAR)<br>ALI ( 830201-06-5250 )                                                            |

|                      | engaku membenarkan tesis (Sarjana Muda/ <del>Sar</del><br>rpustakaan dengan syarat-syarat kegunaan sep |                                                                                           |

| 1.<br>2.<br>3.<br>4. | Perpustakaan dibenarkan membuat salinan                                                                |                                                                                           |

| (                    | SULIT atau kepentingan                                                                                 | klumat yang berdarjah keselamatan<br>Malaysia seperti yang termaktub<br>AHSIA RASMI 1972) |

| (                    |                                                                                                        | klumat TERHAD yang telah ditentukan oleh<br>li mana penyelidikan dijalankan)              |

|                      | $\sqrt[n]{\sqrt{\frac{1}{\sqrt{1}}}}$ TIDAK TERHAD                                                     |                                                                                           |

|                      |                                                                                                        | Disahkan oleh:                                                                            |

| T)                   | ANDATANGAN PENULIS)                                                                                    | (TANDATANGAPENYELIA)                                                                      |

| <u>Y</u> .<br>25     | amat Tetap:<br>58, KG PERMATANG BADAK,<br>150 KUANTAN,<br>MHANG                                        | IR ZULKIFLEEE KHALIDIN<br>( Nama Penyelia )                                               |

| Ta                   | rikh: 11MAY 2009                                                                                       | Tarikh: : <u>11 MAY 2009</u>                                                              |

• Tesis dimaksudkan sebagai tesis bagi Ijazah doktor Falsafah dan Sarjana secara Penyelidikan, atau disertasi bagi pengajian secara kerja kursus dan penyelidikan, atau Laporan Projek Sarjana Muda (PSM).

## ELECTRONIC WAU CONTROLLER

## NOR HASYIMAH BINTI MAT ALI

This thesis is Part Fulfillment of the Requirement for a Bachelor Degree of Electrical Engineering (Electronic)

> Faculty of Electrical & Electronic Engineering University Malaysia Pahang

> > MAY 2009

"All the trademark and copyrights use herein are property of their respective owner. References of information from other sources are quoted accordingly; otherwise the information presented in this report is solely work of the author."

| Signature | :                             |

|-----------|-------------------------------|

|           |                               |

| Author    | : <u>NOR HASYIMAH MAT ALI</u> |

Date

: <u>11 MAY 2009</u>

"I hereby acknowledge that the scope and quality of this thesis is qualified for the award of the Bachelor Degree of Electrical Engineering (Electronics)"

Signature :\_\_\_\_\_

Name : <u>IR ZULKIFLEE KHALIDIN</u>

Date : <u>11 MAY 2009</u>

To my beloved mother and father

### ACKNOWLEDGEMENT

I would like to thank my supervisor IR Zulkiflee Khalidin for this advice and support throught this project. Without his continoud support and interest, this thesis would not have been the same as presented here.

My sincere appreciation also extands to all the lecturers and staffs that have provided assistance at various occasions. Their views and tips are useful indeed.

I also would like to express my gratitude to my collegues for their full cooperation during doing this project.

I also wish acknowledgement to the people who give support direct or inderectly to the project and during the thesis writing and I also would like to thanks my beloved family for not forget to pray and giving support to me. Once again, thank you very much.

### ABSTRACT

Traditionally, after the harvesting of padi, the people will rejoice and take part in kite-flying sport, when farmers have spare time to decorate and fly these Wau. There are many type of Wau in Malaysia and it controlled by human using a rope to control the movement of this Wau. The purpose of this project is to control the Wau without using the rope. It will be control by using remote control. A remote control system for providing a remote control signal for controlling a device from a distance. This project involving hardware, software, and electrical sub-systems. The hardware required includes a flight vehicle, which is a commercial remote control.. The software systems on the ground must transmit commands, and the software in the air must process commands and data to stabilize and fly the Wau. The electrical subsystems include micro-controllers and computers required to support the software

### ABSTRAK

Kebiasaannya, selepas menuai padi, petani akan bergembira dan mengambil bahagian dalam permaianan laying-layang atau Wau yang di reka dan dibuat sendiri. Di Malaysia, terdapat pelbagai jenis Wau dan Wau tersebut akan dikawal oleh manusia dengan mengawal tali yang telah diikat pada Wau. Jadi, tujuan projek ini adalah untuk menaikkan dan mengawal Wau tersebut tanpa menggunakan tali sebaliknya ianya dikawal dengan menggunakan sistem kawalan jauh. Projek ini terdiri daripada perkakasan, perisian dan sub sistem elektrik. Perkakasan termasuklah Wau dan sistem kawalan jauh. Sistem perisan bagi alat kawalan jauh akan menghantar arahan dan sistem elektrikal pada Wau akan menerima data dan memproses data tersebut untuk membuatkan Wau terbang. Bagi sub sistem elektrik pula, terdiri daripada mikro kawalan dan computer

## TABLE OF CONTANT

| CHAPTER | TITLE                     | PAGE |

|---------|---------------------------|------|

|         | TITLE                     | i    |

|         | DECLARATION               | ii   |

|         | SUPERVISOR'S DECLARATION  | iii  |

|         | DEDICATION                | iv   |

|         | ACKNOWLEGDEMENT           | v    |

|         | ABSTRACT                  | vi   |

|         | ABSTRAK                   | vii  |

|         | TABLE OF CONTANT          | viii |

|         | LIST OF FIGURE            | xi   |

|         | LIST OF TABLE             | xii  |

|         | LIST OF SYMBOL            | xiii |

| 1       | INTRODUCTION              |      |

|         | 1.1 Background            | 1    |

|         | 1.2 Overview of Project   | 1    |

|         | 1.3 Problem Statement     | 2    |

|         | 1.4 Objectives of Project | 2    |

|         | 1.5 Scopes of Project     | 3    |

|         | 1.5.1 Transmitter         | 3    |

|         | 1.5.2 Receiver            | 3    |

|         |                           |      |

## LITERATURE REVIEW

2

| 2.1 Background                         | 5 |

|----------------------------------------|---|

| 2.1.1 Helicopter Controller            | 5 |

| 2.1.2 Transmitter and Receiver Concept | 7 |

| 2.1.3 Frequency Allocation Concept     | 7 |

## 3 METHODOLOGY

| 3.1 Background                                  | 9  |

|-------------------------------------------------|----|

| 3.2 System Hardware Components                  | 9  |

| 3.2.1 PIC Microcontroller                       | 12 |

| 3.2.2 Transmitter Receiver Modules              | 13 |

| 3.2.3 Joysticks                                 | 14 |

| 3.2.4 Joysticks Control Method                  | 15 |

| 3.2.4.1 Ascend                                  | 15 |

| 3.2.4.2 Descend                                 | 16 |

| 3.2.4.3 Steering                                | 16 |

| 3.2.5 Antenna                                   | 16 |

| 3.2.6 Servo Motor                               | 17 |

| 3.2.7 Servo Control                             | 18 |

| 3.2.8 Encoder and Decoder                       | 20 |

| 3.3 System Integration and Software             | 22 |

| 3.3.1 System Integration: Interface to Hardware | 22 |

| 3.3.1.1Joystick and A/D Converter               | 22 |

| 3.3.1.2 PWM mode in CCP Channel                 | 22 |

| 3.3.2 Communication Protocol                    | 23 |

| 3.4 Software                                    | 24 |

| 3.5 Circuit Design of the System                | 26 |

| 3.5.1 Circuit Diagram                           | 26 |

| 3.5.2 Circuit on PCB Board                      | 27 |

|   | 3.5.3 List of Components | 29 |

|---|--------------------------|----|

| 4 | DISCUSSION               |    |

|   | 4.1 Background           | 30 |

|   | 4.2 Discussion           | 30 |

| 5 | CONCLUSION               |    |

|   | 5.1 Background           | 32 |

|   | 5.2 Conclusion           | 32 |

|   | 5.3 Recommendation       | 33 |

|   | REFERENCE                | 34 |

|   | APPENDICES               |    |

| Appendices A - Data Sheet | 35 |

|---------------------------|----|

|                           |    |

## LIST OF FIGURE

FIGURE NO

TITLE

## PAGE

| 3.1  | Basic block diagram of the project                | 10 |

|------|---------------------------------------------------|----|

| 3.2  | Contents of the integrated controller             | 11 |

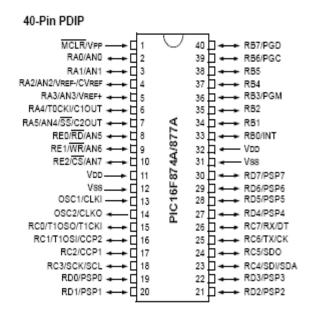

| 3.3  | PIC16F877 Pin Configuration                       | 12 |

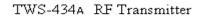

| 3.4  | RF Transmitter Schematic                          | 13 |

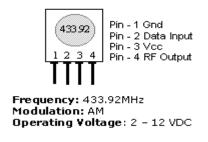

| 3.5  | RF Receiver Schematic                             | 14 |

| 3.6  | Potentiometer Joysticks                           | 15 |

| 3.7  | Servo motor circuit consist of DC driver circuit, |    |

|      | rotor and blade                                   | 18 |

| 3.8  | Servos are controlled by 1-2 ms pulses            | 19 |

| 3.9  | HT12E Pin Configuration                           | 20 |

| 3.10 | HT12D Pin Configuration                           | 21 |

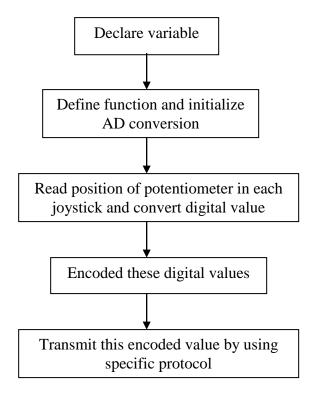

| 3.11 | Transmit Control Algorithm                        | 24 |

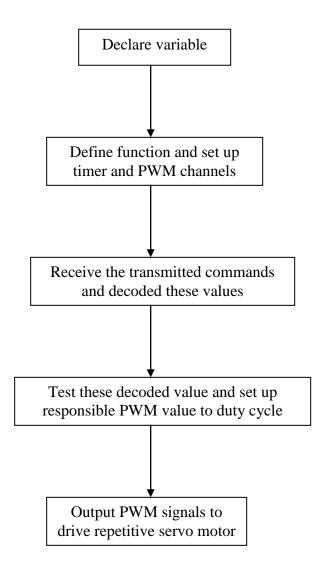

| 3.12 | Receive Control Algorithm                         | 25 |

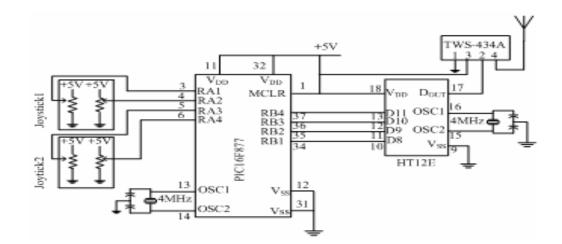

| 3.13 | Circuit Diagram for Transmitter Section           | 26 |

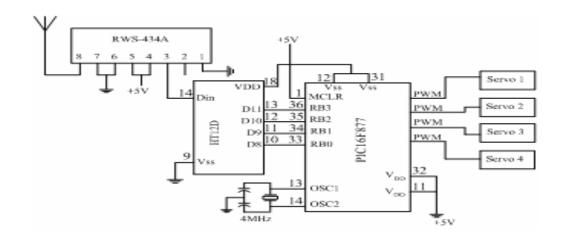

| 3.14 | Circuit Diagram for Receiver Section              | 27 |

| 3.15 | Transmitter Circuit on PCB board                  | 27 |

| 3.16 | Receiver Circuit on PCB board                     | 28 |

# LIST OF TABLE

| TABLE NO. | TITLE                                     | PAGE |

|-----------|-------------------------------------------|------|

| 3.1       | RC receiver PWM outputs                   | 11   |

| 3.2       | List of component for Transmitter Circuit | 29   |

| 3.3       | List of component for Receiver Circuit    | 29   |

## LIST OF SYMBOL

| Κ  | - | Kilo  |

|----|---|-------|

| р  | - | Pico  |

| F  | - | Farad |

| Μ  | - | Mega  |

| Hz | - | Hertz |

| Ω  | - | Ohm   |

**CHAPTER 1**

## **INTRODUCTION**

### 1.1 Background

This section explains details about an overview of project, problem statement, objectives of project, scopes of project and thesis outline.

## **1.2** Overview of project

Traditionally, after the harvesting of padi, the people will rejoice and take part in kite-flying sport, when farmers have spare time to decorate and fly these Wau. There are many type of Wau in Malaysia and it controlled by human using a rope to control the movement of this Wau.

The purpose of this project is to control the Wau without using the rope. It will be control by using remote control. A system comprising: a remote control system for providing a remote control signal for controlling a device from a distance. A controller is a hand-held device that sends radio signals to the radio receiver in the Wau Controller to tell it what to do. The controller is also called a transmitter because it transmits signals that control the movement of the Wau. For this project, the remote control used two joysticks to control the Wau. The controller is also described based on the number of actions or channels it controls.

### **1.3 Problem Statement**

The Wau usually controlled by the user using the rope to control the movement. The problem is while the strong wind coming it is difficult to control the Wau and the rope that control the Wau easily cut off. The Wau also playing only while have the wind to make it up and move in right or left direction. The solution for this problem is designed the Wau that controlled by electronic controller.

#### **1.4** Objectives of project

The kind objectives of this project are to make the Wau flying by using electronic controller that controlled by user. Besides, the Wau also can go up and down and turn left and turn right.

## **1.5** Scope of project

The scope that used in this project includes two parts which are transmitter and receiver.

### 1.5.1 Transmitter

In this project, transmitter used to transmit the digital signal from the device. Transmitter will modulate the signal and send this encoded value to the receiver via an antenna.

### 1.5.2 Receiver

Receiver used to receive the signals that transmit from transmitter by an antenna. Receiver have to amplify a low level signal as received from antenna, demodulate the signal and amplify the base band signal to a level power.

### 1.6 Thesis Outline

Chapter 1 explains the background of the project with it is an overview of project, problem statement, objectives of project and scopes of project. The transmitter and receiver are the main essential in this project.

Chapter 2 focused on the literature review. All information from journals, books and sources from website that have some attachment to this project are used as a reference to guide and help completing this project. Each of this part explains based on this finding.

Chapter 3 explains and discuss about the methodology that have been used in order to complete this project. There are two parts in this chapter which are hardware implementation and software development. The discussion will be focused on circuit design.

Chapter 4 discussed about the result obtained and limitation of the project. All discussion is concentrating on the result and performance of the device

Chapter 5 discussed the conclusion of development of this project. This chapter also discusses the recommendation for this system for future development or implementation. **CHAPTER 2**

### LITERATURE REVIEW

#### 2.1 Background

This chapter focused on the literature review for each component in this project. The entire component is described based on the finding during the completion of this project.

#### 2.1.1 Helicopter controller

This project is design basically from helicopter controller. As we know the speeds of helicopter controller is fast but for this project will modified to make the Wau operate or function with smoothly movement. It is because the project perpetuates our nature Wau although it is used modern technology. This applet models a high-attitude take off motion of a Wau with a modal controller. The x, z-axes of the spatial frame are

pointing north and down. The body x-axis is defined from the center of gravity to the nose of the Wau, and body z-axis is pointing down from the center of gravity. The motion of the Wau is controlled by the main rotor thrust, and the longitudinal tilt path angle. Flight modes represent different modes of operation of the Wau and they correspond to controlling different variables in the dynamic.

The infrared (I.R.) sensor works by using an I.R. led to emit a series of pulses of I.R. light. A sensitive circuit using a photodiode detects this signal as reflected by an obstructing object the robot might encounter. Comparators then process the signal and provide the logic for reversing the left motor. The existing robot kit is hence an excellent baseline circuit to which the microcontroller is added and provides a number of pieces of circuitry required in the final version of the robot: the I.R. sensor, motors, and associated driving transistors for the motors.

Wau can make a flight by rotating the main rotor, with the wings (blades) thereof adjusted to a certain attack angle, thus producing a lift. The steering is performed to four-axis control directions including roll, pitch, collective pitch, and yaw. The roll axis, the pitch axis, the collective axis, and the yaw axis are controlled by adjusting the rotor pitch angle of the rotating plane of the main rotor of a Wau. For this control, a swash plate, which is disposed coaxially on the rotating shaft of the main rotor and of which the three axes have the degree of freedom, is controlled by means of servomechanisms.

A steering control device suitable for a radio-controlled model, comprising a receiver for receiving three steering signals serially transmitted from a transmitter and demodulating the signals, and then outputting three servo control signals, said three steering signals including a roll steering signal, a pitch steering signal, and a collective pitch steering signal, said three servo control signals including a roll servo control signals, and a collective pitch servo control signal, and a collective pitch servo control signal, and a collective pitch servo control signal, a control signal, a pitch servo control signal, and a collective pitch servo control signal, a control signal, a pitch servo control signal, and a collective pitch servo control signal, a control signal servo control signals for three axes of rotation, said three servo control signals for three axes of rotation, said three servo drive signals for three axes of rotation, said three servo drive signals including a roll servo drive signals for three axes of rotation, said three servo drive signals for three axes of rotation, said three servo drive signals including a roll servo drive signals for three axes of rotation, said three servo drive signals including a roll servo drive signals for three axes of rotation, said three servo drive signals including a roll servo drive signals for three axes of rotation, said three servo drive signals including a roll servo drive signals for three axes of rotation, said three servo drive signals including a roll servo drive signals for three axes of rotation, said three servo drive signals including a roll servo drive signals for three axes of rotation, said three servo drive signals including a roll servo drive signals for three axes of rotation, said three servo drive signals including a roll servo drive drive drive drive signals for three axes of rotation, said three servo drive signals for three servo drive signals for

signal, a pitch servo drive signal and a collective pitch servo drive signal; a synchronous circuit for synchronizing said three servo drive signals output from said controller and outputting said three servo drive signals in parallel; and a roll servo mechanism, a pitch servo mechanism, and a collective pitch servo mechanism, which are controllably driven respectively by said three servo drive signals.

#### 2.1.2 Transmitter and Receiver Concept

A transceiver is a device that has both a transmitter and a receivers which is combined and share common circuitry or a single housing. If no circuitry is common between transmit and receive functions, the device is a transmitter-receiver. The term originated in the early 1920s. Technically, transceivers must combine a significant amount of the transmitter and receiver handling circuitry. Similar devices include transponders, transverters, and repeaters.

#### 2.1.3 Frequency Allocation Concept

The electromagnetic spectrum is an aspect of the physical world, like land, water, and air. It is a resource, limited by its usability. Use of radio frequency bands of the electromagnetic spectrum is regulated by governments in most countries, in a process known as frequency allocation or spectrum allocation. Like weather and internationally traded goods, radio propagation and RF technology do not stop at national boundaries. Giving technical and economic reasons, governments have sought to harmonies spectrum allocation standards. As a matter of physics, many objects and actions generate low-level, wide-band radiation. The frequency allocation process traditionally has not been concerned with many types of radiation.

## **CHAPTER 3**

### METHODOLOGY

#### 3.1 Background

This chapter discussed about circuit designed and components used to complete this project. The discussion will be focused on transmitter circuit that contained the joysticks, microcontroller, RF module and an antenna used to transmit a signal. For receiver circuit will focused on an antenna used to receive a signal from transmitter, microcontroller, RF module and servo motor.

#### 3.2 Hardware Components System

The overall system configuration is briefly represented in this section and the hardware used in this research and the physical integration of the components are also

described This project has two circuit which are circuit for remote control system, also called transmitter and circuit for Wau, also called receiver. Remote control system will control the Wau by sending the signal to the Wau. This system has two channels movement means first channel used to control up and down movement and second channel to make the Wau turn left or turn right.

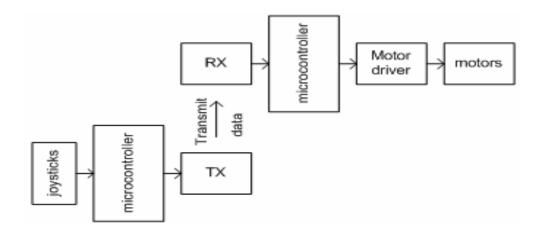

Figure 3.1: Basic block diagram of the project

Block diagram above shows that the joysticks will give command in analogue signal and then microcontroller will convert these analogue signal to digital signal and transmit these encoded value to the receiver. The receiver receives transmitted commands and decoded this value. The output signal then used to drive repetitive servo motor.

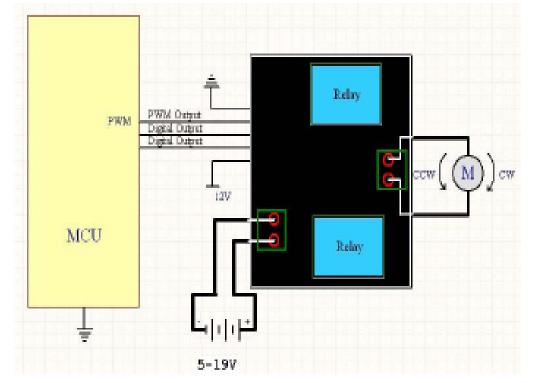

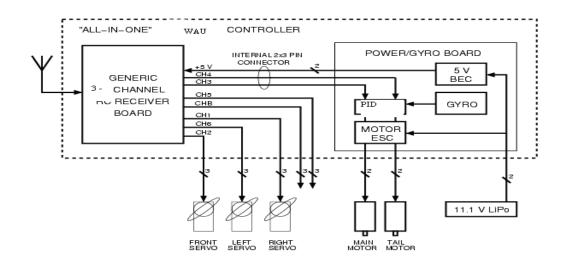

Figure 3.2: Contents of the integrated controller

The controller board must use PWM signals. Generating PCM signals would require more work, especially if proprietary encodings are used. The controller board also must expose the multiplexed PPM signal between the FM radio receiver and the demultiplexer, or at least the PWM inputs to the motor ESCs.

| Channel | Usage                                                     |  |

|---------|-----------------------------------------------------------|--|

| 1       | Right servo                                               |  |

| 2       | Front servo                                               |  |

| 3       | Main motor (internally connected to the power/gyro board) |  |

| 4       | Tail rotor (internally connected to the power/gyro board) |  |

| 5       | Unused                                                    |  |

| 6       | Left servo                                                |  |

#### 3.2.1 PIC Microcontroller

The PIC 16F877 8-bit microcontroller was chosen to obtain the analog data from the joysticks in transmitting section and control the motors on the Wau. This microcontroller has a 25 MHz processor, 33 input/output (I/O) pins, (8k\*14words) of Enhanced FLASH program memory, (386\*8bytes) of RAM, (256\*8bytes) of data EEPROM. The PIC does not have an operating system and simply runs the program in its memory when it is turned on. This PIC microcontroller has several hardware features that are very useful for use in a Wau and simplify the interfacing of sensors and motors with the microcontroller, such as an analog to digital converter (ADC), interrupts, timers, and capture/compare/pulse width modulation (CCP) channels. Figure 3.3 show the PIC16F877 pin configuration.

Figure 3.3: PIC16F877 Pin Configuration

### 3.2.2 Transmitter Receiver Modules

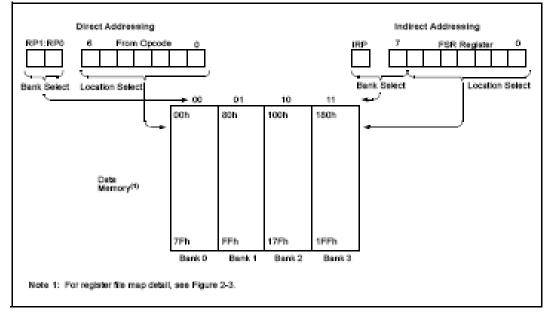

A pair of TWS/RWS 434 transmitter receiver module interfacing microcontroller is used to send and receive data between the ground station and quad-rotor. Two 433MHz whip style antennas are also used in the set up for long range detection. The TW-434 outputs up to 8mW at 433.92 MHz. It has an operating range of about 400 ft. outdoors, or about 200 ft. indoors. It can go through most walls. The operational voltage varies from 1.5 to 12 V and it accepts both linear and digital input. Figure 3.4 below shows the schematic of the transmitter with it is pin specifications.

Figure 3.4: RF Transmitter Schematic

The RWS-434 receiver also operates at 433.92 MHz with an operational voltage of around 4.5 - 5.5VDC. It sensitivity is 3  $\mu$ V, and it can have both linear and digital outputs. Figure 3.5 below shows the schematic of this receiver with the pin specifications.

Figure 3.5: RF Receiver Schematic

The modulation type for this module is Amplitude Modulation (AM). Amplitude Modulation is the process of changing the amplitude of a relatively high frequency carrier signal in proportion with the instantaneous value of the modulating signal. Amplitude Modulation is a relatively inexpensive, low quality form of modulation that is used for commercial broadcasting of both audio and video signals.

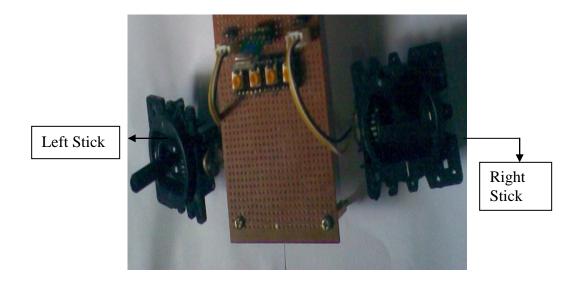

#### 3.2.3 Joysticks

In this project, only the two sticks are used on the remote control. The sticks that used are potentiometer joystick. The sticks will give command in analogue signal. The right stick is used to control the collective (up and down) by moving it up and down as well as the rudder (yaw left and yaw right) by moving it left and right. While the left stick controls the cyclic left and right by moving it left and right. Moving the right stick up and down actually controls two things which are the collective (pitch on the main blades) and the throttle. Depending on how fast the Wau is going and in which orientation it is flying, the controls behave differently.

Figure 3.6: Potentiometer Joysticks

## 3.2.4 Joystick Control Method

This section shows the control method of joystick. The control method included ascend, descend and steering.

## 3.2.4.1 Ascend

When the stick (throttle stick) was pulled up, the spinning speed of the main rotor blade is increase and the Wau begin to ascend.

#### 3.2.4.2 Descend

When the stick (throttle stick) was pulled down, the spinning speed of the main rotor blade is decrease and the Wau begin to descend.

#### 3.2.4.3 Steering

When the right stick (rudder stick) is moving to left, the head of the Wau turns to left. When the right stick (rudder stick) is moving to right, the head of the Wau turns to right.

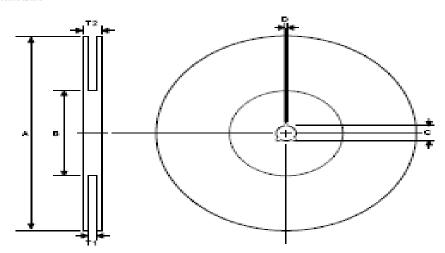

### 3.2.5 Antenna

An antenna is a metallic conductor system capable of radiating and capturing electromagnetic energy. The antenna is the medium to interface between two media to send and capture the signal. It is important in communication path. Antennas are also used to interface transmission lines to the atmosphere, the atmosphere to transmission lines, or both. In this project, both circuit used an antenna to transmit and receive the signal.

In essence, a transmission line couples energy from a transmitter to an antenna and an antenna to a receiver. At the transmit end of free space radio communication system, an antenna converts electrical energy traveling along a transmission line into electromagnetic waves that are emitted into space. At the receive end, an antenna converts electromagnetic waves space into electrical energy on a transmission line.

In this system, transmitter is connected to receiver through transmission line, antenna and free space. Electromagnetic waves are coupled from transmit to receive antenna through free space in a manner similar to the way energy is coupled from the primary to the secondary of a transformer.

A basic antenna is a passive reciprocal device. Transmit antenna must be capable of handling high power, therefore, it is constructed with material that can withstand high voltages and currents. Receive antenna produce very small voltages and currents and it is constructed from small diameter wire.

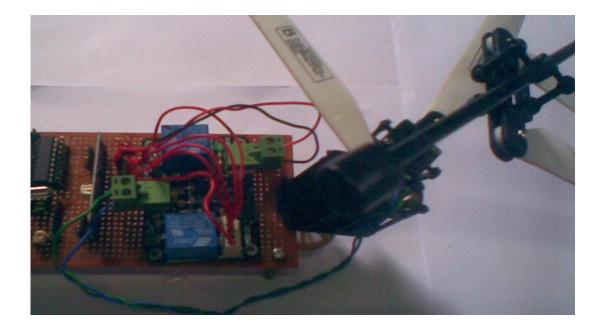

#### 3.2.6 Servo Motor

Servo motor is a system that consists of DC driver motor, rotor and blade. This kind of servo motor was chosen according to the torque means have high torque at all speed. A servo motor also must capable of holding static or no motion position. Besides, a servo motor also must be able to reverse direction quickly. Otherwise, a servo motor must be able to accelerate and decelerate to reach a position or rate of speed quickly. A servo motor as shown in Figure 3.7.

Figure 3.7: Servo motor circuit consist of DC driver circuit, rotor and blade

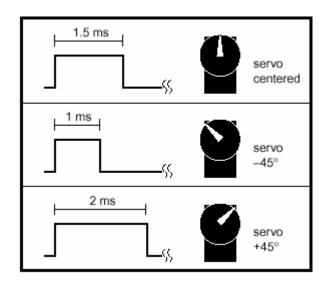

### 3.2.7 Servo Control

A brushed DC motor is a very simple device to control. Pulse-proportional servos are designed for use in radio-controlled (RC) cars, boats and planes. They provided precise control for steering, throttle, rudder, using a signal that is easy to transmit and receive. The motor speed (RPM) is directly proportional to the voltage applied across the terminals. The motor torque is directly proportional to the current flowing through the motor. Motor voltage can be easily controlled by using a PWM switch to chop the current to the motor proportionally to the desired throttle setting.

The processor is PIC16F877 with 8 channel PWM signal output. It can command 8 servos at the same time with RS-232 serial port. PWM signal is used extensively on DC servo control, such as the hobby model DC servo. The signal consists of pulses ranging from 1 to 2 milliseconds long, repeated 60 times a second.

The width of the square wave decides the horn of the servo oscillating angle, and the wave width is described according to the continuous time. When the width of the square wave equals 1.5 millisecond, the horn of the servo keeps on neutral position, 45degree angle. The width of square will change from 1 to 2 millisecond, and the horn of servo will rotate amount 0~90 degree angle. The servo positions its output shaft in proportion to the width of the pulse, as shown in Figure 3.8.

Figure 3.8: Servos are controlled by 1-2 ms pulses

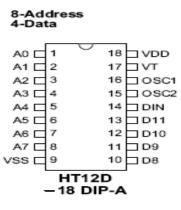

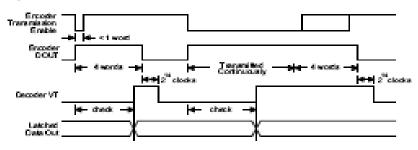

### 3.2.8 Encoder and Decoder

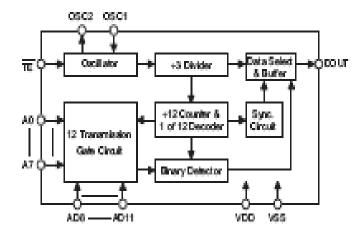

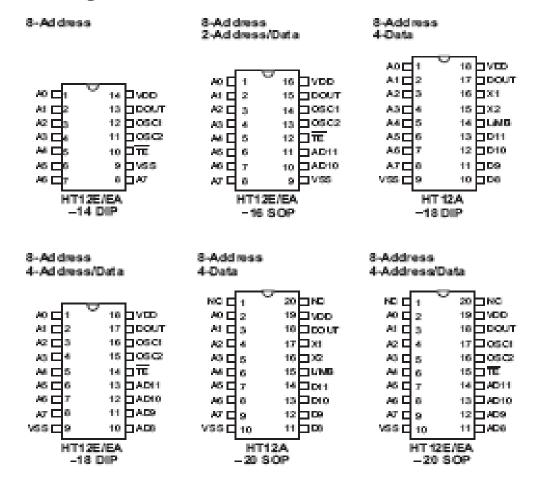

The  $2^{12}$  encoders are a series of CMOS LSIs for remote control system applications. They are capable of encoding information which consists of N address bits and 12\_N data bits. Each address or data input can be set to one of the two logic states. The programmed addresses or data are transmitted together with the header bits via an RF or an infrared transmission medium upon receipt of a trigger signal. The capability to select a TE trigger on the HT12E further enhances the application flexibility of the  $2^{12}$  series of encoders. Figure 3.9 show the HT12E pin configuration.

#### 8-Address

Figure 3.9: HT12E Pin Configuration

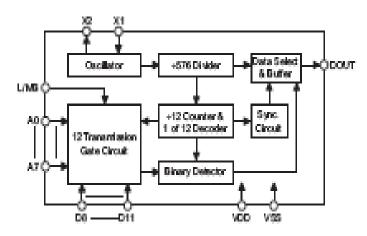

The  $2^{12}$  decoders are a series of CMOS LSIs for remote control system applications. They are paired with Holtek's  $2^{12}$  series of. For proper operation, a pair of encoder and decoder with the same number of addresses and data format should be chosen. The decoders receive serial addresses and data from a programmed  $2^{12}$  series of encoders that are transmitted by a carrier using an RF transmission medium. In this project, the HT12D is used and it is arranged to provide 8 address bits and 4 data bits. Figure 3.10 show the HT12D pin configuration.

Figure 3.10: HT12D Pin Configuration

## 3.3 Integration and Software System

This section describes a System Integration where to Interface to Hardware and Communication Protocols.

## **3.3.1** System Integration: Interface to Hardware

This section describes the C code that was written to interface the microcontroller with the hardware used in this project.

## 3.3.1.1 Joystick and A/D Converter

The 10 bit analog to digital converter on the PIC microcontroller was used to convert the signal representing the joystick movement to an integer value that could be used by the microcontroller.

## 3.3.1.2 PWM mode in CCP Channel

Since servo motor is controlled by means of managing PWM, the features of CCP (Capture/Compare/Pulse Width Modulation) play in important role.

## **3.3.2** Communication Protocols

The transmitter section uses a specific protocol to send commands to the vehicle over an RS-232 connection. The transmitter will send a constant of ASCII packet to the vehicle computer when the manual control is enabled. These packets consist of five pieces of information, separated by underscores. These pieces of information included manual control status, propeller speed, rudder angle, elevator angle, and a check sum.

Manual Control status is denoted by a 0 or a 1. The first element of the packet is 1 when the Manual Control is enabled. While when the Manual Control is disabled, a single packet of five zeroes is sent to the vehicle, and then the transmitter stops streaming data.

Propeller speed is sent to the vehicle as a signed value, between -300 and +300. This represents propeller speeds between -300 rotations per minute and +300 rotations per minute. Rudder angle and elevator angle are both sent to the vehicle as signed values, ranging from -4500 to +4500. These numbers represent hundredths of degrees, ranging between -45 degrees and positive 45 degrees. Positive rudder angles cause the vehicle to turn to port when moving forward. Positive elevator angles cause the elevator to go trailing edge low.

The last element of the packet is a checksum. The checksum is calculated by summing the status, the absolute value of propeller speed, the absolute value of rudder angle, and the absolute value of the elevator angle.

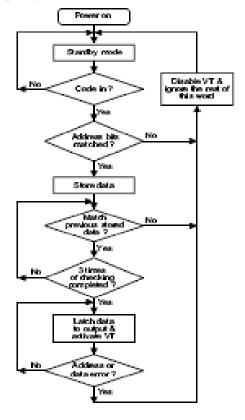

## 3.4 Software

This project used PIC microcontroller, so PIC C language code is written as a programming to control a transmitter and receiver. The joysticks will give the command and it is first task is calibrated while the microcontroller is powered up. Due to the fact that elevator and rudder angle, as well as propeller speed, are adjusted by moving the joysticks. Figure 3.11 and Figure 3.12 show the control algorithm for the transmitting and receiving data between the ground station and WAU. The first part of the program declares all of the variables needed throughout the program. The functions used to communicate between transmitter and receiver sections are also defined.

In transmitting section, at the start of the program set up AD conversion and process this conversion for the analog signals from each. This ADC values are encoded and send the command to the vehicle by the specific protocol.

Figure 3.11: Transmit Control Algorithm

In the receiver portion, at the beginning of the program set up PWM channel. Receiver receive the sending commands from transmitter and then decoded these data and decide which servo mounted on the control surface to be driven and output the PWM signal to responsible servo.

Figure 3.12: Receive Control Algorithm

## 3.5 Circuit Design of the System

This section shows how to design the circuit of the remote control of this system and the component list that was used in this project. Figure 3.13 and Figure 3.14 show the circuit diagram of the system. Figure 3.15 and Figure 3.16 show the circuit on PCB board.

## 3.5.1 Circuit Diagram

Figure 3.13: Circuit Diagram for Transmitter Section

Figure 3.14: Circuit Diagram for Receiver Section

## 3.5.2 Circuit on PCB Board

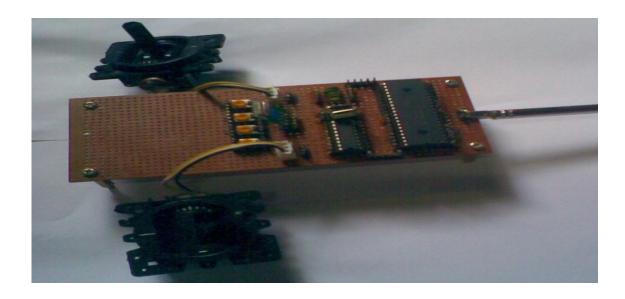

Figure 3.15: Transmitter Circuit on PCB board

Figure 3.16: Receiver Circuit on PCB board

## 3.5.3 List of components

In this section describe the components used in transmitter and receiver circuit.

| Component              | Description | Quantity |

|------------------------|-------------|----------|

| Potentiometer Joystick | -           | 2        |

| Microcontroller        | PIC16F877   | 1        |

| Capacitor              | 22pF        | 4        |

| Variable Resistor      | 10ΚΩ        | 4        |

| Encoder                | HT12E       | 1        |

| Antenna                | 433MHz      | 1        |

| RF Transmitter Module  | TWS434      | 1        |

| Crystal                | 4MHz        | 2        |

Table 3.2: List of component for Transmitter Circuit

| Component                 | Description | Quantity |

|---------------------------|-------------|----------|

| Microcontroller           | PIC16F877   | 1        |

| Capacitor                 | 22pF        | 2        |

| Decoder                   | HT12D       | 1        |

| Coil                      | -           | 1        |

| RF Receiver Module        | RWS434      | 1        |

| Crystal                   | 4MHz        | 1        |

| Motor with gear and blade | 12Watt      | 1        |

| DC Driver Circuit         | -           | 1        |

Table 3.3: List of component for Receiver Circuit

**CHAPTER 4**

DISCUSSION

## 4.1 Background

This section discussed about the result obtained and limitation of the project. All discussion is concentrating on the result and performance of the device.

## 4.2 Discussion

In this project, firstly the wireless connection between encoder and decoder must be able to ensure the data will transmit and receive clearly. It is difficult to get the connection and the correct formula and calculation must known. In programming, all the data and variable for transmitter and receiver was determined and in receiver the timer and PWM channel needed to set up clearly. Besides, the entire angles which are elevator angle and rudder angle must accurate to make the Wau fly without any problem.

Otherwise, the joystick is important component because it controls the commands that control the movement of Wau. The command from joystick is in analogue and microcontroller converted this command to digital signal. These digital signals then receive at receiver and microcontroller at this section convert it to original data to the servo motor. The used of RF Module in this project proved to be far superior in performance, cost and ease of use.

**CHAPTER 5**

## CONCLUSION

## 5.1 Background

This section discussed the conclusion of development of this project. This chapter also discusses the recommendation for this system for future development or implementation.

## 5.2 Conclusion

Overall, this project did not achieve the objective of the project and the result is not as expected. It is difficult to get the wireless connection between encoder and decoder. It is important to make connection between encoder and decoder because it will ensure a transmitter transmits the data and a receiver receive the data. Although this project not success but we got more knowledge and also applied the knowledge that we learned before especially in Communication System and make some an analysis between theorical and practical.

With a proper ways of conducting this project such as gaining all the knowledge as much as possible before doing the project or prepare all the things that need to be used so that it will not become the obstacle in the future will help us to conduct this project more effectively.

## 5.3 Recommendation

For future development, a more suitable an antenna and joysticks can help to improve this project. The value, formula and calculation to find the elevator angle, rudder angle, propeller speed acceleration, check sum, timer and counter and PWM period must be correct.

Besides, this project only has two channel where channel one is to make the Wau go up and down and channel two to make the Wau turn left and right, so we can added more channel such as a channel to make the Wau move forward and backward.

## REFERENCE

- Roy Blake. *Electronic Communication System*. Second Edition. United States of America: Delmar, Thomson Learning. 2001

- 2 Rusnani Ariffin, Kamariah Ismail, Mohd Tarmizi Ali and Norasimah Khadri. *Communication Engineering 1*. First Edition: University Technology Mara.

- Nurul Huda Abdul Ghani. Ac Motor Position Control Using PID Controller.

Bachelor Degree Project Thesis. University Malaysia Pahang; 2007

- 4 Double Horse Ltd.: *R/C Helicopter Using Instruction*: Trade broucher

APPENDICES

**Appendices A - DATA SHEET**

## PIC16F87XA Data Sheet

28/40/44-Pin Enhanced Flash Microcontrollers

© 2003 Microchip Technology Inc.

DS39582B

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are distonest and possibly llegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the periori doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warrantly is given and no liability is assumed by Microchip Technology incorporated with respect to the accuracy or use of such information, or infingement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Tradomarks

The Microchip name and logo, the Microchip logo, Accuron, dePIC, KesLoo, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of

Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Application Masstro, dsPICDEM, dsPICDEM.net, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB,

In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPUIB, MPLINK, MPSIM, PICKE, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

9 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

D6395828-page ii

© 2003 Microchip Technology Inc.

## 28/40/44-Pin Enhanced Flash Microcontrollers

### Devices included in this Data Sheet:

- PIC16F873A

PIC16F876A

- PIC16F874A

PIC16F877A

### High-Performance RISC CPU:

- Only 35 single-word instructions to learn

- All single-cycle instructions except for program branches, which are two-cycle

- Operating speed: DC 20 MHz clock input DC – 200 ns instruction cycle

- Up to SK x 14 words of Flash Program Memory, Up to 368 x 8 bytes of Data Memory (RAM), Up to 256 x 8 bytes of EEPROM Data Memory

- Plnout compatible to other 28-pin or 4D/44-pin PIC16CXXX and PIC16FXXX microcontrollers

### Peripheral Features:

- Timer0: 8-bit timer/counter with 8-bit prescaler.

- Timer1: 16-bit timer/counter with prescaler, can be incremented during Sleep via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Two Capture, Compare, PWM modules.

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max, resolution is 200 ns.

- PWM max, resolution is 10-bit

- Synchronous Serial Port (SSP) with SPI™ (Master mode) and I<sup>2</sup>C<sup>™</sup> (Master/Slave)

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI) with 9-bit address detection

- Parallel Slave Port (PSP) 8 bits wide with external RD, WR and CS controls (40/44-pin only)

- Brown-out detection circuitry for Brown-out Reset (BOR)

## Analog Features:

- 10-bit, up to 8-channel Analog-to-Digital Converter (AD)

- Brown-out Reset (BOR)

- Analog Comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VR0F) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs are externally accessible

### Special Microcontroller Features:

- 100,000 erase/write cycle Enhanced Flash program memory typical

- 1,000,000 erase/write cycle Data EEPROM memory typical

- Data EEPROM Retention > 40 years

- Self-reprogrammable under software control.

- In-Circuit Serial Programming<sup>\*\*</sup> (ICSP<sup>\*\*</sup>) via two pins

- Single-supply 5V In-Circuit Serial Programming

- Watchdog Timer (WOT) with its own on-chip RC oscillator for reliable operation

- Programmable code protection

- Power saving Sleep mode

- Selectable oscillator options

- In-Circuit Debug (ICD) via two pins

## CMOS Technology:

- Low-power, high-speed Flash/EEPROM technology

- Fully static design

- Wide operating voltage range (2.0V to 5.5V)

- Commercial and industrial temperature ranges

- Low-power consumption

|            | Prog  | ram Memory                   | Data | EEPROM  |    | 10-bit   | 10-ык сср  |      | 188P                       |           | Timera  |             |

|------------|-------|------------------------------|------|---------|----|----------|------------|------|----------------------------|-----------|---------|-------------|

| Device     | Bytes | #Single Word<br>Instructions |      | (Bytes) | νo | A/D (ch) | ATTRACTOR. | SPI  | Master<br>I <sup>2</sup> C | USART     | 0/16-5H | Comparators |

| PIC16F673A | 7.2K  | 4095                         | 192  | 128     | 22 | - 6      | 2          | Yea  | Yes                        | Yes       | 251     | 2           |

| PIC16F674A | 7.2K  | 4096                         | 192  | 128     | 33 | 8        | 2          | Yea  | Yes                        | Yes       | 27      | 2           |

| PIC16F676A | 14.3K | 8192                         | 388  | 255     | 22 | - 6      | 2          | Y08. | Y0:0                       | Yes       | 271     | 2           |

| PIC16F677A | 14.3K | 8192                         | 388  | 256     | 33 | 8        | 2          | 708  | Yes                        | 988<br>78 | 2       | 2           |

© 2003 Microchip Technology Inc.

D8395828-page 1

## 1.0 DEVICE OVERVIEW

This document contains device specific information about the following devices:

- PIC16F873A

- PIC16F874A

- PIC16F876A

- PIC16F877A

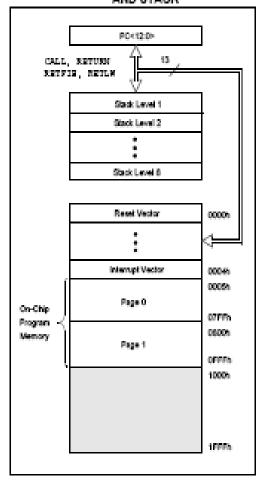

PIC16F873A/876A devices are available only in 28-pin packages, while PIC16F874A/877A devices are available in 40-pin and 44-pin packages. All devices in the PIC16F87XA family share common architecture with the following differences:

- The PIC16F873A and PIC16F874A have one-half of the total on-chip memory of the PIC16F876A and PIC16F877A

- The 28-pin devices have three I/O ports, while the 40/44-pin devices have five

- The 28-pin devices have fourteen interrupts, while the 40/44-pin devices have fifteen

- The 28-pin devices have five A/D input channels, while the 40/44-pin devices have eight

- The Parallel Slave Port is implemented only on the 40/44-pin devices

The available features are summarized in Table 1-1. Block diagrams of the PIC16F873A/876A and PIC16F874A/877A devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2 and Table 1-3.

Additional Information may be found in the PICmicro<sup>®</sup> Mid-Range Reference Manual (D\$33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

| Key Features                           | PIC16F873A                                              | PIC16F874A                                              | PIC16F876A                                              | PIC16F877A                                              |

|----------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Operating Frequency                    | DC - 20 MHz                                             |

| Resets (and Delays)                    | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 | POR, BOR<br>(PWRT, OST)                                 |

| Flash Program Memory<br>(14-bit words) | 4K                                                      | 4K                                                      | SK                                                      | 8K                                                      |

| Data Memory (bytes)                    | 192                                                     | 192                                                     | 368                                                     | 368                                                     |

| EEPROM Data Memory (bytes)             | 128                                                     | 128                                                     | 256                                                     | 256                                                     |

| Interrupts                             | 14                                                      | 15                                                      | 14                                                      | 15                                                      |

| I/O Parts                              | Ports A, B, C                                           | Ports A, B, C, D, E                                     | Ports A, B, C                                           | Ports A, B, C, D, E                                     |

| Timers                                 | 3                                                       | 3                                                       | 3                                                       | 3                                                       |

| Capture/Compare/FWM modules            | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Serial Communications                  | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             | MSSP, USART                                             |

| Parallel Communications                | —                                                       | PSP                                                     |                                                         | PSP                                                     |

| 10-bit Analog-to-Digital Module        | 5 Input channels                                        | 8 input channels                                        | 5 Input channels                                        | 8 Input channels                                        |

| Analog Comparators                     | 2                                                       | 2                                                       | 2                                                       | 2                                                       |

| Instruction Set                        | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         | 35 Instructions                                         |

| Packages                               | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN | 28-pin PDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN | 40-pin PDIP<br>44-pin PLCC<br>44-pin TQFP<br>44-pin QFN |

## TABLE 1-1: PIC16F87XA DEVICE FEATURES

© 2003 Microchip Technology Inc.

D8395828-page 5

| OSC1/CLKI<br>OSC1                                       | 9  | 6  |            |                        |                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------|----|----|------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI                                                    |    | 2  | ı<br>I     | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input. ST<br>buffer when configured in RC mode; otherwise CMOS.<br>External clock source input. Always associated with pin<br>function OSCI (see OSCI ICLK). OSCIACLKO close. |

| 09C2/CLKO<br>09C2<br>CLKO                               | 10 | 7  | 0          | -                      | Ciscillator crystal or clock output.<br>Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or resonato<br>in Crystal Oscillator mode.<br>In RC mode. OSC2 pin outputs CLKO, which has 1/4 the                                               |

| CENO                                                    |    |    | 9          |                        | frequency of OSC1 and denotes the instruction cycle rab                                                                                                                                                                                                                        |

| MCLRAPP                                                 | 1  | 28 | I          | 8T                     | Master Clear (input) or programming voltage (output).<br>Master Clear (Reset) input. This pin is an active low Reset<br>to the device.                                                                                                                                         |

| VPP                                                     |    |    | - P        |                        | Programming voltage input.                                                                                                                                                                                                                                                     |

| RAD/ANO<br>EAD                                          | 2  | 27 | 100        | TTL                    | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                             |

| AND                                                     |    |    | 1          |                        | Analog input 0.                                                                                                                                                                                                                                                                |

| RA1/AN1<br>RA1<br>AN1                                   | 3  | 28 | ю          | TTL                    | Digital IXO.<br>Anako insut 1.                                                                                                                                                                                                                                                 |

| RA2/AN2/VREF-/<br>CVREF<br>RA2<br>AN2<br>VREF-<br>CVREF | 4  | 1  | <u>0</u> 0 | TTL                    | Digital IXO.<br>Analog input 2.<br>A/D reference voltage (Low) input.<br>Comparator ViceF output.                                                                                                                                                                              |

| RASVANSVIREF+<br>RAS<br>ANS<br>VREF+                    | 5  | 2  | 10         | TTL                    | Digital IXO.<br>Analog input 3.<br>A/D reference voltage (High) input.                                                                                                                                                                                                         |

| RA4/TOCKI/C1OUT<br>RA4<br>T0CK0<br>C1OUT                | 6  | 3  | 10<br>- 0  | ST                     | Digital I/O – Open-drain when configured as output.<br>Timer0 external clock input.<br>Comparator 1 output.                                                                                                                                                                    |

| RA5AN4/65/C2OUT<br>RA5<br>AN4<br>S5<br>C2OUT            | 7  | 4  | 10 0       | TTL                    | Digital IKO.<br>Analog input 4.<br>SPI slave select input.<br>Comparator 2 output.                                                                                                                                                                                             |

#### TABLE 1-21 PIC16E873A/876A PINOUT DESCRIPTION

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

#### TABLE 1-31 DIC105874A/877A DINOUT DESCRIPTION

| TABLE 1-3: PIC      | :16F8;       |              |              | IOUT L      | DESCR        |                       |                                                                   |

|---------------------|--------------|--------------|--------------|-------------|--------------|-----------------------|-------------------------------------------------------------------|

| Pin Name            | PDIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | QFN<br>Pin₽ | ИО/Р<br>Туре | Buffer<br>Type        | Description                                                       |

| OSC WOLKI           | 13           | 14           | 30           | 32          |              | ST/CMOS <sup>H)</sup> |                                                                   |

| OSC1                |              |              |              |             | 1            |                       | Oscillator crystal input or external clock source                 |

|                     |              |              |              |             |              |                       | input. ST buffer when configured in RC mode;                      |

| CLKI                |              |              |              |             |              |                       | otherwise CMOS.<br>External clock source input. Always associated |

| GUNI                |              |              |              |             | 1            |                       | with pin function OSC1 (see OSC1/CLK).                            |

|                     |              |              |              |             |              |                       | OSC2/CLKO pira).                                                  |

| OSC2/CLKO           | 14           | 15           | 34           | 33          |              |                       | Oscilator crystal or clock output.                                |

| 0802                |              | 14           |              |             | 0            |                       | Oscillator crystal output.                                        |

| Serverie:           |              |              |              |             |              |                       | Connects to crystal or resonator in Crystal                       |

|                     |              |              |              |             |              |                       | Oscillator mode.                                                  |

| CLKO                |              |              |              |             | 0            |                       | In RC mode, OSC2 pin outputs CLKO, which                          |

|                     |              |              |              |             |              |                       | has 1/4 the frequency of OSC1 and denotes the                     |

|                     |              |              |              |             |              |                       | instruction cycle rate.                                           |

| MCLR/VPP            | ÷            | 2            | 18           | 8           |              | ST                    | Master Clear (input) or programming voltage (output).             |

| MOLR                |              |              |              |             | -            |                       | Master Clear (Reset) input. This pin is an active                 |

| N dawn              |              |              |              |             |              |                       | low Reset to the device.                                          |

| VPP                 |              |              |              |             |              |                       | Programming voltage input.                                        |

|                     |              |              |              |             |              |                       | PORTA is a bidirectional I/O port.                                |

| RADIAND             | 2            | 3            | 19           | 12          |              | TTL                   |                                                                   |

| RAO                 |              |              |              |             | NO .         |                       | Digital I/O.                                                      |

| ANO                 |              |              |              |             | 1            |                       | Analog input 0.                                                   |

| RA1/AN1             | 3            | 4            | 20           | 20          |              | TTL                   |                                                                   |

| RA1                 |              |              |              |             | NO .         |                       | Digital VO.                                                       |

| AN1                 |              |              |              |             | -            |                       | Analog input 1.                                                   |

| RA2/AN2/VREF-/CVREF | 4            | 5            | 21           | 21          |              | TTL                   |                                                                   |

| RA2                 |              |              |              |             | 10           |                       | Digital I/O.<br>Analog insut 2.                                   |

| AN2<br>Vector       |              |              |              |             |              |                       | Analog input 2.<br>A/D reference voltage (Low) input              |

| CVREF               |              |              |              |             | - ô -        |                       | Comparator VREF output.                                           |

| RA332N3A/pere       | 6            |              | 22           | 22          | ·            | TT                    | companies and only only a                                         |

| RA3                 | 0            | 6            | 22           | 22          | NO.          | 110                   | Distal I/O.                                                       |

| AN3                 |              |              |              |             | 100          |                       | Analog input 3.                                                   |

| VREP+               |              |              |              |             | i            |                       | A/D reference voltage (High) input.                               |

| RANTICKISCIOLIT     | 8            | 7            | 23           | 23          |              | ST                    |                                                                   |

| RA4                 | 1991         | •            |              |             | LIO .        | <u>е</u> т            | Digital I/O - Open-drain when configured as                       |

|                     |              |              |              |             |              |                       | output.                                                           |

| TOCINI              |              |              |              |             | 1            |                       | Timer0 external clock input.                                      |

| CIOUT               |              |              |              |             | 0            |                       | Comparator 1 output                                               |

| RA5/AN4/SS/C2OUT    | 7            | 8            | 24           | 24          |              | TTL                   |                                                                   |

| RA5                 |              |              |              |             | - NO         |                       | Digital VO.                                                       |

| AN4                 |              |              |              |             | 1            |                       | Analog input 4.                                                   |

| 88                  |              |              |              |             | 1            |                       | SPI slave select input.                                           |

| C2OUT               |              |              |              |             | 0            |                       | Comparator 2 output                                               |

| Legend: I = input   |              | - outpu      |              |             | npu%out      |                       | ) = power                                                         |

| - = Not us          | 60 T         | IL - TIL     | Incast.      | - 数正 三条     | Schmitt 1    | rioper input          |                                                                   |

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmit Trigger input when configured as the external interrupt. 2: This buffer is a Schmit Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

© 2008 Microchip Technology Inc.

| Pin Name | PDIP<br>Pin# | PLCC<br>Pin# | TQFP<br>Pin# | QFN<br>Pinë | VO/P<br>Type | Buffer<br>Type        | Description                                        |

|----------|--------------|--------------|--------------|-------------|--------------|-----------------------|----------------------------------------------------|

|          |              |              |              |             |              |                       | PORTB is a bidirectional I/O port. PORTB can be    |

|          |              |              |              |             |              |                       | software programmed for internal weak pull-up on a |

|          |              |              |              |             |              |                       | inputs.                                            |

| RBOINT   | 33           | 36           | 8            | 9           |              | TTL/ST <sup>(1)</sup> |                                                    |

| RB0      |              |              |              |             | 1/0          |                       | Digital I/O.                                       |

| INT      |              |              |              |             | I            |                       | External interrupt.                                |

| RB1      | 34           | 37           | 9            | 10          | NO.          | TTL                   | Digital I/O.                                       |

| R82      | 35           | 38           | 10           | 11          | NO.          | TTL                   | Digital I/O.                                       |

| RB3/PGM  | 38           | 39           | 11           | 12          |              | TTL                   |                                                    |

| R83      |              |              |              |             | NO.          |                       | Digital I/O.                                       |

| POM      |              |              |              |             | I            |                       | Low-voltage ICSP programming enable pin.           |

| R84      | 37           | 41           | 14           | - 14        | NO.          | TIL                   | Digital I/O.                                       |

| R85      | 38           | 42           | 15           | 15          | NO.          | TTL                   | Digital I/O.                                       |

| RBMPGC   | 39           | 43           | 16           | 16          |              | TTL/8T <sup>(2)</sup> |                                                    |

| RE6      |              |              |              |             | NO.          |                       | Digital I/O.                                       |

| POC      |              |              |              |             | I            |                       | In-circuit debugger and ICSP programming clock     |

| R67/PGD  | 40           | 44           | 17           | 17          |              | TTL/8T <sup>(2)</sup> |                                                    |

| RB7      |              |              |              |             | NO.          |                       | Digital I/O.                                       |

| POD      |              |              |              |             | 1/0          |                       | In-circuit debugger and ICSP programming data      |

## TABLE 1-3: PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED)

- = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Pin Name                                 | PDIP<br>Pin# | PLCC<br>Pin# | TOFP<br>Pin# | QFN<br>Pin# | UO/P<br>Type | Buffer<br>Type | Description                                                                               |

|------------------------------------------|--------------|--------------|--------------|-------------|--------------|----------------|-------------------------------------------------------------------------------------------|

|                                          |              |              |              |             | .,,,,,,,     | .,,,,,         | PORTC is a bidirectional I/O part.                                                        |

| RCO/T1080/T1CKI<br>RCO<br>T1080<br>T1CKI | 15           | 16           | 32           | 34          | 00-          | ST             | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external clock input.                 |

| RC1/T105/0CP2<br>RC1<br>T1051<br>CCP2    | 18           | 18           | 35           | 35          | 2 - 2        | 87             | Digital I/O.<br>Timer1 oscillator input.<br>Capture2 input, Compare2 output, PWM2 output. |

| RC2/CCP1<br>RC2<br>CCP1                  | 17           | 19           | 36           | 38          | 20           | ST             | Digital I/O.<br>Capture1 input, Compare1 output, IPWM1 output                             |

| RC3/SCK/SCL<br>RC3<br>SCK                | 18           | 20           | 37           | 37          | 22           | 8T             | Digital I/O.<br>Synchronous serial clock input/output for SIPI mode.                      |

| SCL                                      |              |              |              |             | 10           |                | Synchronous serial clock inpubliculput for I <sup>2</sup> C mode.                         |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA         | 23           | 25           | 42           | 42          | 2 - 2        | 87             | Digital IKO.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                |

| RC5/SDO<br>RC5<br>SDO                    | 24           | 28           | 43           | 43          | 0            | 87             | Digital I/O.<br>SPI data cut.                                                             |

| ROB/TX/CK<br>ROS<br>TX<br>CK             | 25           | 27           | 44           | 44          | 2 o 2        | ST             | Digital I/O.<br>USART asynchronous transmit.<br>USART1 synchronous clock.                 |

| RC7/RX/DT<br>RC7<br>RX<br>DT             | 28           | 29           | 1            | 1           | 2 - 2        | ST             | Digital I/O.<br>USART asynchronous receive.<br>USART synchronous data.                    |

#### PIC16F874A/877A PINOUT DESCRIPTION (CONTINUED) TABLE 1-3:

Note 1: This buller is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmit Trigger input when used in Serial Programming mode.

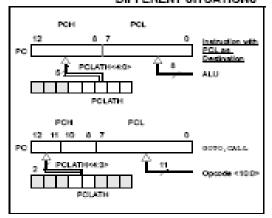

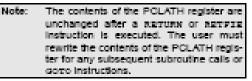

This buffer is a Schmit Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.