# UNIVERSITI MALAYSIA PAHANG

| BORANG PE                                                                                    | NGESAHAN STATUS TESIS*                                                                                                                                     |  |  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| JUDUL: MODELING AND SIN                                                                      | JUDUL: MODELING AND SIMULATION OF SINGLE PHASE INVERTER                                                                                                    |  |  |

| WITH PWM USING M                                                                             | IATLAB/SIMULINK                                                                                                                                            |  |  |

| SESI F                                                                                       | PENGAJIAN: 2007/2008                                                                                                                                       |  |  |

| Saya MOHAMMAD A                                                                              | RIFF BIN YAAKOB ( 851015-01-6693 )<br>(HURUF BESAR)                                                                                                        |  |  |

| mengaku membenarkan tesis (Sarj<br>Perpustakaan dengan syarat-syarat                         | jana Muda/ <del>Sarjana</del> / <del>Doktor Falsafah</del> )* ini disimpan di<br>t kegunaan seperti berikut:                                               |  |  |

|                                                                                              | siti Malaysia Pahang (UMP).<br>nbuat salinan untuk tujuan pengajian sahaja.<br>nbuat salinan tesis ini sebagai bahan pertukaran antara institusi           |  |  |

| SULIT                                                                                        | (Mengandungi maklumat yang berdarjah keselamatan<br>atau kepentingan Malaysia seperti yang termaktub<br>di dalam AKTA RAHSIA RASMI 1972)                   |  |  |

| TERHAD                                                                                       | (Mengandungi maklumat TERHAD yang telah ditentukan oleh organisasi/badan di mana penyelidikan dijalankan)                                                  |  |  |

| √ TIDAK TERH                                                                                 | AD                                                                                                                                                         |  |  |

|                                                                                              | Disahkan oleh:                                                                                                                                             |  |  |

| (TANDATANGAN PENULIS)                                                                        | (TAPPATINGAN PENYELIA)                                                                                                                                     |  |  |

| Alamat Tetap:                                                                                |                                                                                                                                                            |  |  |

| <u>NO 30, JLN PANGSUN4 27/12I<br/>TAMAN BUNGA NEGARA,<br/>40400 SHAH ALAM,<br/>SELANGOR.</u> | D, MUHAMAD ZAHIM BIN SUJOD<br>( Nama Penyelia )                                                                                                            |  |  |

| Tarikh: <u>26 NOVEMBER 2007</u>                                                              | Tarikh: : <u>26 NOVEMBER 2007</u>                                                                                                                          |  |  |

| berkuasa/organi                                                                              | ak berkenaan.<br>LIT atau TERHAD, sila lampirkan surat daripada pihak<br>sasi berkenaan dengan menyatakan sekali tempoh tesis ini perh<br>gai atau TERHAD. |  |  |

Tesis dimaksudkan sebagai tesis bagi Ijazah doktor Falsafah dan Sarjana secara Penyelidikan, atau disertasi bagi pengajian secara kerja kursus dan penyelidikan, atau Laporan Projek Sarjana Muda (PSM). "I hereby acknowledge that the scope and quality of this thesis is qualified for the award of the Bachelor Degree of Electrical Engineering (Power System)"

Signature Name Date : <u>Jud H</u> : <u>MUHAMAD ZAHIM BIN SUJOD</u> : <u>22 NOVEMBER 2007</u>

# DEVELOPMENT OF SINGLE PHASE PWM INVERTER FOR UPS APPLICATION

# MOHAMMAD ARIFF BIN YAAKOB

This thesis is submitted as partial fulfillment of the requirement for the award of the Bachelor Degree Electrical Engineering (Power System)

> Faculty of Electrical & Electronic Engineering Universiti Malaysia Pahang

> > NOVEMBER, 2007

# DECLARATION

I declare that this thesis entitled "Development of Single Phase PWM Inverter for Ups Application" is the result of my own research except as cited in the references. The thesis has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

Signature Author Date : MOHAMMAD ARIFF BIN YAAKOB : NOVEMBER 2007 Specially dedicated to My beloved parent

# ACKNOWLEDGEMENT

Alhamdulillah, the highest thank to God because with His Willingness I possible to complete the final year project. In preparing this thesis, I was in contact with many people, researchers, academicians, and practitioners. They have contributed towards my understanding and thoughts. In particular, I wish to express my sincere appreciation to my main thesis supervisor, Mr. Mohd Zahim Bin Sujod, for encouragement, guidance, critics and friendship. I am also very thankful to Mr. Fadhil Bin Abas for sharing his valuables ideas as well as his knowledge. Without their continued support and interest, this thesis would not have been the same as presented here.

My fellow postgraduate students should also be recognized for their support. My sincere appreciation also extends to all my colleagues and others who have provided assistance at various occasions. Their views and tips are useful indeed. Unfortunately, it is not possible to list all of them in this limited space. I am grateful to all my family members.

# ABSTRACT

This project is to develop an inverter circuit for Uninterruptable Power Supply (UPS) application. Inverters are circuit that convert DC to AC. The function of inverter is to create an AC voltage by using a DC voltage source and in UPS system, the voltage source that used DC voltage commonly batteries. Pulse-width modulation (PWM) technique is use in this project because with PWM, the amplitude of the output voltage can be controlled with the modulating waveforms. In this project, Metal Oxide Field Effect Transistor (MOSFET) is used as switch in the full bridge inverter circuit design. For alternated control purpose, sequential switching is designed for PWM get-way through the MOSFET driver. The function of the driver is to control the ON/OFF of the MOSFET. Driver of the MOSFET is essential in the inverter circuit because the driver use to interface between control circuits (low voltage) and inverter circuit (high voltage). The objective of this project is to develop single phase PWM Inverter for UPS application and to design the circuit, simulate and analyze the switching characteristic of single phase PWM inverter. The simulation of full-bridge single phase inverter for this project has been done by using Unipolar scheme and the output waveform is successfully generated. The switching process in hardware is control by PIC 16F877a and the MOSFET driver is using IR2110. At the end of this project, the results from simulation were compared with hardware.

## ABSTRAK

Projek ini adalah mengenai pembangunan litar penyongsang untuk aplikasi Bekalan kuasa tidak terganggu (UPS). Penyongsang adalah litar yang mengubah DC ke AC. Fungsi penyongsang adalah untuk menghasilkan voltan AC dengan menggunakan voltan DC dan dalam sistem UPS, sumber voltan DC yang digunakan biasanya bateri. Teknik pemodulatan lebar denyut (PWM) digunakan dalam projek ini kerana dengan PWM, amplitud voltan keluaran boleh dikawal. Dalam projek ini, Metal Oxide Field Effect Transistor (MOSFET) digunakan sebagai suis di dalam litar penyongsang. Untuk tujuan kawalan yang berulang, pensuisan berkala direkabentuk sebagai penghubung kepada pemandu MOSFET. Fungsi pemandu adalah untuk mengawal "ON/OFF" MOSFET. Pemandu MOSFET adalah penting dalam litar penyongsang kerana ianya digunakan sebagai penghubung antara litar kawalan (voltan rendah) dan litar penyongsang (voltan tinggi). Objektif projek ini adalah untuk merekabentuk litar, mesimulasi dan menganalisis ciri-ciri pengsuisan penyongsang fasa tunggal. Simulasi penyongsang fasa tunggal dijalankan dengan menggunakan skim unipolar. Proses pensuisan didalam perkakas dikawal dengan menggunakan PIC 16F877 dan pemandu MOSFET yang digunakan ialah IR2110. Pada pengakhir projek ini, keputusan daripada simulasi dibanding dengan keputusan perkakas.

# TABLE OF CONTENTS

| CHAPTER | CONTENTS              | PAGE |

|---------|-----------------------|------|

|         | TITLE                 | i    |

|         | DECLARATION           | ii   |

|         | DEDICATION            | iii  |

|         | ACKNOWLEDGEMENT       | iv   |

|         | ABSTRACT              | V    |

|         | ABSTRAK               | vi   |

|         | TABLE OF CONTENTS     | vii  |

|         | LIST OF TABLE         | xi   |

|         | LIST OF FIGURE        | xii  |

|         | LIST OF ABBREVIATIONS | xiv  |

|         | LIST OF APPENDIX      | XV   |

# 1 INTRODUCTION

| 1.1 | Background                   | 1 |

|-----|------------------------------|---|

| 1.2 | Overview of Inverter Project | 1 |

| 1.3 | Objective                    | 2 |

| 1.5 | Scope of Project             | 2 |

# 2 LITERATURE REVIEW

3

| 2.1      | Uninterruptable Power Supply (UPS) |                                              | 3  |

|----------|------------------------------------|----------------------------------------------|----|

| 2.2      | Microcontroller (PIC 16F877)       |                                              | 5  |

| 2.3 HV F |                                    | loating MOS-Gate Driver IC                   |    |

|          | 2.3.1                              | Gate Drive Requirements of High-Side Devices | 8  |

|          | 2.3.2                              | Low-Side Channel                             | 9  |

|          | 2.3.3                              | High-side Channel                            | 10 |

|          | 2.3.4                              | How to Select the Bootstrap Components       | 11 |

|          | 2.3.5                              | How to Deal With Negative Transients         |    |

|          |                                    | on the V <sub>s</sub> Pin                    | 13 |

|          | 2.3.6                              | Minimize the Parasitics                      | 14 |

|          | 2.3.7                              | Reduce Control IC Exposure                   | 15 |

|          | 2.3.8                              | Improve Local Decoupling                     | 15 |

| 2.4      | Invert                             | er                                           | 16 |

|          | 2.4.1                              | Power Inverter                               | 16 |

|          | 2.4.2                              | Inverter Applications                        | 17 |

|          | 2.4.3                              | Types of Inverter                            | 17 |

|          | 2.4.4                              | Basic Half-Bridge Inverter Circuit           |    |

|          |                                    | Resistive Load                               | 18 |

|          | 2.4.5                              | Inductive-Resistive Load                     | 19 |

1

# METHODOLOGY

3

| 3.1 | Background            |                                                   | 23 |

|-----|-----------------------|---------------------------------------------------|----|

| 3.2 | Overall System Design |                                                   | 25 |

| 3.3 | Hardw                 | Hardware Design                                   |    |

|     | 3.3.1                 | Power Supply Design                               | 27 |

|     | 3.3.2                 | Controller Design                                 | 28 |

|     | 3.3.3                 | Driver Design                                     | 30 |

|     |                       | 3.3.3.1 Calculating the Bootstrap Capacitor Value | 31 |

|     |                       | 3.3.3.2 Selecting the Bootstrap Diode             | 33 |

|     |                       | 3.3.3.3 IR2110 Circuit Layout Considerations      | 34 |

|     | 3.4.4                 | Inverter Design                                   | 34 |

|     |                       | 3.4.4.1 Low-Pass Filter                           | 36 |

# 4 **RESULT AND ANALYSIS**

4.1 Introduction 38 Power Supply Circuit Output Voltages 4.2 39 4.3 Microcontroller Output Pulses 40 MOSFET Driver Output Pulses 4.4 42 Analysis of Inverter Output 44 4.5 4.5.1 Analysis of Voltage, Current, and Power Relation with Load 44 4.5.2 Analysis of Total Harmonic Distortion (THD) 46 4.5.3 Hardware Output 49

21

23

38

| CON  | ICLUSION                      | 51 |

|------|-------------------------------|----|

| 5.1  | Conclusion                    | 51 |

| 5.2  | Recommendation                | 52 |

| 5.3  | Costing and Commercialization | 52 |

|      | 5.3.1 Costing                 | 52 |

|      | 5.3.2 Commercialization       | 54 |

| REF  | ERENCE                        | 55 |

| APPI | ENDIX A                       | 56 |

| APPI | ENDIX B                       | 60 |

| APPI | ENDIX C                       | 65 |

|      |                               | 68 |

| APPENDIX D | 68 |

|------------|----|

| APPENDIX E | 80 |

# LIST OF TABLES

| TABLE NO. | TITLE                                          | PAGE |  |

|-----------|------------------------------------------------|------|--|

| 4.1       | Supply output versus design constrain          | 39   |  |

| 4.2       | Comparisons between designs constrain and      |      |  |

|           | Microcontroller output                         | 41   |  |

| 4.3       | IR2110 MOSFET driver output                    | 43   |  |

| 4.4       | Voltage, current and power value based on the  |      |  |

|           | load resistance                                | 46   |  |

| 4.5       | Inverters configuration                        | 48   |  |

| 4.6       | Modified square wave inverter data from        |      |  |

|           | frequency spectrum                             | 48   |  |

| 4.7       | Modified square wave inverter with filter data |      |  |

|           | from frequency spectrum                        | 49   |  |

| 5.1       | The cost of component                          | 53   |  |

# LIST OF FIGURES

| FIGURE N | IO. TITLE                                                        | PAGE |

|----------|------------------------------------------------------------------|------|

| 2.1      | Small UPS                                                        | 3    |

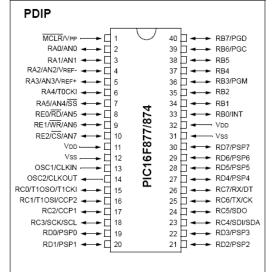

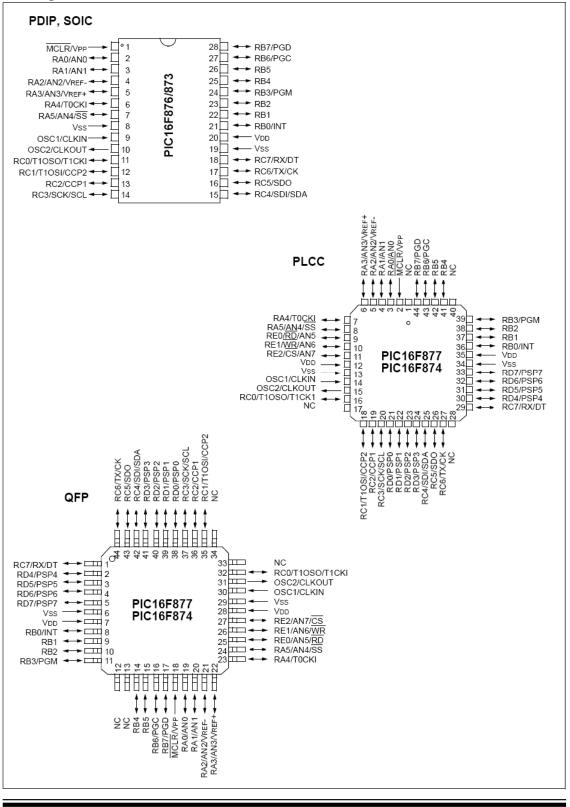

| 2.2      | PIC16F8777A                                                      | 5    |

| 2.3      | PIC SCHEMATIC                                                    | 6    |

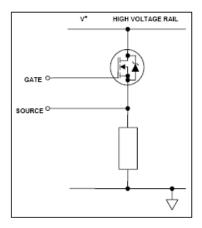

| 2.4      | Power MOSFET in the High-Side Configuration                      | 9    |

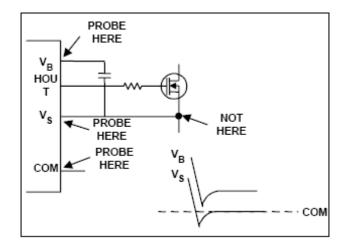

| 2.5      | Considering the $V_S$ Spike during the Reverse Recovery          | 14   |

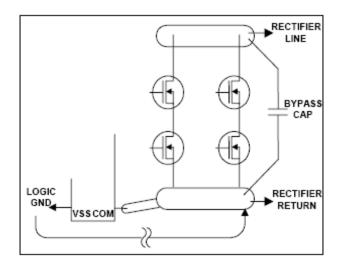

| 2.6      | Ground Connections and Layout                                    | 15   |

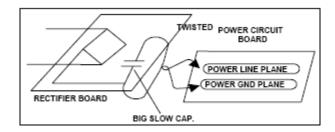

| 2.7      | Power Bypass Capacitor                                           | 16   |

| 2.8      | (a) Half-bridge Inverter under resistive load                    |      |

|          | (b) Switching and output voltage waveform                        | 19   |

| 2.9      | (a) Half-bridge inverter with inductive resistive load           |      |

|          | (b) Equivalent circuit                                           |      |

|          | (c) Steady state waveforms                                       | 20   |

| 2.10     | SPWM and Inverter Output Voltage                                 | 22   |

| 3.1      | System design of Inverter system                                 | 24   |

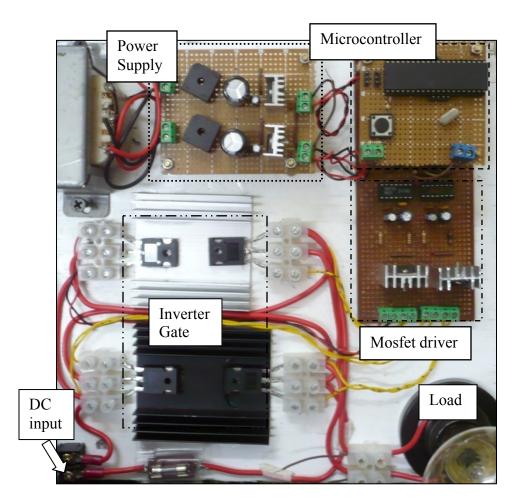

| 3.2      | The full picture of hardware                                     | 26   |

| 3.3      | Power Supply circuit                                             | 27   |

| 3.4      | Picture of power supply designed                                 | 27   |

| 3.5      | Microcontroller circuit                                          | 28   |

| 3.6      | Picture of controller designed                                   | 28   |

| 3.7      | Desired output pulses                                            | 29   |

| 3.8      | IR2110 MOSFET driver circuit                                     | 30   |

| 3.9      | Bootstrap diode/capacitor circuit used with IR 2110 control IC's | 31   |

| 3.10     | Recommended layout of the Bootstrap Components                   | 34   |

| 3.11 | Full-bridge inverter                                            | 35 |

|------|-----------------------------------------------------------------|----|

| 3.12 | L-C low-pass filter schematic                                   | 37 |

| 4.1  | Power supply output voltage (a) output1 (b) output2             | 39 |

| 4.2  | Output pulses at pin 16 and pin 17                              | 40 |

| 4.3  | Simulation output pulses at both pin by using ISIS              | 40 |

| 4.4  | Program used to generated pulses                                | 41 |

| 4.5  | Ho pin output pulses of both drivers                            | 42 |

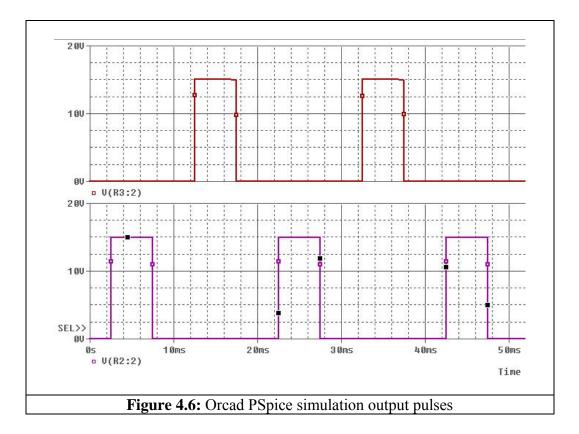

| 4.6  | Orcad PSpice simulation output pulses                           | 43 |

| 4.7  | The output voltage of different load                            | 44 |

| 4.8  | The output current with different load                          | 45 |

| 4.9  | The output power with different load                            | 45 |

| 4.10 | Frequency spectrum of modified square wave inverter             |    |

|      | (without filter)                                                | 47 |

| 4.11 | Frequency spectrum of modified square wave inverter with filter | 47 |

| 4.12 | Inverter output waveform from oscilloscope                      | 49 |

| 4.13 | Hardware output result                                          | 50 |

# LIST OF ABBREVIATION

| DC     | - | Direct Current                      |

|--------|---|-------------------------------------|

| AC     | - | Alternate Current                   |

| PWM    | - | Pulse Width Modulation              |

| SPWM   | - | Sinusoidal Pulse Width Modulation   |

| IGBT   | - | Insulated Gate Bipolar Transistor   |

| MOSFET | - | Metal Oxide Field Effect Transistor |

| UPS    | - | Uninterruptable Power Supply        |

| PIC    | - | Programmable Intelligent Computer   |

|        |   |                                     |

# LIST OF APPENDICES

| APPENDIX | PPENDIX TITLE        |    |

|----------|----------------------|----|

| А        | IRFP 450 Datasheet   | 56 |

| В        | IR2110 Datasheet     | 60 |

| С        | BYV29-500 Datasheet  | 65 |

| D        | PIC 16F877 Datasheet | 68 |

| Е        | SPWM program         | 80 |

# **CHAPTER 1**

#### **INTRODUCTION**

## 1.1 Background

This chapter explains briefly about Inverter and its operation. This chapter also explains the overview of project objectives, scopes and thesis outline.

## **1.2** Overview of Inverter Project

Inverters are circuits that convert DC to AC. More precisely, inverters transfer power from a DC source to an AC load. The function of inverter is to create an AC voltage by using a DC voltage source and in UPS system, the voltage source that used DC voltage commonly batteries. Inverters are used in applications such as adjustablespeed AC motor drives, uninterruptable power supplies (UPS), and AC appliances run from an automobile battery.

In this report, a design for a power inverter circuit is presented for conversion of energy from DC battery to AC power to be used mainly for Uninterruptable Power Supply (UPS) applications. The configuration is achieved using a full-bridge PWM inverter. DC-DC converter circuit not been constructed in this project and DC supply from High voltage DC supply been used.

In this project, PIC microcontroller used to control the output by using sinusoidal pulse width modulation technique based on open loop configuration system. The proposed practical circuit operates from a 340V DC input and outputs a regulated 240V AC, 50Hz voltage. A complete circuit analysis, design and cost evaluation is presented and supported by PSPICE simulation results.

## 1.3 Objective

The objective of this project is to develop single phase PWM Inverter for UPS application. In this part, the development of PWM Inverter circuit is the main task of this project to convert DC power from battery to AC. These projects also develop an open-loop control system by using PIC microcontroller to control output voltage. The other objectives of this project are to design the circuit, simulate and analyze the switching characteristic of single phase PWM inverter.

#### **1.4** Scope of the Project

The main scopes of this project are;

- i. Design PWM Inverter circuit that generates 240V<sub>RMS</sub>, 50Hz and 500W of power.

- Microcontroller used as a controller to control switching process. The type of PIC used is PIC16F877.

- ORCAD PSpice and Multisim PSpice program are used to simulate and design the circuit.

## **CHAPTER 2**

## THEORY AND LITERATURE REVIEW

# 2.1 Uninterruptible Power Supply (UPS)

Figure 2.1: Small UPS

An uninterruptible power supply (UPS), uninterruptible power source or sometimes called a battery backup is a device which maintains a continuous supply of electric power to connected equipment by supplying power from a separate source when utility power is not available [1]. A UPS is inserted between the source of power (typically commercial utility power) and the load it is protecting. When a power failure or abnormality occurs, the UPS will effectively switch from utility power to its own power source almost instantaneously [1].

While not limited to any particular type of equipment, a UPS is typically used to protect computers, telecommunication equipment or other electrical equipment where an unexpected power disruption could cause injuries, fatalities, serious business disruption or data loss. UPS units come in sizes ranging from units which will back up a single computer without monitor (around 200 VA) to units which will power entire data centers or buildings (several megawatts). Larger UPS units typically work in conjunction with generators [1].

Historically, UPS were very expensive and were most likely to be used on expensive computer systems and in areas where the power supply is interrupted frequently. However, UPS units are now more affordable, and have become an essential piece of equipment for data centers and business computers, but are also used for personal computers, entertainment systems and more [1].

In certain countries, where the electrical grid is under strain, providers struggle to ensure supply during times of peak demand (such as summer, during which air-conditioning usage increases). In order to prevent blackouts, electrical utilities will sometimes use a process called rolling blackouts or load shedding, which involves cutting the power to large groups of customers for short periods of time. Several major blackouts occurred in 2003, most notably the 2003 North America blackout in the north-eastern US and eastern Canada and the 2003 Italy blackout, both of which affected over 50 million people, and brought attention to the need for UPS power backup units [1].

A UPS is not to be confused with a standby generator, which does not provide protection from a momentary power interruption and may result in an interruption when it is switched into service, whether manually or automatically. However, such generators are typically placed before the UPS to provide cover for lengthy outages [1].

## 2.2 Microcontroller (PIC 16F877A).

**PIC** is a family of Harvard architecture microcontrollers made by Microchip Technology, derived from the PIC1650 originally developed by General Instrument's Microelectronics Division. The name PIC was originally an acronym for "**Programmable Intelligent Computer**".

Figure 2.2: PIC16F8777A

In this project, a microcontroller; PIC16F877a (Figure 2.2) is use to control the output. The reason for use microcontroller is the PIC architecture is distinctively minimalist. It is characterized by the following features:

- separate code and data spaces

- a small number of fixed length instructions

- most instructions are single cycle execution (4 clock cycles), with single delay cycles upon branches and skips

- a single accumulator (W), the use of which (as source operand) is implied

- All RAM locations function as registers as both source and/or destination of math and other functions.

- data space mapped CPU, port, and peripheral registers

- the program counter is also mapped into the data space and writable (this is used to synthesize indirect jumps)

- 10-bit multi-channel Analog-to-Digital converter

- has 33 input or output ports (see Figure 2.3)

Figure 2.3: PIC Schematic

Unlike most other CPUs, there is no distinction between "memory" and "register" space because the ram serves the job of both memory and registers, and the ram is usually just referred to as the register file or simply as the registers.

PIC microcontroller have a very small set of instructions (only 35 instruction), leading some to consider them as RISC devices, however many salient features of RISC CPU's are not reflected in the PIC architecture. For example:

- it does not have load-store architecture, as memory is directly referenced in arithmetic and logic operations

- it has a singleton working register, whereas most modern architectures have significantly more

PIC have a set of register files that function as general purpose RAM, special purpose control registers for on-chip hardware resources are also mapped into the data space. The addressability of memory varies depending on device series, and all PIC devices have some banking mechanism to extend the addressing to additional memory. Later series of devices feature move instructions which can cover the whole addressable space, independent of the selected bank. In earlier devices (ie. the baseline and mid-range cores), any register move had to be through the accumulator.

To synthesize indirect addressing, a "file select register" (FSR) and "indirect register" (INDF) are used: A read or write to INDF will be to the memory pointed to by FSR. Later devices extended this concept with post and pre increment/decrement for greater efficiency in accessing sequentially stored data. This also allows FSR to be treated like a stack pointer.

All PICs feature Harvard architecture, so the code space and the data space are separate. PIC code space is generally implemented as EPROM, ROM, or FLASH ROM. In general, external code memory is not directly addressable due to the lack of an external memory interface.

The PIC architecture has no (or very meager) hardware support for saving processor state when servicing interrupts. The 18 series improved this situation by implementing shadow registers which save several important registers during an interrupt. The PIC architecture may be criticized on a few important points.

• The few instructions, limited addressing modes, code obfuscations due to the "skip" instruction and accumulator register passing makes it difficult to program in assembly language, and resulting code difficult to comprehend. This drawback has been alleviated by the increasing availability of high level language compilers.

• Data stored in program memory is space inefficient and/or time consuming to access, as it is not directly addressable.

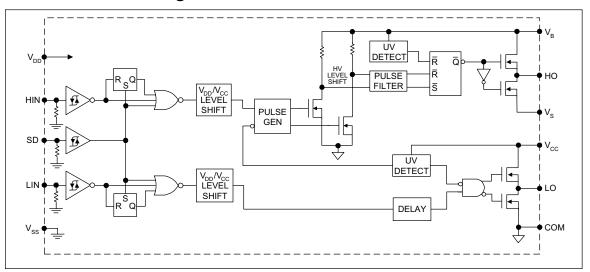

#### 2.3 HV Floating MOS-Gate Driver IC

## 2.3.1 Gate Drive Requirements of High-Side Devices

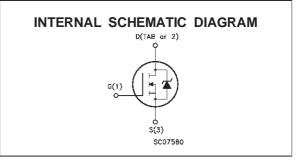

The gate drive requirements for a power MOSFET or IGBT utilized as a high-side switch (the drain is connected to the high voltage rail, as shown in Figure 2.4) driven in full enhancement (i.e., lowest voltage drop across its terminals) can be summarized as follows:

- Gate voltage must be 10 V to 15 V higher than the drain voltage. Being a high-side switch, such gate voltage would have to be higher than the rail voltage, which is frequently the highest voltage available in the system.

- The gate voltage must be controllable from the logic, which is normally referenced to ground. Thus, the control signals have to be level-shifted to the source of the high-side power device, which, in most applications, swings between the two rails.

- 3. The power absorbed by the gate drive circuitry should not significantly affect the overall efficiency.

Figure 2.4: Power MOSFET in the High-Side Configuration

With these constraints in mind, several techniques are presently used to perform this function. Each basic circuit can be implemented in a wide variety of configurations [2].

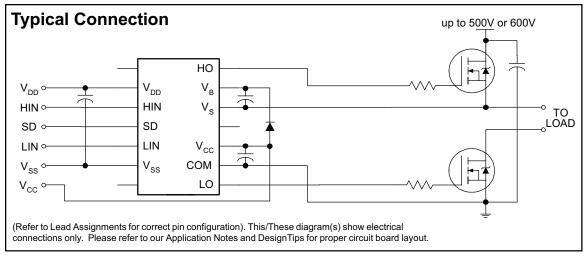

International Rectifier's family of MOS-gate drivers (MGDs) integrate most of the functions required to drive one high-side and one low-side power MOSFET or IGBT in a compact, high performance package. With the addition of few components, they provide very fast switching speeds and low power dissipation. They can operate on the bootstrap principle or with a floating power supply. Used in the bootstrap mode, they can operate in most applications from frequencies in the tens of Hz up to hundreds of kHz [2].

### 2.3.2 Low-Side Channel

The driver's output stage is implemented either with two n-channel MOSFETs in the totem pole configuration (source follower as a current source and common source for current sinking), or with an n-channel and a p-channel CMOS inverter stage. Each MOSFET can sink or source gate currents from 0.12 A to 4 A, depending on the MGD. The source of the lower driver is independently brought out to the COM pin so that a direct connection can be made to the source of the power device for the return of the gate drive current. An under voltage lockout prevents either channel from operating if  $V_{CC}$  is below the specified value (typically 8.6/8.2 V) [2].

Any pulse that is present at the input pin for the low-side channel when the UV lockout is released turns on the power transistor from the moment the UV lockout is released. This behavior is different from that of the high-side channel [2].

#### 2.3.3 High-Side Channel

This channel has been built into an "isolation tub" capable of floating from 500 V or 1200 V to -5 V with respect to power ground (COM). The tub "floats" at the potential of  $V_{S.}$  Typically this pin is connected to the source of the high-side device, as shown in Figure 2 and swings with it between the two rails [2].

If an isolated supply is connected between  $V_B$  and  $V_S$ , the high-side channel will switch the output (HO) between the positive of this supply and its ground in accordance with the input command [2].

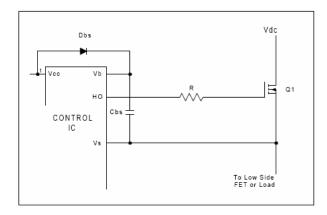

One significant feature of MOS-gated transistors is their capacitive input characteristic (i.e., the fact that they are turned on by supplying a charge to the gate rather than a continuous current). If the high-side channel is driving one such device, the isolated supply can be replaced by a bootstrap capacitor ( $C_{BOOT}$ ) [2].

The gate charge for the high-side MOSFET is provided by the bootstrap capacitor which is charged by the 15 V supply through the bootstrap diode during the

time when the device is off (assuming that  $V_S$  swings to ground during that time, as it does in most applications). Since the capacitor is charged from a low voltage source the power consumed to drive the gate is small. The input commands for the high-side channel have to be level-shifted from the level of COM to whatever potential the tub is floating at which can be as high as 1200 V. As shown in Figure 2 the on/off commands are transmitted in the form of narrow pulses at the rising and falling edges of the input command. They are latched by a set/reset flip-flop referenced to the floating potential [2].

The use of pulses greatly reduces the power dissipation associated with the level translation. The pulse discriminator filters the set/reset pulses from fast dv/dt transients appearing on the V<sub>S</sub> node so that switching rates as high as 50 V/ns in the power devices will not adversely affect the operation of the MGD. This channel has its own under voltage lockout (on some MGDs) which blocks the gate drive if the voltage between V<sub>B</sub> and V<sub>S</sub> (i.e., the voltage across the upper totem pole) is below its limits. The operation of the UV lockout differs from the one on V<sub>CC</sub> in one detail: the first pulse *after* the UV lockout has released the channel changes the state of the output. The high voltage level translator circuit is designed to function properly even when the V<sub>S</sub> node swings below the COM pin by a voltage indicated in the datasheet (typically 5 V). This occurs due to the forward recovery of the lower power diode or to the LdI/dt induced voltage transient [2].

#### **2.3.4** How to Select the Bootstrap Components

The bootstrap diode and capacitor are the only external components strictly required for operation in a standard PWM application. Local decoupling capacitors on the  $V_{CC}$  (and digital) supply are useful in practice to compensate for the inductance of the supply lines [3].

The voltage seen by the bootstrap capacitor is the  $V_{CC}$  supply only. Its capacitance is determined by the following constraints:

1. Gate voltage required to enhance MGT

- 2. I<sub>QBS</sub> quiescent current for the high-side driver circuitry

- 3. Currents within the level shifter of the control IC

- 4. MGT gate-source forward leakage current

- 5. Bootstrap capacitor leakage current

Factor 5 is only relevant if the bootstrap capacitor is an electrolytic capacitor, and can be ignored if other types of capacitor are used. Therefore it is always better to use a non-electrolytic capacitor if possible [3].

The minimum bootstrap capacitor value can be calculated from the following equation:

$$C \ge \frac{2\left[2Q_{g} + \frac{I_{gbs(max)}}{f} + Q_{ls} + \frac{I_{Cbs(leak)}}{f}\right]}{V_{cs} - V_{f} - V_{LS} - V_{min}}$$

(2.1)

Where:

$Q_g$  = Gate charge of high-side FET

f = frequency of operation

$I_{Cbs (leak)}$  = bootstrap capacitor leakage current

$I_{qbs (max)} = Maximum VBS$  quiescent current

$V_{CC}$  = Logic section voltage source

$V_{\rm f}$  = Forward voltage drop across the bootstrap diode

$V_{LS}$  = Voltage drop across the low-side FET or load

$V_{Min}$  = Minimum voltage between VB and VS.

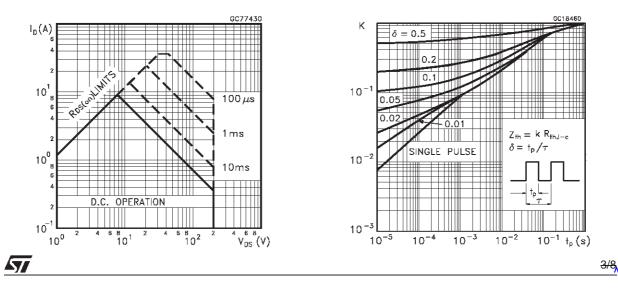

Q<sub>ls</sub> = level shift charge required per cycle (typically 5 nC for 500 V/600 V MGDs and 20 nC for 1200 V MGDs) The bootstrap diode must be able to block the full voltage, this occurs when the top device is on and is about equal to the voltage across the power rail. The current rating of the diode is the product of gate charge times switching frequency. For an IRF450 HEXFET power MOSFET operating at 100 kHz it is approximately 12 mA [3].

The high temperature reverse leakage characteristic of this diode can be an important parameter in those applications where the capacitor has to hold the charge for a prolonged period of time. For the same reason it is important that this diode have an ultra-fast recovery to reduce the amount of charge that is fed back from the bootstrap capacitor into the supply [3].

### 2.3.5 How to Deal With Negative Transients on the V<sub>s</sub> Pin

Of the problems caused by parasitics, one of the main issues for control ICs is a tendency for the  $V_S$  node to undershoot the ground following switching events. Conversely, overshoot does not generally present a problem due to the high differential voltage capability of International Rectifier's proven HVIC process [2].

International Rectifier's control ICs are guaranteed to be completely immune to  $V_S$  undershoot of at least 5 V, measured with respect to COM. If undershoot exceeds this level, the high-side output will temporarily latch in its current state. Provided  $V_S$  remains within absolute maximum limits the IC will not suffer damage, however the high-side output buffer will not respond to input transitions while undershoot persists beyond 5 V. This mode should be noted but proves trivial in most applications, as the high-side is not usually required to change state immediately following a switching event [2].

The signals listed below should be observed both in normal operation and during high-stress events such as short circuit or over-current shutdown, when di/dt is highest. Readings should always be taken directly across IC pins as shown in Figure 2.5, so that contributions from the parasitics in the drive coupling are included in the measurement [2].

- (1) High-side offset with respect to common; V<sub>S</sub>-COM

- (2) The floating supply;  $V_B V_S$

The following guidelines represent good practice in control IC circuits and warrant attention regardless of the observed latch-up safety margin [2].

Figure 2.5: Considering the V<sub>S</sub> Spike during the Reverse Recovery

## 2.3.6 Minimize the Parasitics

- 1) Use thick, direct tracks between switches with no loops or deviation.

- 2) Avoid interconnect links. These can add significant inductance.

- 3) Reduce the effect of lead-inductance by lowering package height above the PCB.

- 4) Consider co-locating both power switches to reduce track lengths.

#### 2.3.7 Reduce Control IC Exposure

- 1) Connect  $V_s$  and COM as shown in Figure 2.6.

- 2) Minimize parasitics in the gate drive circuit by using short, direct tracks.

- 3) Locate the control IC as close as possible to the power switches.

Figure 2.6: Ground Connections and Layout

## 2.3.8 Improve Local Decoupling

- 1) Increase the bootstrap capacitor ( $C_B$ ) value to above 0.47  $\mu$ F using at least one low-ESR capacitor. This will reduce overcharging from severe V<sub>S</sub> undershoot.

- 2) Use a second low-ESR capacitor from  $V_{CC}$  to COM. As this capacitor supports both the low-side output buffer and bootstrap recharge, we recommend a value at least ten times higher than  $C_B$ .

- 3) Connect decoupling capacitors directly across the appropriate pins as shown in Figure 2.7.

- 4) If a resistor is needed in series with the bootstrap diode, verify that  $V_B$  does not

fall below COM, especially during start-up and extremes of frequency and duty cycle.

Figure 2.7: Power Bypass Capacitor

Granted proper application of the above guidelines, the effects of  $V_S$  undershoot will be minimized at source. If the level of undershoot is still considered too high, then some reduction of dv/dt may be necessary [2].

External snubbing and/or increasing gate drive resistance may be used to trade efficiency for lower switching rate. If the system will not tolerate this, then fast anti-parallel clamping diodes may be considered appropriate. HEXFRED diodes are ideal for this purpose [2].

#### 2.4 Inverter

#### 2.4.1 **Power Inverter**

A power inverter is a device that converts DC (Direct Current) power into AC (Alternating Current) power. The AC output is usually 120 VAC, 60 Hz (USA domestic power) or 230 VAC, 50 Hz (International power). Aircraft applications often require 115 VAC, 400 Hz. Nova Electric offers all three of these common output voltages, in both single and three-phase configurations, as well as other special / custom outputs [4].

#### 2.4.2 Inverter Applications

With a large enough battery bank, or a large enough alternator output from a vehicle, almost anything within reason can be operated from a power inverter – this assumes that the inverter has the proper power output for the given load. Everyday appliances such as microwaves, power tools, TVs and VCRs, lights, audio/visual equipment, battery chargers and computers are common loads. An inverter sized for loads with heavy inrush current can be used to power air compressors, water pumps, heaters, ventilation fans, and air conditioners. Nova Electric's Pure Sine Wave inverters are ideal for running sensitive test equipment such as communications equipment, oscilloscopes, scales, high end stereos & video equipment, communications equipment, etc [4].

## 2.4.3 Types of Inverter

**Square Wave:** Square Wave units could be harmful to some electronic equipment, especially equipment with transformers or motors. The square wave output has a high harmonic content which can lead such equipment components to overheat Square Wave units were the pioneers of inverter development and, like the horse and buggy, are no longer relevant for modern use [4].

**Modified Square Wave:** The most common, general-use inverters available are "Modified Sine Wave". Usually available at more moderate pricing compared to pure sine wave models. Modified Square Wave (or "Modified Sine Wave" and "Quasi Sine Wave") output inverters are designed to have somewhat better characteristics than Square Wave units, while still being relatively inexpensive. Although designed emulate a Pure Sine Wave output, Modified Square Wave inverters do not offer the same perfect electrical output. As such, a negative by-product of Modified output units is electrical

noise, which can prevent these inverters from properly powering certain loads. For example, many TVs and stereos use power supplies incapable of eliminating common mode noise. As a result, powering such equipment with a Modified Square Wave may cause a "grain" or small amount of "snow" on your video picture, or "hum" on your sound system. Likewise, most appliances with timing devices, light dimmers, battery chargers, and variable speed devices may not work well, or indeed, may not work at all [4].

**Pure Sine Wave:** Pure or True Sine Wave inverters provide electrical power similar to the utility power you receive from the outlets in your home or office, which is highly reliable and does not produce electrical noise interference associated with the other types of inverters. With its "perfect" sine wave output, the power produced by the inverter fully assures that your sensitive loads will be correctly powered, with no interference. Some appliances which are likely to require Pure Sine Wave include computers, digital clocks, battery chargers, light dimmers, variable speed motors, and audio/visual equipment. If your application is an important video presentation at work, opera on your expensive sound system, surveillance video, a telecommunications application, any calibrated measuring equipment, or any other sensitive load, you must use a Pure Sine Wave inverter [4].

## 2.4.4 Basic Half-Bridge Inverter Circuit Resistive Load

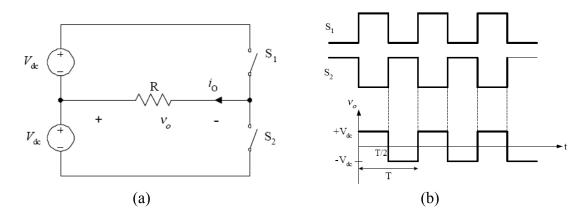

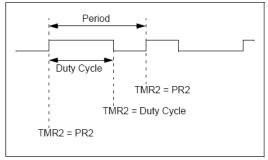

To illustrate the basic concept of a DC-to-AC inverter circuit we consider a halfbridge voltage-source inverter circuit under resistive load as shown in Fig. 2.8 (a). Its switching waveforms for S1, S2 and the result output voltage are shown in Fig. 2.8 (b).

**Figure 2.8:** (a) Half-bridge Inverter under resistive load (b) Switching and output voltage waveform

The circuit operation is very simple since S1 and S2 are switched on and off alternatively at 50% duty cycle as shown in the switching waveform in Fig. 2.8 (b). This shows that the circuit generates a square ac voltage waveform across the load from a constant dc source. The voltages,  $V_{DC}$  and  $-V_{DC}$  are across R when S1 ON while S2 OFF and when S2 is ON while S1 is OFF, respectively. One observation to be made here is that the frequency of the output voltage is equal to f = 1/T and is determined by the switching frequency. This is true as long as S1 and S2 are switched complementarily. Moreover, the *rms* value of the output voltage is simply  $V_{DC}$ . Hence, to control the *rms* value of the output voltage we must control the rectified  $V_{DC}$  voltage source. Another observation is that the load power factor is unity since we have purely resistive load. That is rarely encountered in practical application.

Finally, we should note that in practice the above circuit does not require two equal dc voltage sources as shown in Fig. 2.8 (a). Instead, large splitting capacitors are used to produce two equal DC voltage sources [5].

The two capacitors are equal and very large so that RC is much larger than the half-switching period. This will guarantee that the mid-point, a, between the capacitors has a fixed potential at one-half of the supply voltage  $V_{DC}$  [5].

#### 2.4.5 Inductive-Resistive Load

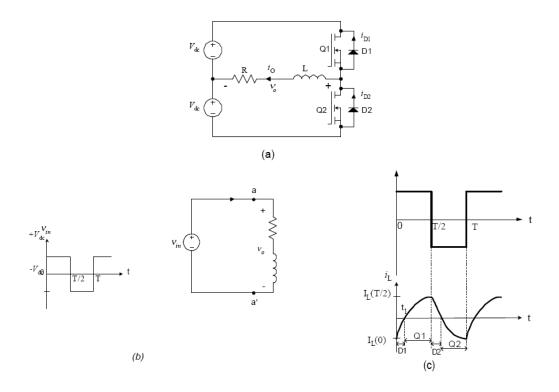

Figure 2.9 (a) shows a half-bridge inverter under inductive resistive load with the equivalent circuit and the output waveforms shown in Fig. 2.9 (b) and (c), respectively.

**Figure 2.9** (a) Half-bridge inverter with inductive resistive load (b) Equivalent circuit and (c) Steady state waveforms.

With Q1 and Q2 switched complementary each at 50% duty cycle with switching frequency f, then the load between terminal a and  $a\phi$  is excited by square voltage waveform v(t) in of amplitudes +V dc and -V dc as shown in Fig. 2.9 (b), i.e. v(t) in is defined as follows:

$$v_{in}(t) = \begin{cases} +V_{dc} & 0 \le t < T/2 \\ -V_{dc} & T/2 \le t < T \end{cases}$$

(2.2)

The switches are implemented by using conventional SCR (that require external forced commutation circuit) or fully controlled power switching devices such as IGBTs,

GTOs, BTJs or MOSFETs. Notice from the load current  $i_L$  direction, these switches must be bi-directional. Assume the inverter operates in steady state and its inductor current waveform is shown in Fig. 2.9(c) for  $1 \ 0 < t < t$ , the inductor current is negative which means while Q1 is ON the current actually flows in the reverse direction, i.e. in the body diode of the bi-directional switch Q1. At  $1 \ t = t$ , the current flows through the transistor Q1 as shown. At t = T 2, when S2 is turned ON, since the current direction is positive, the flyback diode, D2, turns ON until  $1 \ t = T 2 + t$  when Q2 starts conducting [5].

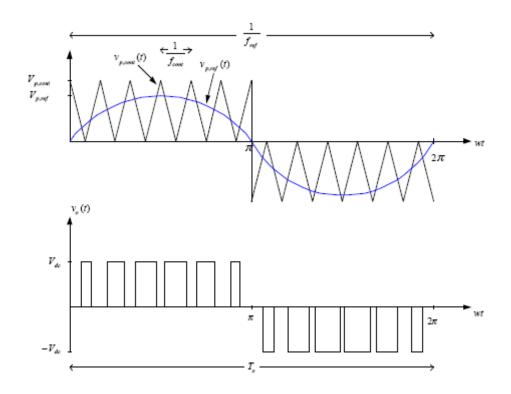

#### 2.4.6 Sinusoidal PWM Waveforms

In Sinusoidal Pulse Width Modulation, SPWM, multiple pulses are generated, each having different width time. The width of each pulse is varied in proportion to the instantaneous integrated value of the required fundamental component at the time of its event. In other words, the pulse width becomes a sinusoidal function of the angular position. The repetition frequency of the output voltage will be a frequency higher than the fundamental. In applying SPWM, the lower order harmonics of the modulated voltage wave are highly reduced in contrast to the use of uniform pulse width modulation [5].

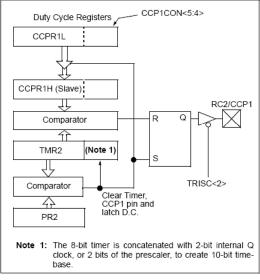

In SPWM the output voltage signal can be obtained by comparing a control signal, *cont* v, against a sinusoidal reference signal, *ref* v, at the desired frequency as shown in Fig 2.10. At the first half of the output period, output voltage takes a positive value (+ dc V), whenever the reference signal is greater than the control signal. At the same way, at the second half of the output period, the output voltage takes a negative value (- dc V) whenever the reference signal is less than the control signal [5].

The control frequency *cont* f determines the number of pulses per half of cycle for the output voltage signal. Also, the output frequency  $O_f$  is determined by the reference frequency *ref f*. The modulation index Ma is defined as the ratio between the sinusoidal magnitude and the control signal magnitude [5].

To obtain a vary train of pulses, each pulse has to vary proportional to the necessary fundamental component precisely at the time when this pulse occurs. The frequency of the output waveform needs to be higher than the frequency of the fundamental component. By varying the width of each pulse, the inverter is able to produce different levels of output voltage for the corresponding pulse event [5].

Figure 2.10: SPWM and Inverter Output Voltage.

### CHAPTER 3

#### METHODOLOGY

# 3.1 Background

This chapter explains about hardware design for the inverter including PIC microcontroller circuit, H-bridge Inverter circuit and MOSFET driver circuit. This chapter also explains the calculation involve in designing the hardware.

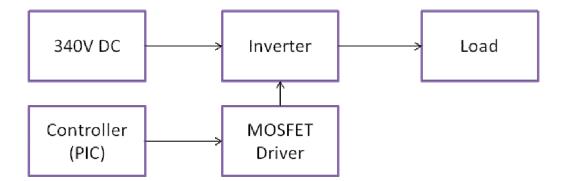

Before looking at the detail of all the methods below, it is best to begin with brief review the correlation of all methods. The Figure 3.1 below show the correlation of all methods in this project.

Figure 3.1: System design of Inverter system

#### **3.2** Overall System Design

#### **Design Specifications**

| : | 340 V <sub>DC</sub>            |

|---|--------------------------------|

| : | Single-phase $240V_{AC}$ RMS   |

| : | $50\text{Hz} \pm 0.1\text{Hz}$ |

| : | >500Watts                      |

| : | > 90%                          |

| : | 50 Hz, 25% Duty cycle          |

| : | PIC 16F877                     |

|   | :<br>:<br>:<br>:<br>:          |

There are 4 main circuit in this inverter design, the first is the supply, second is the microcontroller, third is the MOSFET driver and the forth is the inverter. For the supply circuit, 240Vrms AC voltage is step down, rectify and regulate to get 15V and 5V DC.

The second circuit is microcontroller circuit. The PIC 16F877 is used to generate PWM pulses. For this system design, PWM technique is used to control the switching pulses that used to drive MOSFET.

The third circuit for this inverter design consist MOSFET driver, a driver that used to drive MOSFET. Based on MOSFET datasheet, the minimum voltage used to fully turn on MOSFET is 10V. So, the microcontroller cannot connect directly to the MOSFET because it only produces 5V output and it doesn't have electrical isolation between the upper control pulses and the upper gate of the full-bridge inverter circuit.

The forth circuit design is an inverter circuit. Inverter is a circuit that convert DC source to AC source. For this design, the method used to generate AC is using Full-

bridge inverter configuration. The DC source used is a 340V and the output waveform produce the switching scheme is a modified square wave.

# 3.3 Hardware Design

The hardware design is divided into 4 parts. The power supply design, PIC microcontroller design, MOSFET driver design and Inverter design.

Figure 3.2: The full picture of hardware

### 3.3.1 Power Supply Design

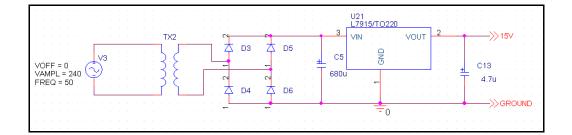

Figure 3.3: Power supply circuit

The power supply is developed by using full bridge rectifier and regulator to convert AC power supply to DC. This power supply is used as a replacement of battery that been used as a supply in UPS. This supply produces two voltages at the output, one is 5V and the other is 15V. The voltage is step down by power transformer from 240Vrms socket supply to 20Vrms and 12Vrms. The step down AC voltage been rectified by bridge rectifier and then voltage regulator LM7805 and LM7815 been used to regulate and stabilize the voltage at the output of the power supply. The 5V voltage is used to supply control circuit that contain PIC microcontroller and the 15V voltage is used to supply MOSFET driver circuit. The figure of power supply circuit is shown in Figure 3.3. Figure 3.4 is the power supply designed.

Figure 3.4: Picture of power supply designed

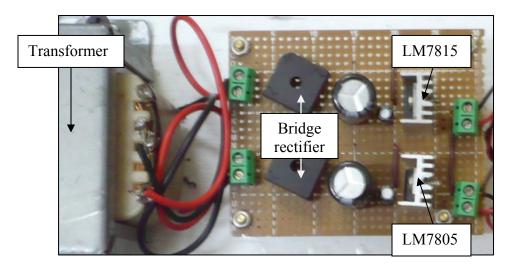

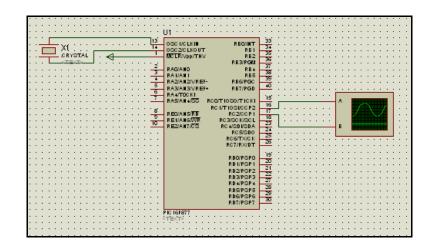

Figure 3.5: Microcontroller circuit

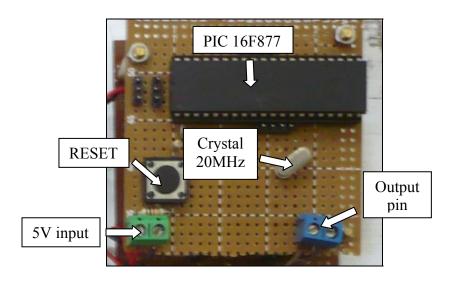

The microcontroller that used in designing the switching controller is 16F877 and the crystal used is 20MHz. This PIC is chosen because it can generate high switching pulses and easy to get in the market. The high frequency crystal is used so it can support high switching pulses that can be used in further improvement of the inverter. The output pin used in this design is pin 16 and pin 17. Figure 3.6 below is the picture of controller designed.

Figure 3.6: Picture of controller designed

The programming used to program PIC is using C and the compiler is PCW C compiler. The program for controlling the pulse is very short and just about half page. It is short because the project is open loop and the output is fixed, so the microcontroller does not have external input to be fed on. The other factor is the switching technique used for this project. The switching technique used for this project is just normal PWM and not SPWM (sine PWM). For the normal PWM, the programming is just about controlling period and ON time ( $t_{on}$ ).

Figure 3.7: Desired output pulses

Figure 3.7 is the desired output pulses. The program is made based on pulses on Figure 3.6. For the pulse of PIN\_C1 (the upper pulse on Figure 3.6), the time delay is 2.5 ms and for pulse of PIN\_C2 (the bottom pulse on Figure 3.6), the time delay is 12.5 ms. The period of both pulse is 20 ms, so the frequency generated is 50Hz. The pulse width of both pulses is 5 ms because the desired Duty cycle is 25%. The duty cycle can be calculated based on equation 3.1 below:

$$Duty \ Cycle, \% = \frac{t_{on}}{Period} \times 100 \tag{3.1}$$

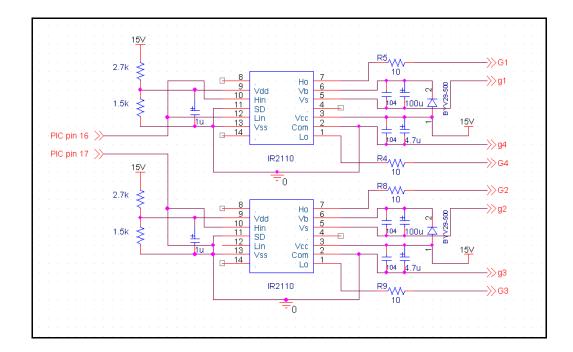

Figure 3.8: IR2110 MOSFET driver circuit

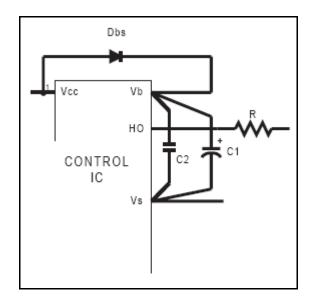

The IR2110 MOSFET gate driver chips play two vital roles in creating drive pulses suitable for operation of a full-bridge inverter circuit. First of all, the IR2110's amplify the 5-volt logic signals output by the microcontroller to obtain a 15 volt signal necessary to fully turn on the gate of the full-bridge circuit. A gate drive pulse of less than 10 volts could result in excessive heating which occurs when the MOSFET is driven are operating in the linear mode of operation, which by the physical MOSFET construction, happens to be the most resistive regions of operation.

The other role played by the IR2110 chips is to provide electrical isolation between the upper control pulses and the upper gate of the full-bridge inverter circuit. Electrical isolation is extremely important in biasing the upper full-bridge gate with the appropriate drive signal voltages. Without proper electrical isolation, the upper gate would be considered "floating". In other words, the upper full-bridge MOSFETs would have a gate-to-source voltage ranging from 0 VDC to 340 VDC because they are not directly referenced to ground potential.

The IR2110 gate driver chips provide electrical isolation by inserting a capacitor and diode, also known as a "bootstrap supply", are shown in Figure 3.9 below. When Vs is pulled down to ground (either through the low side FET or the load, depending on the circuit configuration), the bootstrap capacitor (Cbs) charges through the bootstrap diode (Dbs) from the 15 Vcc supply. This provides a supply to Vbs.

Figure 3.9: Bootstrap diode/capacitor circuit used with IR 2110 control IC's

#### **3.3.3.1** Calculating the Bootstrap Capacitor Value

The following equation gives the minimum charge which needs to be supplied by the capacitor:

$$Q_{bs} = 2Q_g + \frac{I_{qbs(max)}}{f} + Q + \frac{I_{cbs(leak)}}{f}$$

(3.2)

$Q_g$  = Gate charge of high side FET (refer to IRFP450 datasheet)

f = frequency of operation

$I_{cbs(leak)}$  = Bootstrap capacitor leakage current (neglected if using ceramic capacitor)

$Q_{ls}$  = level shift charge required per cycle = 5nC (500V/600V IC's) or 20nC (1200V IC's) or 20nC (1200V IC's)

$$Q_{bs} = 2(75n) + \frac{230u}{50} + 5n + \frac{0}{50}$$

$$= 4.755uC$$

The bootstrap capacitor must be able to supply the charge given by equation 3.2 and retain its full voltage. Otherwise, there will be a significant amount of ripple on the Vbs voltage which could cause the Ho output to stop functioning. Therefore, the charge in the Cbs capacitor must be a minimum of twice the value given by equation 3.2. The minimum capacitor value can be calculated from the equation 3.3 below:

$$C \ge \frac{2[Q_{bs}]}{V_{cc} - V_f - V_{LS} - V_{min}}$$

(3.3)

Where:

$V_f$  = Forward voltage drop across the bootstrap diode (refer to BYV29-500 datasheet)  $V_{LS}$  = Voltage drop across the low side FET (V<sub>SD</sub> in IRFP450 datasheet)  $V_{Min}$  = Minimum voltage between V<sub>B</sub> and V<sub>S</sub> (minimum V<sub>BSUV</sub> in IR2110 datasheet)

$$C \ge \frac{2[4.755u]}{15 - 1 - 1.4 - 7}$$

$\geq$  1.698uF

The  $C_{bs}$  Capacitor value obtained from the above equation above is the absolute minimum required, however due to the nature of the bootstrap circuit operation, a low value capacitor can lead to overcharging, which could in turn damage the IC. Therefore to minimize the risk of overcharging and further reduce ripple on the V<sub>bs</sub> voltage the C<sub>bs</sub> value obtained from the above equation should be should be multiplied by a factor of 15 (rule of thumb).  $C_{new} \ge 1.698 uF \times 15$   $\ge 25.47 uF$  $\ge 47 uF$  (nearest available value)

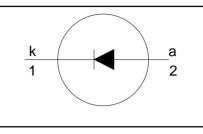

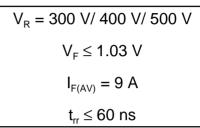

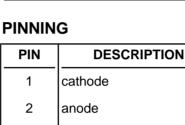

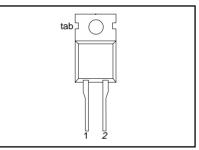

#### **3.3.3.2** Selecting the Bootstrap Diode

The bootstrap diode  $(D_{bs})$  needs to be able to block the full power rail voltage, which is seen when the high side device is switched on. It must be a fast recovery device to minimize the amount of charge fed back from the bootstrap capacitor into the V<sub>cc</sub> supply, and similarly the high temperature reverse leakage current would be important if the capacitor has to store charge for long periods of time.

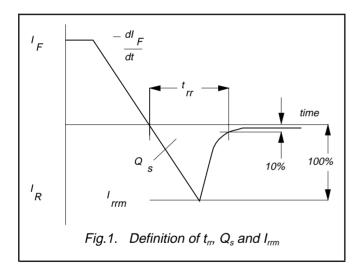

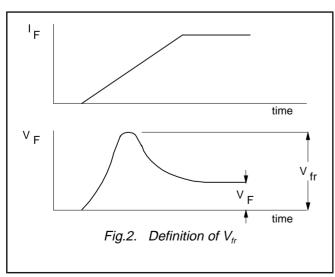

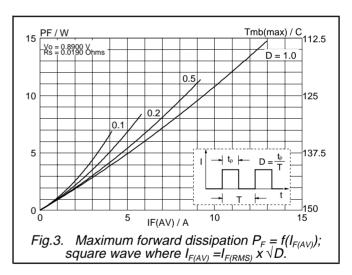

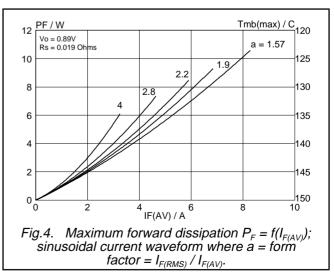

Therefore: Diode Characteristics  $V_{RRM}$  = Power rail voltage  $\geq 400 \text{ V}$ Chosen diode (BYV29-500);  $V_{RRM}$  = 500 V Maximum  $t_{rr}$  = 100 ns  $\leq 100 \text{ ns}$ Chosen diode (BYV29-500);  $t_{rr} \leq 60 \text{ ns}$   $I_F = Q_{bs} \text{ x f}$ = 4.755uC × 50Hz = 0.238 mA Chosen diode (BYV29-500);  $I_F$  = 9A

#### 3.3.3.3 IR2110 Circuit Layout Considerations

For the layout of IR2110 circuit, the bootstrap capacitor is placed closed to the pins of the IC (as shown in Figure 3.10). At least one low ESR capacitor should be used to provide good local decoupling. If an aluminium electrolytic capacitor is used for the bootstap capacitor, a separate ceramic capacitor need to be placed close to the IC. If the bootstap capacitor is a ceramic or tantalum type, the capacitor alone should be sufficient as the local decoupling.

Figure 3.10: Recommended layout of the Bootstrap Components

### 3.3.4 Inverter Design

There are 3 main type of inverter in the market today. The most simple and cheapest type is square wave inverter, the improved version of square wave inverter is a modified square wave inverter, the best and most expensive type is true sine wave inverter. The type chosen for this project is the common type used in the market that is modified square wave inverter.

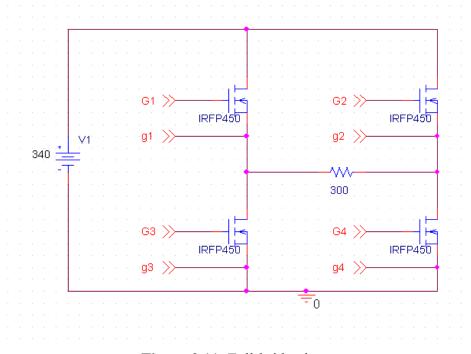

The full-bridge inverter used for this project is very simple to construct because it only consists 4 switches, as shown in Figure 3.11. The function of the full-bridge inverter is to convert 340 VDC from supply into 240Vrms, 50 Hz. The gate chosen for the full-bridge inverter circuit were the IRFP450's. The IRFP450 MOSFET were chosen because they have appropriate voltage and current ratings ( $V_{DS max} = 500V$ ,  $I_{D max} = 14A$ ).

Figure 3.11: Full-bridge inverter

The two PWM pulses produced by the microcontroller circuit are fed into the full-bridge inverter. One signal is sent in parallel to MOSFET gate G1 and G4. The other signal is sent in parallel to MOSFET gate G2 and G3. The signal programmed in the microcontroller will allow for MOSFET gate G1 and G4 to be ON while MOSFET gate G2 and G3 are OFF, and vice versa.

The load chosen for this inverter is resistive load lamp that has resistivity of  $300\Omega$ . The power draw from this load when supplied with full voltage (240Vrms) can be calculated by using equation 3.4 below:

$$P = IV$$

(3.4)

$$= \frac{V^2}{R}$$

$$= \frac{240^2}{300}$$

The value above is not the maximum output power for this inverter because the design inverter can sustain up to 14A maximum current in normal heat condition  $(T_c=25^\circ)$  and 8.7A in worst heat condition  $(T_c=100^\circ)$ . So, the maximum power in theory can be calculated by using equation below:

$$P = IV$$

=  $\frac{14A}{\sqrt{2}} \times 240V$

= 2375W (in normal heat condition)

Or

=  $\frac{8.7A}{\sqrt{2}} \times 240V$

= 192W

= 1476W (in worst heat condition)

The actual value of power that can be sustained by the design inverter may not up to 1476W practically, but it surely can sustain up to 500W.

### 3.3.4.1 Low-Pass Filter

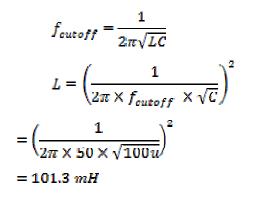

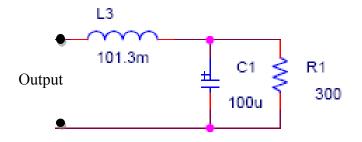

Low-pass filter can result a great reduction of the inverter output harmonics and hence provide clean power for the load. The filter is inserted after the output of fullbridge inverter in order to eliminate any frequency higher than cutoff frequency. The cutoff frequency can be calculated by using following formula:

$$f_{cutoff} = \frac{1}{2\pi\sqrt{LC}}$$

(3.5)

The switching frequency used in this project is 50 Hz and from the equation above, either L (inductor) or C (capacitor) can be set as a constant. In order to make it easier, capacitor been selected as a constant because the inductor will be custom made in either way. By using 100uF for the capacitor value and using formula in equation 3.5 above, the inductor value been calculated.

Figure 3.12: L-C low-pass filter schematic

The Figure 3.12 shown is the configuration of L-C filter. The capacitor is placed parallel with load and the inductor is placed series with capacitor and load.

### **CHAPTER 4**

#### **RESULT AND ANALYSIS**

### 4.1 Introduction

This chapter will show the result and analysis of the Inverter. The comparison between hardware result and simulation by using Orcad Pspice 9.1 will be analyzed. The measurement of hardware output is using oscilloscope. The analysis is divided into 4 parts:

- i. Power supply output voltages

- ii. Microcontroller output pulses

- iii. MOSFET driver output pulses

- iv. Analysis of Inverter output

### 4.2 Power Supply Circuit Output Voltages

The analysis of supply voltage is important to ensure the voltage is not exceeding the required value. Electronic component such as PIC just need 5V to operate. If the component is supplied with high voltage, the component will be hot and in some cases it can blow. The other factor need to be considered is voltage ripple. The ripple will bring effect to generated pulses and it will make the output of the inverter not smooth.

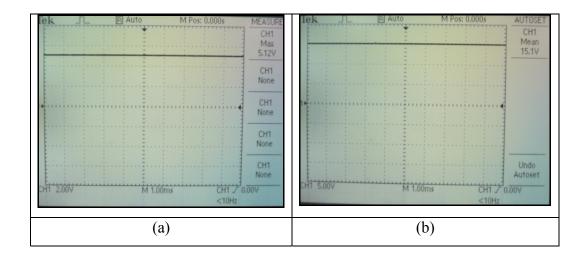

Figure 4.1: Power supply output voltage (a) output1 (b) output2

The Figure 4.1(a) and 4.1(b) is the output of power supply. From the figure we can see that the output is very smooth and the voltage is near to the desired value. The voltage magnitude of the power supply output is show at Table 4.1.

|          | Design constrain | Supply output |

|----------|------------------|---------------|

| Output 1 | 5V               | 5.12V         |

| Output 2 | 15V              | 15.1V         |

Table 4.1:

Supply output versus design constrain

## 4.3 Microcontroller Output Pulses

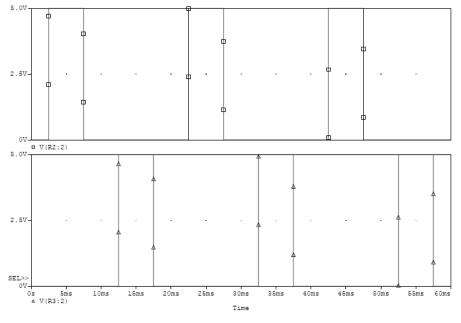

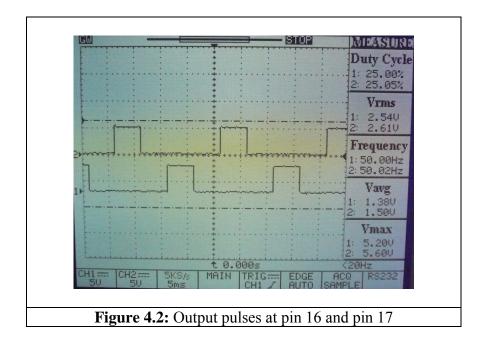

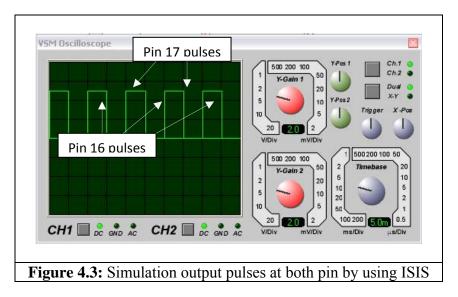

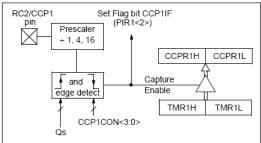

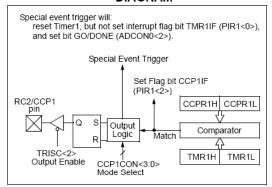

The PWM pulses needed to drive MOSFETs driver is generated by PIC microcontroller through programming. The output pin is set at pin 16 (C1) and pin 17 (C2) and the pulses have 15 ms delay with each other. The maximum voltage of the output pulses is same as the voltage supplied to the PIC that is in 5V voltage range.

From the observation at oscilloscope output, the ON pulse width and OFF pulse width of the hardware and simulation is similar. The ON pulse width is 5 ms, the OFF pulse width is 15 ms and the frequency of the pulses is 50 Hz. The output of PIC is same as the desired output and can be used to drive MOSFETs driver. The comparisons between designs constrain and microcontroller output can be seen at Table 4.2.

Table 4.2: Comparisons between designs constrain and microcontroller output

|            | Design constrain | Pin 16 output | Pin 17 output |

|------------|------------------|---------------|---------------|

| Vmax       | 5V               | 5.2V          | 5.6V          |

| Frequency  | 50 Hz            | 50 Hz         | 50.02 Hz      |

| Duty Cycle | 25%              | 25%           | 25.05%        |

| PCW C Compiler IDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Eile <u>Project</u> <u>E</u> dit <u>O</u> ptions <u>C</u> ompile <u>View</u> <u>T</u> ools <u>D</u> ebug <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| 🎌 🖙 🔲 🖬 🖆 🗊 📇 🛛 Microchip 14 bit 🔄 🖬 📽 🧃                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

| v 웨립 🕼 🐴 🚼 🕨 🤃 🔚 🛛 🔳 트 🔍 🐵                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 🔥 🗌 🕡 🗌 |

| ariff2.c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| <pre>#include &lt;16f877.h&gt; //type of pic #fuses hs,nowdt,noprotect,brownout,nolvp #use delay(clock=20000000) //crystal clock #byte portc=7 void main()</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| <pre>{     set_tris_c(0); // initialize port c     do{         delay_us(2500); // 2.5ms time delay         output_high(PIN_C1); // HIGH output at PIN_C1 (pin 17)         delay_ms(5); // pulse width of PIN_C1 (pin 17)         output_lou(PIN_C1); // LOW output at PIN_C2 (pin 16)         delay_ms(5); // delay between pulse C1 and C2         output_high(PIN_C2); // HIGH output at PIN_C2 (pin 16)         delay_ms(5); // DUSe width of PIN_C2 (pin 16)         output_lou(PIN_C2); // LOW output at PIN_C2 (pin 16)         output_lou(PIN_C2); // LOW output at PIN_C2 (pin 16)         output_lou(PIN_C2); // delay before loop[         //while(1);     } </pre> |         |

| <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

Figure 4.4: Program used to generated pulses

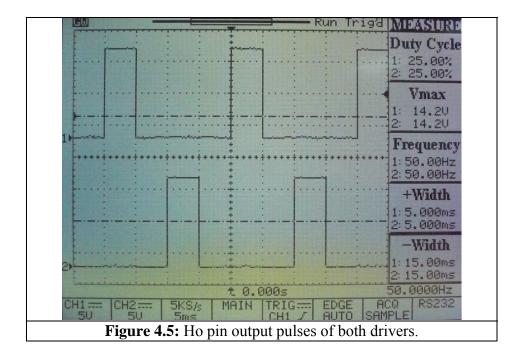

## 4.4 MOSFET Driver Output Pulses

The minimum voltage need to fully turn on MOSFET is 10V, so the drivers need to be supply with voltage larger than 10 V. For this project, the voltage supplied to the  $V_{cc}$  input of IR2110 is 15V. The IR2110 will receive pulses from PIC and then convert it to the voltage based on  $V_{cc}$  input (in this case 15V). The output of IR2110 is shown at Figure 4.5.

Figure 4.5 shows the result from Ho pin of IR2110. The result of both drivers is same except there is 5ms delay between pulse of driver1 and driver2. The  $V_{max}$  on the oscilloscope shows a few drops in voltage because there is a voltage drop across bootstrap diode. The voltage magnitude at Lo pin of both IR2110 is near to  $V_{cc}$  value because the voltage output of Lo pin is using the voltage supplied to  $V_{cc}$ . The result is as desired value and the voltage magnitude (14.2V) is enough to fully turn on MOSFET.

The result from PSpice simulation is shown in Figure 4.6. The pulses from simulation can be considered ideal because the simulation not considering other disturbance factor such as noise, heat and loss. The voltage magnitude for PSpice simulation is different with the real output value because the pulses is generated by using VPULSE and the gate for the full-bridge is using ideal switch. The table that listed all driver output is shown below:

| Table 4.3: IR2110 MOSFET di | river output |

|-----------------------------|--------------|

|-----------------------------|--------------|

|                  | Design    | Но      | Но      | Lo      | Lo      |

|------------------|-----------|---------|---------|---------|---------|

|                  | constrain | Driver1 | Driver2 | Driver1 | Driver2 |

| V <sub>max</sub> | >10V      | 14.2V   | 14.2V   | 15.1V   | 15.1V   |

| Frequency        | 50 Hz     | 50 Hz   | 50 Hz   | 50 Hz   | 50 Hz   |

| Duty Cycle       | 25%       | 25%     | 25 %    | 25 %    | 25 %    |

#### 4.5 Analysis of Inverter Output

This part will show the result and analysis of the Inverter. Before fabricating the hardware, the analysis is done using Orcad Pspice 9.1 After the hardware is finalized, the inverter circuit will be analyzed using oscilloscope.

#### 4.5.1 Analysis of Voltage, Current, and Power Relation with Load

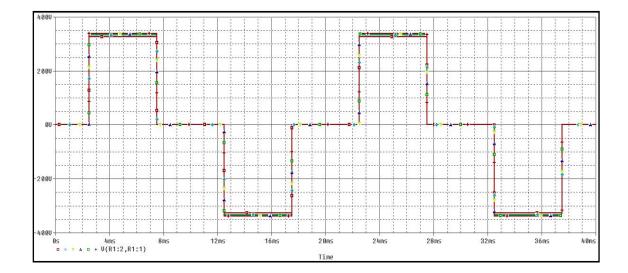

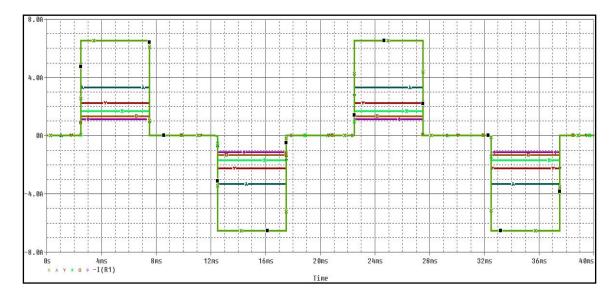

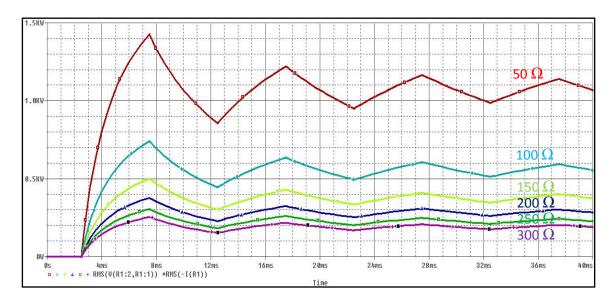

For this analysis, the load resistance value for the inverter is changed. The minimum resistance value set is 50  $\Omega$ , with 50 increments and the maximum value is 300  $\Omega$ . The total reading is 6 and the parameters taken are voltage, current and power. The result for the parameter is on Figure 4.7, 4.8 and 4.9.

Figure 4.7: The output voltage of different load

Figure 4.8: The output current with different load

Figure 4.9: The output power with different load

All the result for Figure 4.7, 4.8 and 4.9 is compress into Table 4.4. The Table 4.4 below lists the values of voltage, current and power when the load is changed.

| Load (Ω)              | 50     | 100    | 150    | 200    | 250    | 300    |

|-----------------------|--------|--------|--------|--------|--------|--------|

| V <sub>peak</sub> (V) | 326.92 | 333.33 | 335.53 | 336.63 | 337.3  | 337.75 |

| $V_{RMS}(V)$          | 231.27 | 235.8  | 237.36 | 238.14 | 238.61 | 238.93 |

| I <sub>peak</sub> (A) | 6.54   | 3.33   | 2.24   | 1.68   | 1.35   | 1.13   |

| $I_{RMS}(A)$          | 4.62   | 2.36   | 1.58   | 1.19   | 0.95   | 0.8    |

| Power<br>(W)          | 1067.8 | 555.03 | 374.9  | 283.04 | 227.33 | 189.94 |

Table 4.4: Voltage, current and power value based on the load resistance

From Table 4.4, the changes in load will affect the value of voltage, current and power. The lower value of resistance, the higher current will flow through the load and the higher power at the load. This is because the value of voltage is same. The relation between current, resistance and power can be seen on equation below:

| P = IV      | (4.1) |

|-------------|-------|

| = I(IR)     |       |

| $P = I^2 R$ | (4.2) |

#### 4.5.2 Analysis of Total Harmonic Distortion (THD)

For this analysis, the THD for three type of inverter is compared. The first type is modified square wave inverter used for this project and the second one is modified square wave inverter with filter. The THD of the current is computed using truncated Fourier series and it's based on frequency spectrum. The equation used for the calculation is as below:

$$THD_{I} = \frac{\sqrt{\sum_{n=2}^{\infty} (I_{n,rms})^{2}}}{I_{Irms}}$$

(4.3)

The figure of frequency spectrum for all three type of inverter is on figure below:

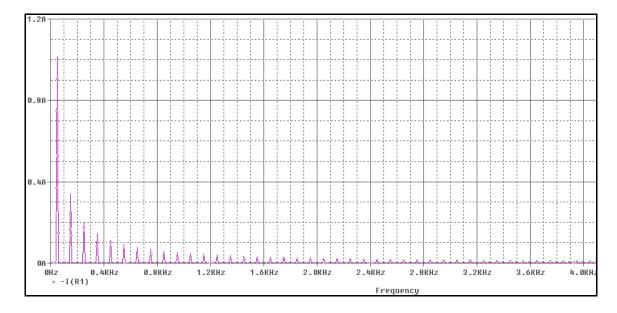

Figure 4.10: Frequency spectrum of modified square wave inverter (without filter)

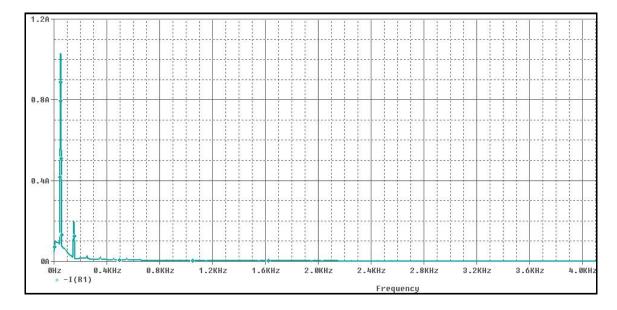

Figure 4.11: Frequency spectrum of modified square wave inverter with filter

The configuration of all three inverter is defined on table below:

|                        | Modified square | Modified square  |

|------------------------|-----------------|------------------|

|                        | wave            | wave with filter |

| Vin (DC)               | 340 V           | 340 V            |

| f                      | 50 Hz           | 50 Hz            |

| Filter capacitor value | -               | 100 uF           |

| Filter inductor value  | -               | 101.3 mH         |

Table 4.5: Inverters configuration

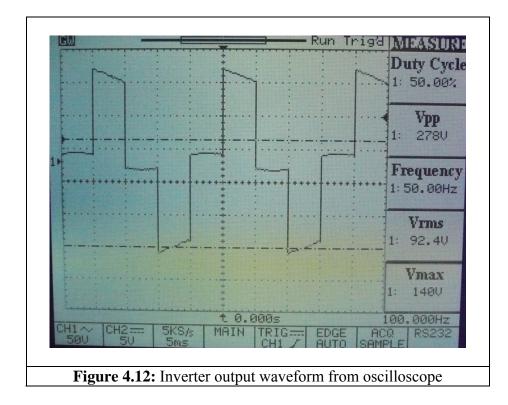

The value from the frequency spectrum Figure 4.11 is inserted into Table 4.6 and the value from the frequency spectrum Figure 4.12 is inserted into Table 4.7. All value inside the table is calculated using Microsoft Office Excel.

| Table 4.6: Modified square v | wave inverter data | from frequency spectrum |

|------------------------------|--------------------|-------------------------|

|                              |                    |                         |

| n                 | Frequency  | In       | $\sqrt{2}$ | In $/\sqrt{2}$ | $(\ln /\sqrt{2})^2$ |